Cadence仿真流程详解与设置

需积分: 16 191 浏览量

更新于2024-08-02

收藏 465KB PDF 举报

"Cadence 仿真流程"

Cadence 仿真流程是电子设计自动化(EDA)领域中的一个重要环节,主要用于验证和优化集成电路(IC)和印刷电路板(PCB)设计的性能。Cadence 提供了一整套工具来支持这一流程,其中Allegro是PCB设计的主要平台,而SpecctraQuest和SigXplore则是关键的仿真工具。以下是对Cadence仿真流程的详细说明:

1. 准备Allegro PCB设计:首先,需要在Allegro环境中创建或导入已完成的PCB设计。设计应包含所有元件布局、布线以及电气连接。

2. 库转换和模型加载:将所需的器件模型(如IBIS模型)从库中转换为dm格式,并加载到仿真环境中。这确保了仿真能够准确地反映实际电路的行为。

3. 定义电源和地:设置设计中的电源电压和接地网络,这对于电源完整性(PI)和信号完整性(SI)仿真至关重要。

4. 调整PCB叠层:根据设计需求调整PCB的层叠结构,以满足阻抗控制和其他电气性能要求。

5. 设置仿真参数:配置仿真环境,包括选择合适的仿真器、设置时间步长、精度等参数,确保仿真能够准确且高效地运行。

6. 选择仿真信号:使用探针(Probe)工具选取需要分析的信号线,这些信号将是仿真关注的重点。

7. 生成仿真报告:定义报告参数,包括频率范围、眼图、时序分析等,以获取详尽的仿真结果。

8. 电路拓扑提取:如果从其他工具导入设计,可能需要提取电路的拓扑结构,以便于在Cadence环境中进行仿真。

9. 多条件仿真:根据设计的不同条件或场景,多次运行仿真,以全面评估设计的性能。

10. 结果分析:对仿真结果进行深入分析,检查信号质量、时序裕量、噪声和干扰等指标,以确定是否满足设计规范。

11. 电气约束规则定义:在仿真过程中,需要定义和检查电气约束规则,如最大电流、电压摆幅等,确保设计符合安全和功能要求。

12. 结束与优化:根据仿真结果,可能需要返回到设计阶段,进行修改和优化,然后再重复仿真流程,直到设计满足所有性能标准。

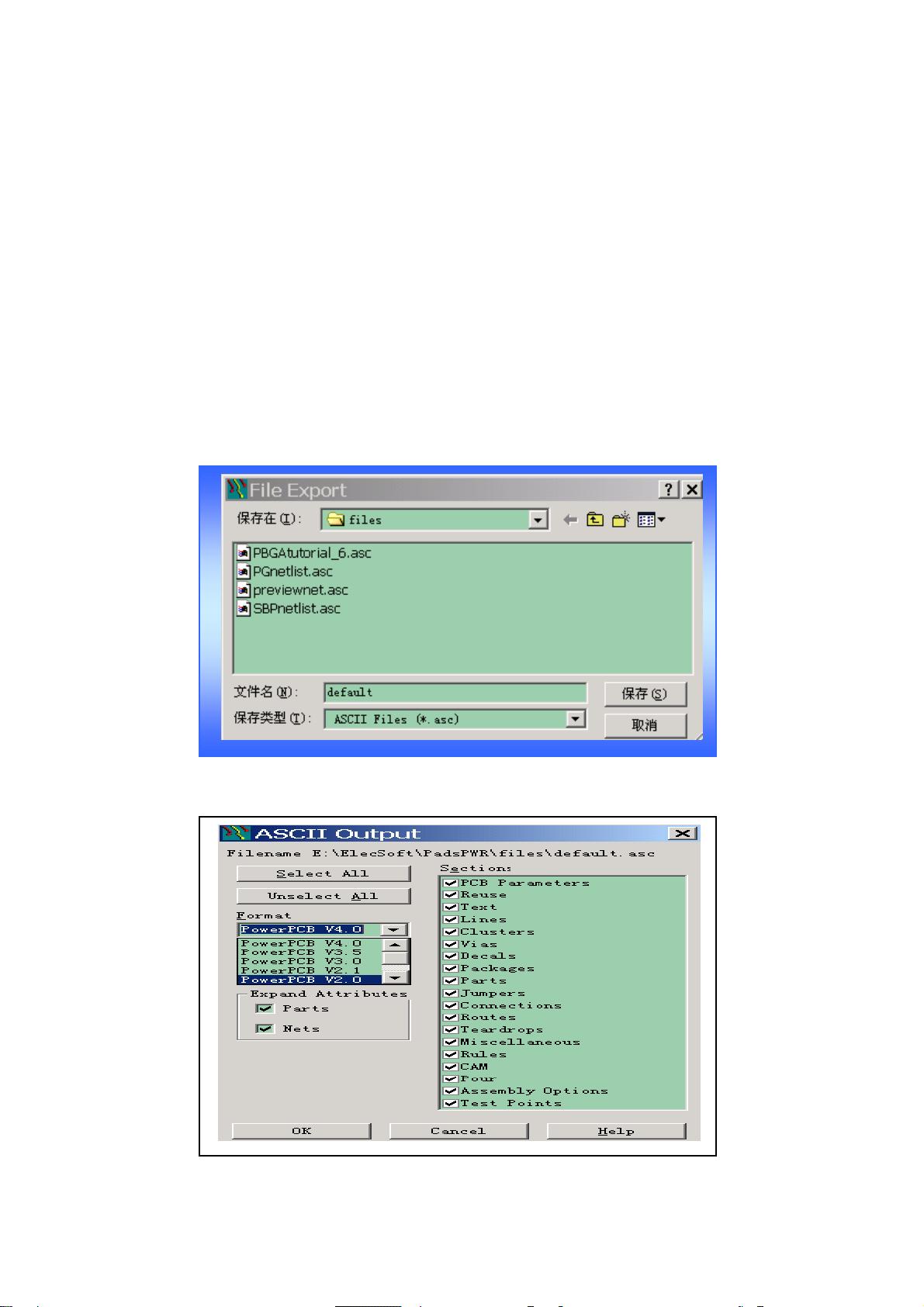

在从PowerPCB转换到Allegro的流程中,需要将PowerPCB的设计导出为ASCII格式的*.asc文件,然后在Allegro中导入,确保所有必要的选项(如Parts和Nets)被选中,且文件格式兼容。导入后,Allegro将生成一个新的PCB设计文件,可以在此基础上进行SI仿真。

Cadence 仿真流程是一个迭代的过程,涉及多个工具和步骤,其目的是确保电子设计在实际应用中的性能和可靠性。通过精细的设置和分析,设计师可以发现并解决潜在的问题,从而提高产品的质量和市场竞争力。

点击了解资源详情

150 浏览量

点击了解资源详情

141 浏览量

181 浏览量

117 浏览量

181 浏览量

点击了解资源详情

xiaowa328

- 粉丝: 0

- 资源: 4

最新资源

- An Integration Research on Service-oriented

- 3D Game Engine Architecture

- IPv6_Ready_DHCP_Interop.pdf

- PureMvc 实现 术语阐述及最佳实践

- IPsec_1_8_1.pdf

- sqlplus操作大全

- 01[1].WebLogic部署应用程序(图解).doc

- 知名企业实际面试数据库类题目及答案

- 在Linux世界驰骋系列全集.pdf

- IBM_-_Using_Ajax_with_PHP_and_Sajax.pdf

- Java Servlet Programming

- 数据库试验SQL 语句参考

- H263协议的中文版文档

- 用vb读取excel中的数据

- 易达oa办公自动化系统解决方案

- myeclipse6 java 中文开发教程