MAX+plusII VHDL快速入门与使用指南

需积分: 8 73 浏览量

更新于2024-07-31

收藏 1.44MB PPT 举报

"这篇文档是关于如何使用maxplusII进行VHDL设计的入门指南,主要介绍了maxplusII的基本操作流程,包括创建源程序、编译、仿真、下载到硬件等步骤,并提到了其他常见的VHDL开发工具,如isplever、QuartusII、ISE、ModelSim等。"

在VHDL设计中,maxplusII是一款由Altera公司提供的集成开发环境,适用于FPGA和CPLD的设计与开发。这个工具不仅支持编译和调试,还提供了仿真功能,使得设计者可以在硬件实现之前验证逻辑设计的正确性。尽管maxplusII在功能上可能不如其他现代工具如QuartusII或ISE强大,但它因其易于学习和使用而受到初学者的欢迎。

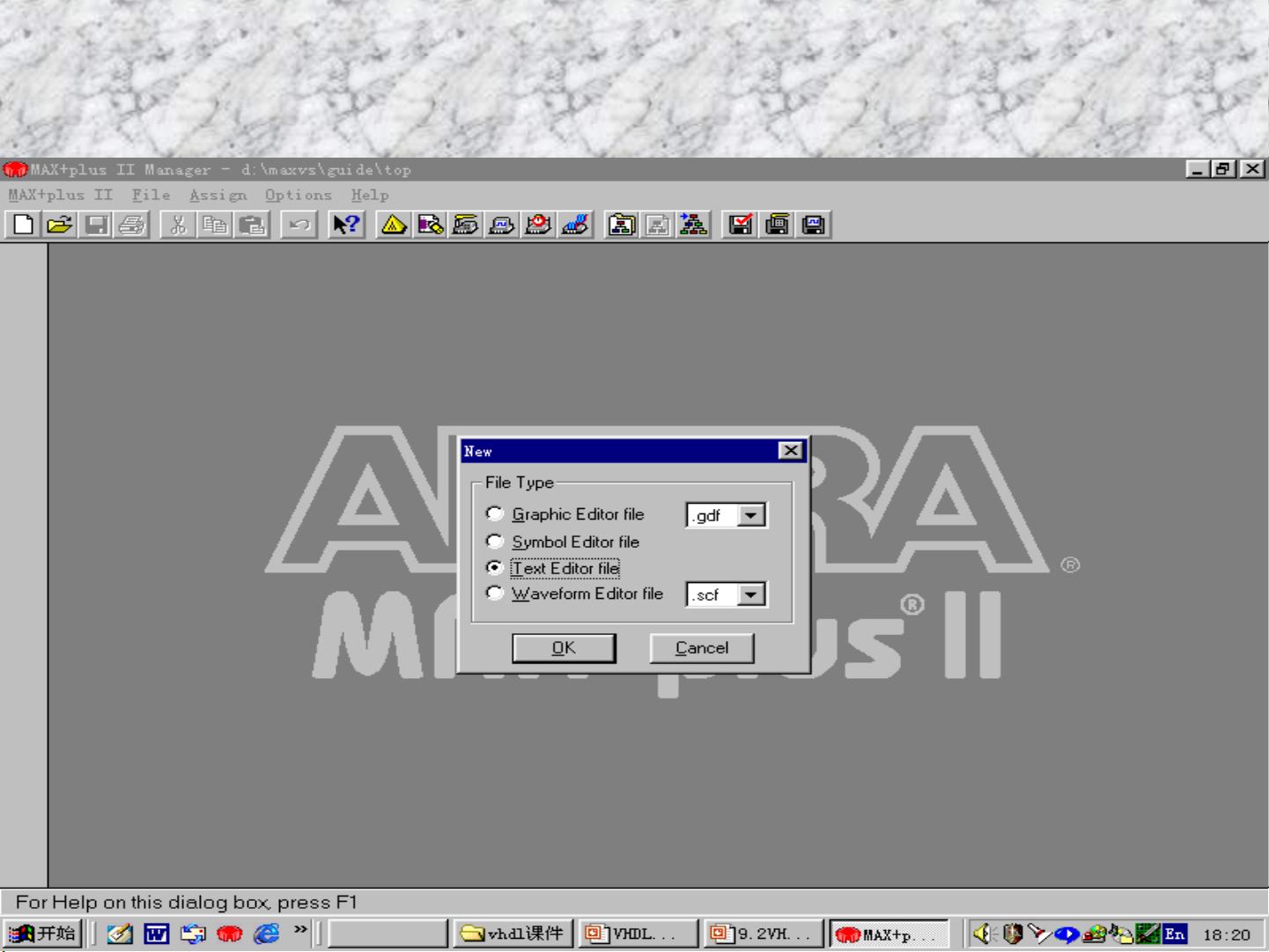

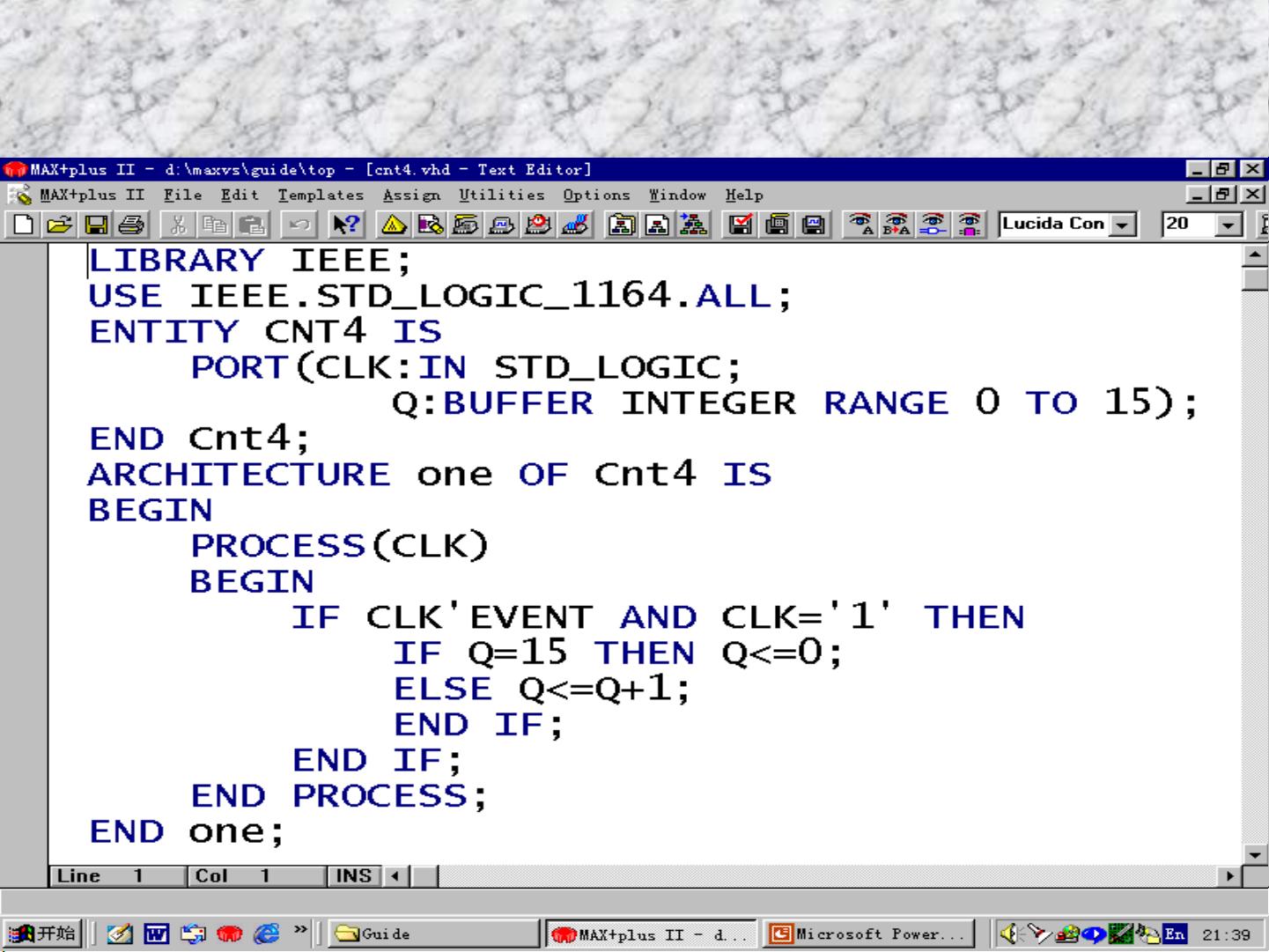

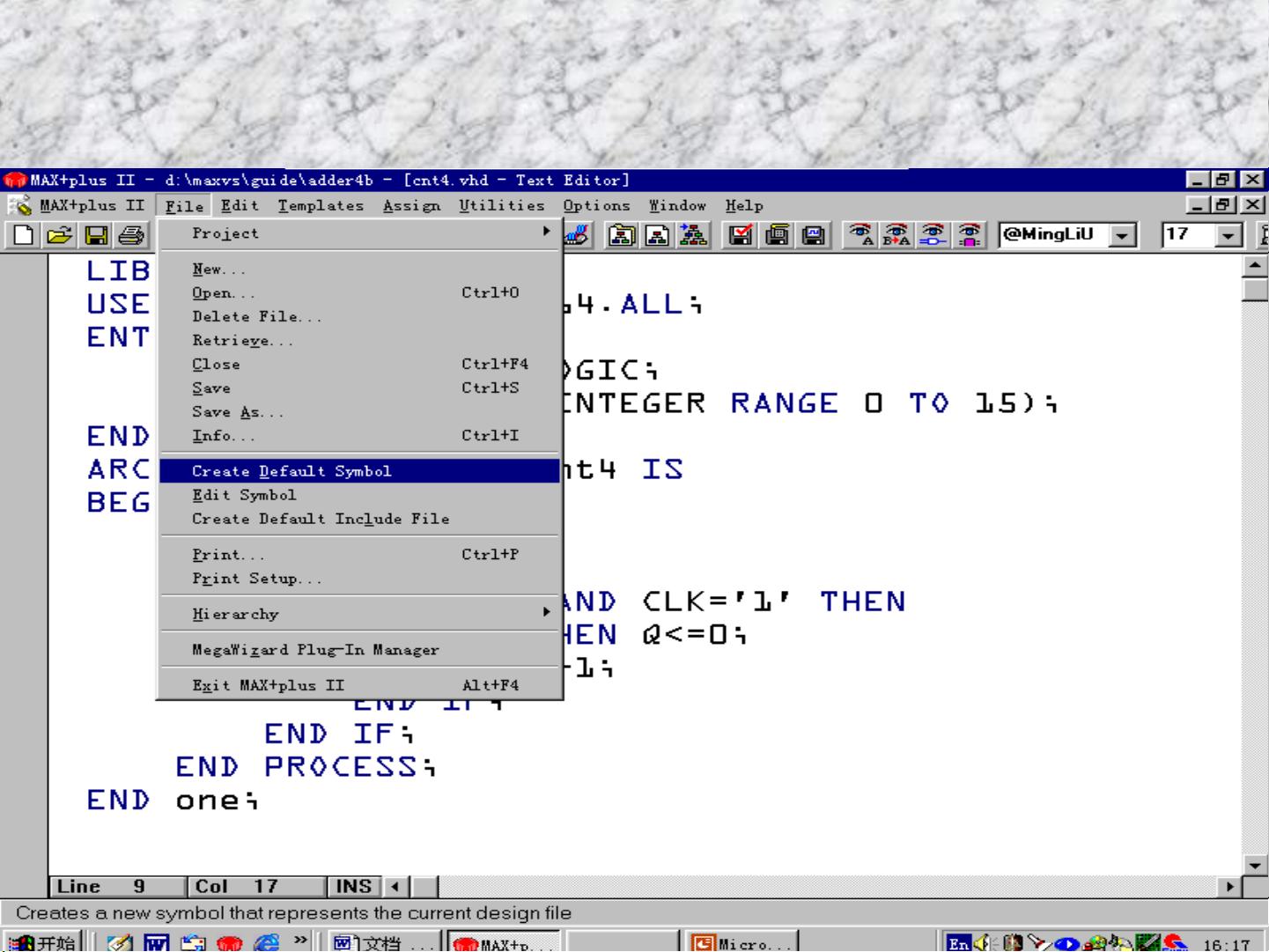

创建源程序是VHDL设计的第一步。在maxplusII中,设计者可以通过"File" -> "New" -> "TextEditorFile"来创建新的VHDL源代码文件,例如,创建一个名为Cnt4.vhd的四位二进制计数器和Decl7s.vhd的七段数码显示译码器。编辑源代码后,用户可以生成设计元件的图形符号,这有助于在顶层设计中直观地表示各个模块。

接下来,通过"File" -> "New" -> "GraphicEditorFile"创建顶层设计文件,如TOP.GDF,这将包含所有子模块的连接。在图形编辑器中,用户可以拖拽元件符号并连接它们的输入和输出,以构建完整的系统结构。

编译顶层设计文件是确保设计符合硬件约束和逻辑正确性的关键步骤。在maxplusII中,编译会检查语法错误和逻辑错误,并生成可编程设备的配置文件。如果编译无误,可以进行仿真,这通常通过"Simulation"菜单进行,以测试设计在不同输入条件下的行为。

在确认设计满足需求后,可以将配置文件下载到实际的FPGA硬件上,进行硬件调试。maxplusII提供了下载功能,允许设计者在真实环境中验证其设计。

此外,文档还提及了其他一些工具,如Lattice的isplever、Xilinx的ISE和Synplicity的SynplifyPro,它们分别用于不同的开发阶段,如综合和仿真。Mentor公司的ModelSim是一个常用的独立仿真工具,而Aldec的ActiveHDL和Cadence的NC系列工具则提供了更多的仿真选项。

maxplusII是VHDL设计者入门的一个良好起点,它提供了一站式的解决方案,覆盖了从源代码编写到硬件实现的整个设计流程。虽然现代工具可能提供了更多高级特性,但maxplusII的简洁易用性使其在教学和简单项目中仍然具有价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

175 浏览量

2012-11-29 上传

235 浏览量

2021-09-30 上传

167 浏览量

143 浏览量

AICZY

- 粉丝: 0

- 资源: 1

最新资源

- docs-to-pdf-converter

- RedisDesktopManager安装包

- springcloud-config

- :parrot:会话标准元语言-Rust开发

- 行业文档-设计装置-防震纸质包装盒.zip

- testrepo

- company_employee_mysql

- Intel ME Firmware Repository

- 行业文档-设计装置-一种平台拖车.zip

- HTML-CSS:基础HTML和CSS知识

- 基于远程监督与bootstrapping方法的人物关系抽取,基于知识图谱的知识问答

- 全球地址表,包括所有国家,地区,城市。mysql版,.sql文件

- 一个易于安装,高性能,零维护的代理,可运行加密的DNS服务器。-Rust开发

- 塔勒3_01_02_2021

- Network_Programing_2021

- 基于apache commons.fileupload的文件上传组件,改进了上传速度