Jeson的Verilog与Vivado学习日志

需积分: 5 46 浏览量

更新于2024-08-05

收藏 779KB DOCX 举报

Jeson的工作日志,记录了他在IT行业的学习和实践经验,主要涉及FPGA相关的知识和技术,包括软件安装、基础理论回顾、硬件设备操作、编程语言理解、IP核应用、时序逻辑分析以及问题排查等。

在Jeson的工作日志中,他首先进行了办公软件的安装和基础知识的回顾,这可能是为了确保他具备必要的计算机操作和理论基础。接着,他开始深入学习FPGA相关技术,如流水灯的点亮,这是FPGA入门的经典实验,用于熟悉硬件编程和逻辑控制。

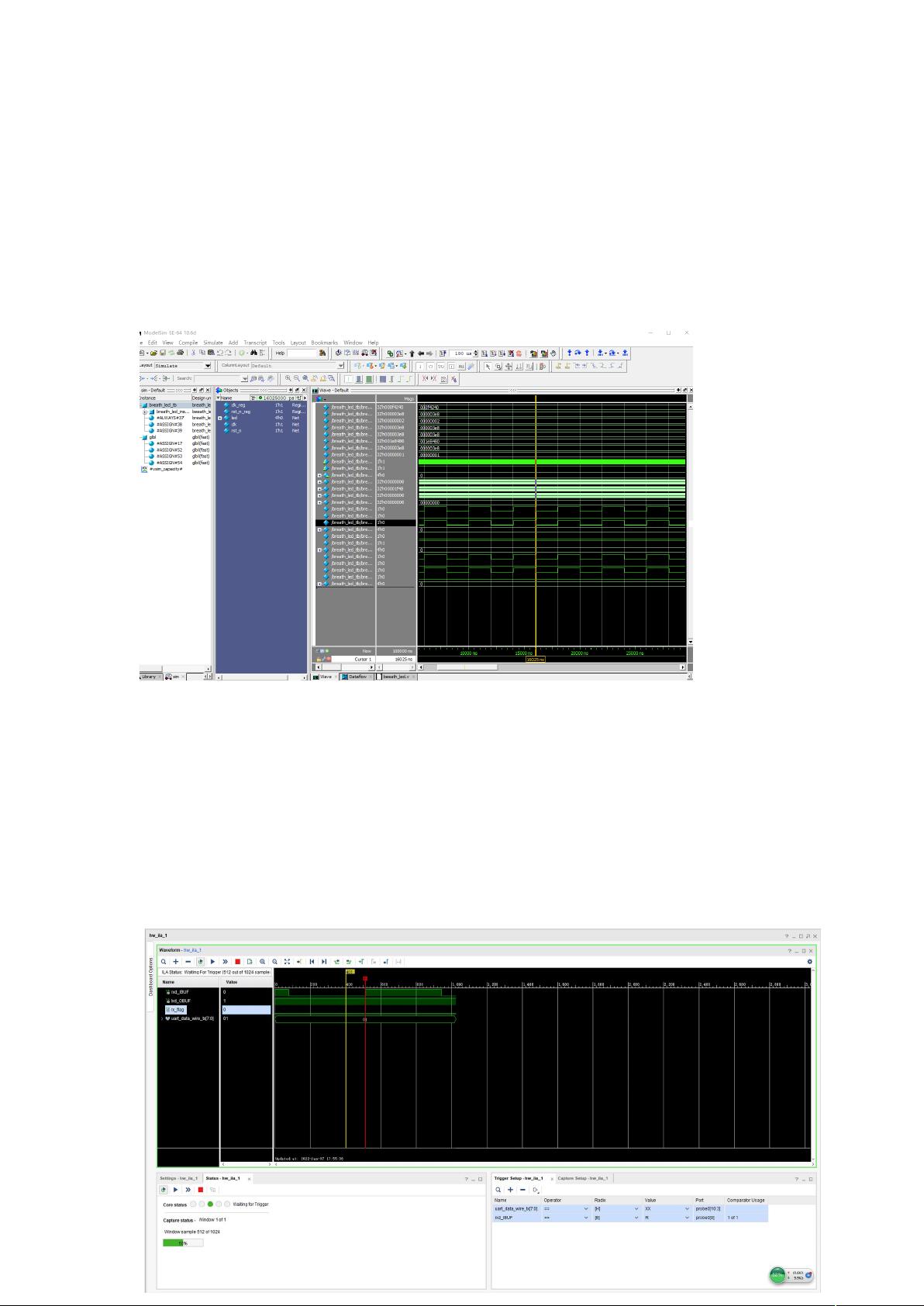

在2022年1月5日,Jeson回顾了Verilog HDL语言,这是FPGA设计的常用硬件描述语言。他还学习了Vivado工具的使用,包括代码编写、综合、管脚绑定和程序烧录,同时使用Modelsim进行联合仿真,这有助于验证设计的正确性。他还接触了呼吸灯的代码,了解了更复杂的定时和控制逻辑。

在后续几天,Jeson逐渐熟悉了VSC编程软件,并开始使用不同的IP核,如FLASH、FIFO和PLL,这些都是FPGA设计中常见的组件。他认识到理解和运用IP核对于提升设计效率至关重要。同时,他对串口通信进行了深入研究,了解了ILA(In-System Logic Analyzer)IP核,这是一种强大的数据捕获工具,帮助检测系统中的数据变化。

在1月10日,Jeson成功编写了通过串口控制LED状态的程序,并掌握了ILA抓取程序数据的新技能,同时继续深化对Vivado的使用。他也遇到了因不熟悉ISE导致的芯片选型错误,这提醒我们在设计时必须精确选择合适的硬件平台。

接下来的几天,Jeson专注于AD9552数据手册的学习,掌握了其传输协议和寄存器功能。他遇到并解决了管脚绑定错误(ERROR:Place:1108),并认识到无源晶振在某些情况下可能无法用示波器测量。他还讨论了时序逻辑的严谨性,强调了时序协议最好用状态机描述,避免使用标志位可能导致的问题。此外,他强调了解决问题需要逐步排查,通过成熟代码判断硬件问题。

最后,Jeson继续深化串口程序的应用,并进一步理解了FIFO的读写操作及其full与empty标志位,这些都是在处理实时数据流时的关键概念。

总结来看,Jeson的工作日志涵盖了FPGA开发的多个关键环节,从基础理论到实际操作,再到问题解决,充分展示了他在FPGA领域的学习和进步。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-03-20 上传

2021-04-28 上传

2021-04-06 上传

2021-05-18 上传

2024-05-18 上传

2013-02-26 上传

weixin_49377467

- 粉丝: 0

最新资源

- 高效实现网页自动二维码生成技术

- Coursera_Capstone项目实践与JupyterNotebook应用

- 3D局部放大镜动画特效实现方法

- RocketMQ官方开发手册3.2.4版全面解析

- 在 Heroku 上部署基础 PHP 应用程序的完整指南

- 凡信:基于环信SDK的Android仿微信聊天应用源码

- Android渐变文字进度条效果实现教程

- 新闻网格网站:CSS Grid设计与实现

- JAVA操作FileMaker数据库实战教程

- 支持自定义关闭按钮的jQuery全屏广告代码

- CalFacility: 计算机辅助制造系统的研究与开发

- STM32F1ZET6 TIM3 PWM输出实验代码及电机驱动应用示例

- 实现Android文本内容到系统剪贴板的复制操作

- 易语言开发的账单库存管理系统4.0开源版本

- 简易快速实现网页回顶部功能的jQuery教程

- 佳博打印机SDK整合Labview等多语言例程