Vivado 2020.2综合设计指南:Synthesis深度解析

"VivadoDesignSuite用户指南,专注于综合部分,版本为2020.2,由Xilinx公司发布,包含更新日志、合成设置使用、运行合成、Tcl运行合成、VHDL架构示例、FSM编码、RAM风格、事件控制时间控制语句等关键内容。"

在Vivado Design Suite中,Synthesis是将高级设计语言(如Verilog或VHDL)转换为硬件描述的逻辑等效过程,这个过程是 FPGA 设计流程的核心步骤。本用户指南详细介绍了如何在Vivado 2020.2版本中进行有效的综合操作。

1. **使用Synthesis Settings**:

- 更新了`debug_log`的使用,这可能涉及如何配置和分析综合过程中的调试日志,以便更好地理解设计优化的过程和问题。

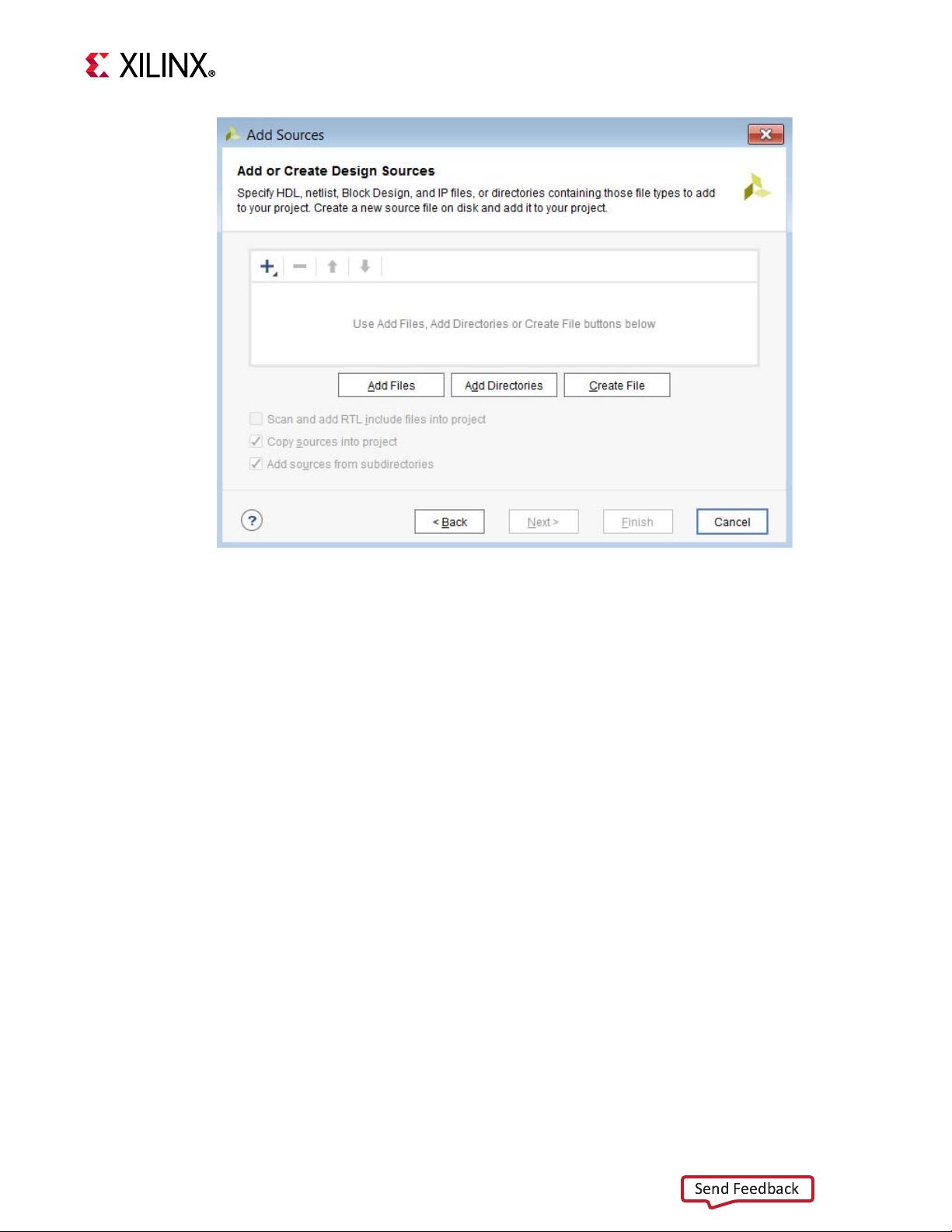

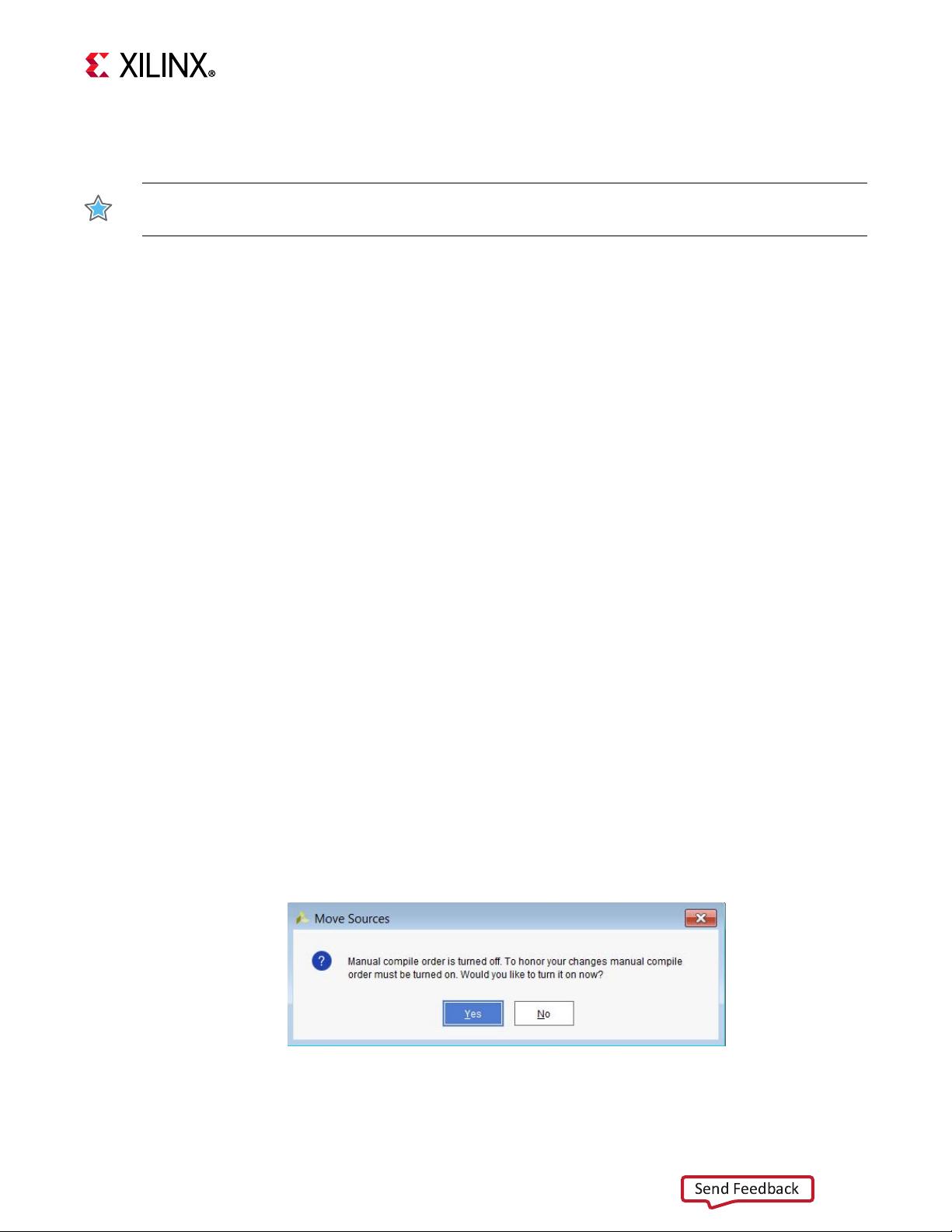

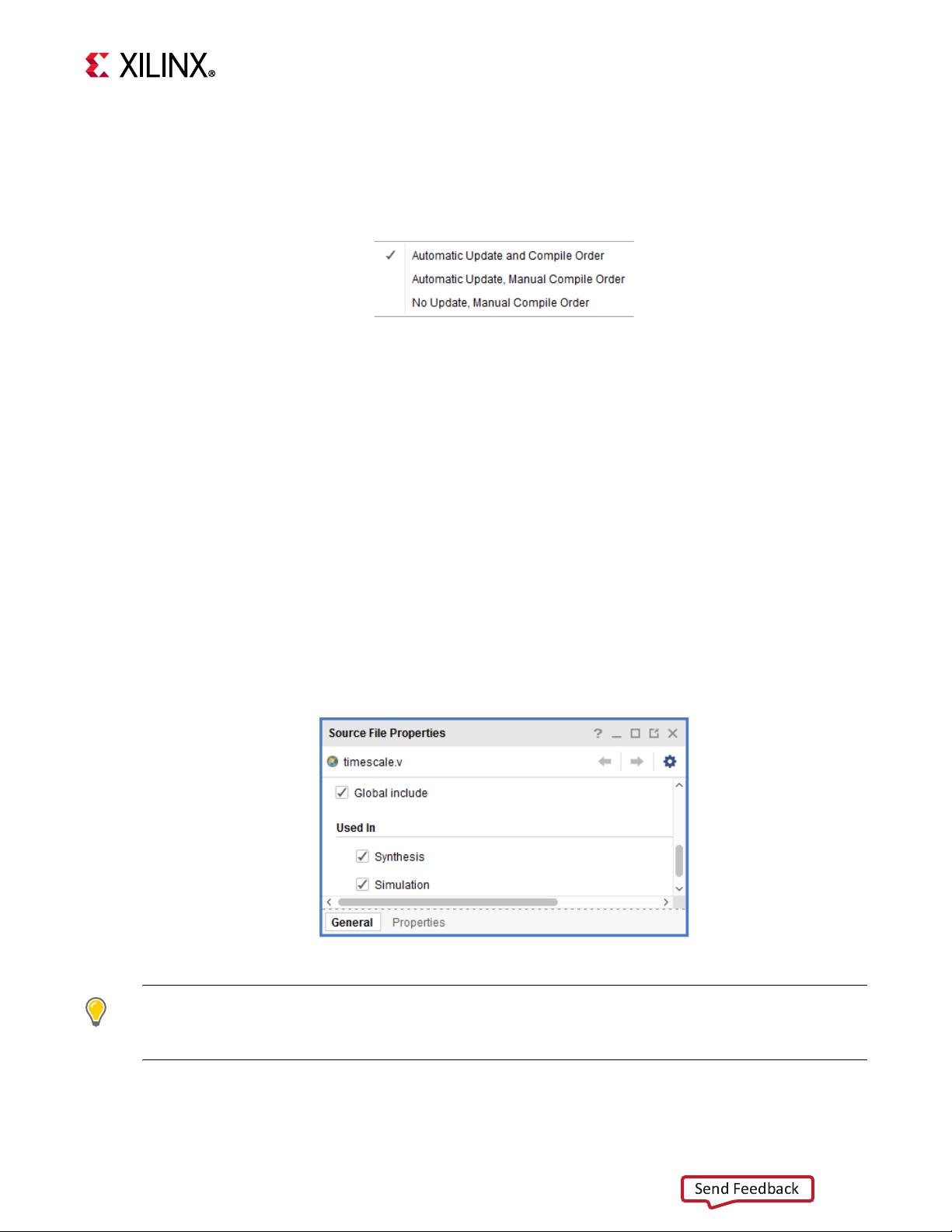

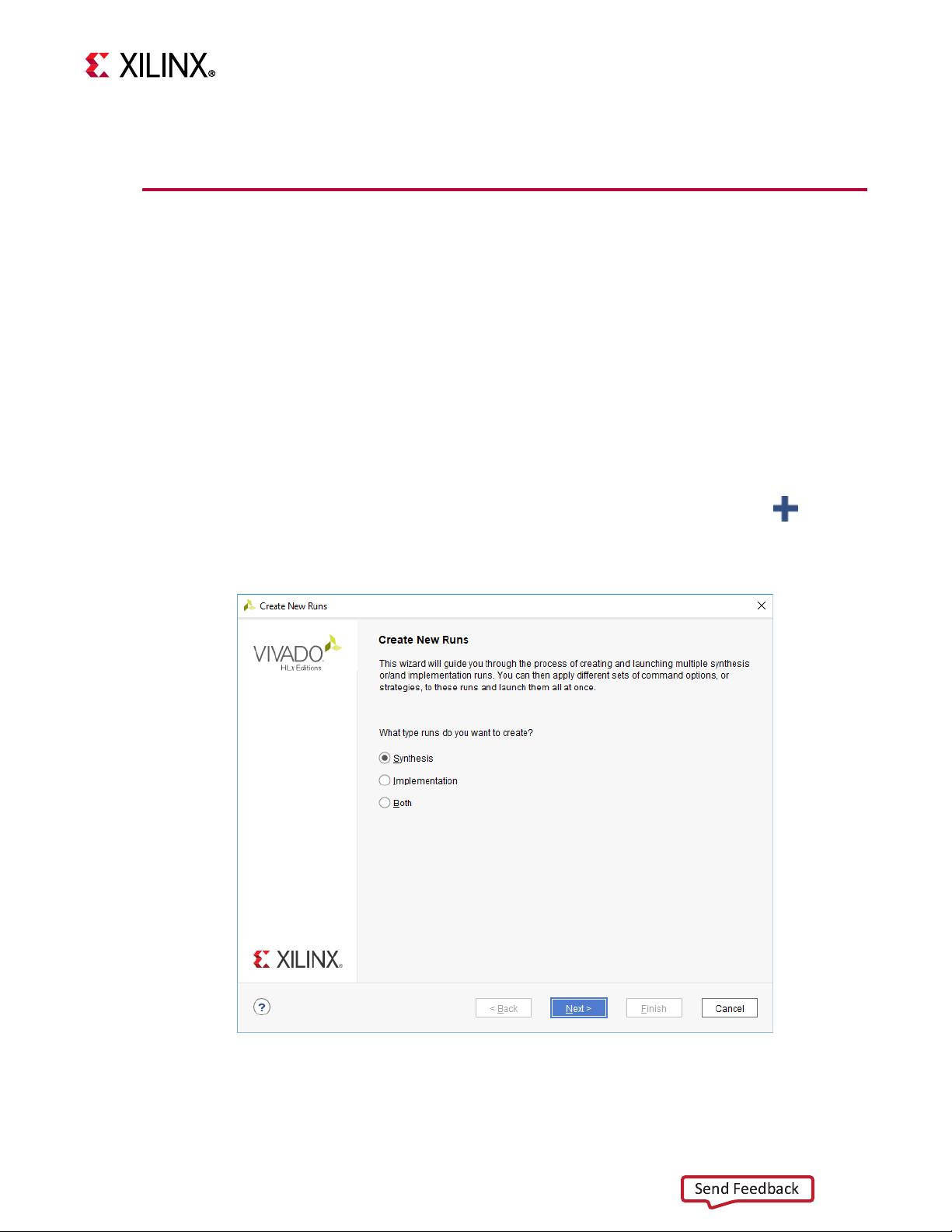

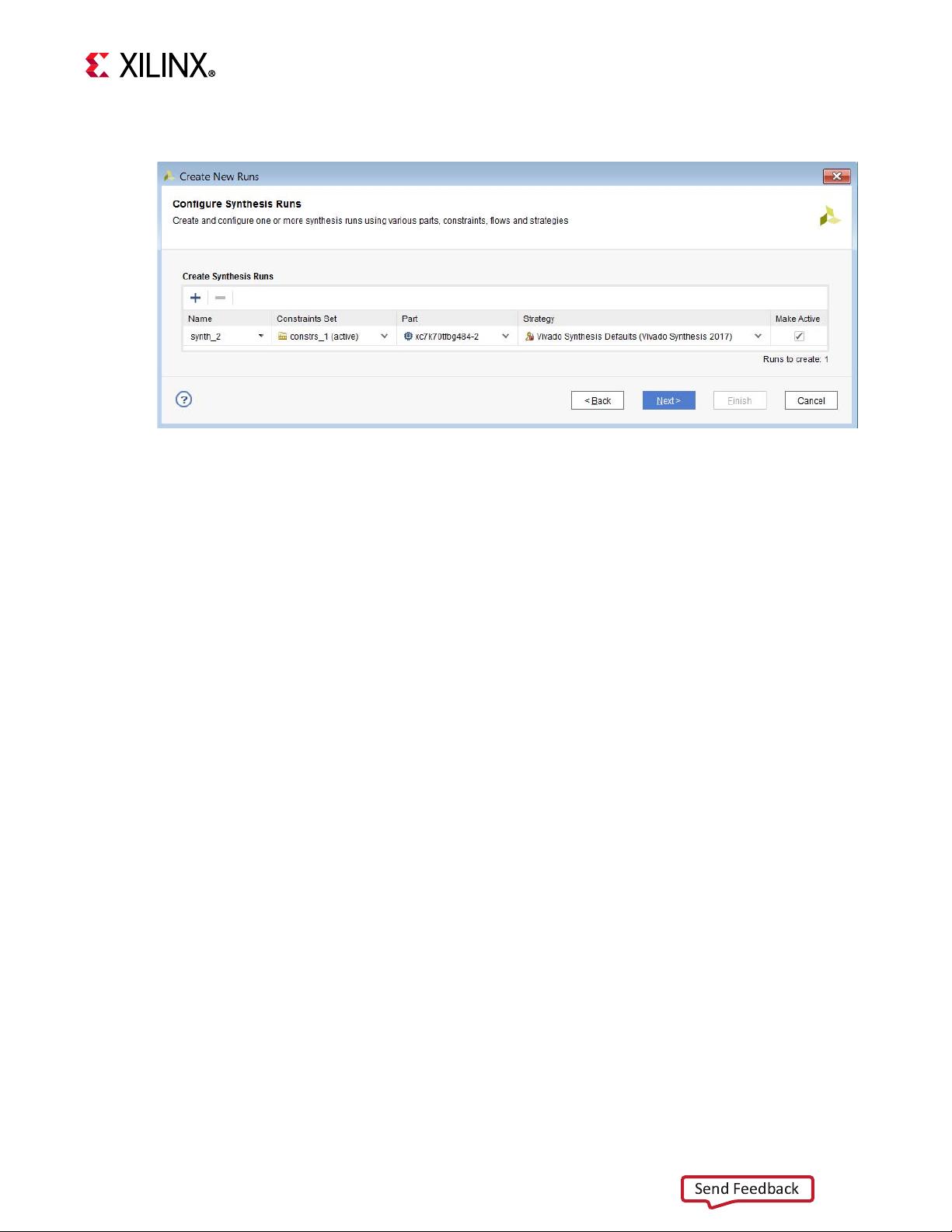

2. **运行Synthesis**:

- 添加了一个注意事项,可能关乎合成过程中需要注意的关键点,以确保设计的成功和优化。

3. **通过Tcl运行Synthesis**:

- 更新了`synth_design`命令的帮助输出示例,这可能涉及使用Tcl脚本来自动化和定制综合过程。

4. **VHDL Example on Architecture**:

- 更新了VHDL架构的例子,展示了如何更有效地描述和综合VHDL设计。

5. **FSM_ENCODING (有限状态机编码)**:

- 添加了用户编码信息,这对于优化状态机的面积和功耗至关重要。

6. **RAM_STYLE (RAM样式)**:

- 增加了关于混合值的信息,说明了如何针对不同类型的存储器结构选择最佳的RAM风格,以满足设计的需求。

7. **Table 3-1**:

- 添加了`SRL_STYLE`选项,这可能涉及到寄存器传输级(RTL)级的延迟优化。

8. **Table 7-5 和 Table 8-1**:

- 这些表格的更新可能涉及到时间控制语句和事件控制的改进,对理解和优化时序路径有直接影响。

9. **Event Control Time Control Statement**:

- 更新了事件控制时间控制语句,这对于精确控制设计中的时序行为至关重要。

10. **Send Feedback**:

- 提供了反馈机制,鼓励用户报告问题和建议,以持续改进Vivado工具的性能。

此外,文档还涵盖了设置自下而上的非上下文流程(Bottom-Up Out-of-Context Flow)、增量合成(Incremental Synthesis)以及如何将进程移到后台运行,以提高工作效率。这些特性对于大型项目和迭代设计尤其有用,能够减少不必要的计算资源消耗并加快设计周期。

Vivado Synthesis用户指南通过详尽的说明和实例,帮助设计者充分利用工具功能,实现高效、优化的FPGA设计。对于那些希望深入理解Vivado 2020.2综合流程的开发者来说,这份文档是一份宝贵的参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-05-13 上传

2019-06-12 上传

2020-08-13 上传

2020-08-13 上传

2021-04-09 上传

2021-08-09 上传