FPGA实现PS2接收:协议解析与FPGA设计

201 浏览量

更新于2024-09-02

收藏 163KB PDF 举报

"这篇文章除了介绍PS2协议的基础知识外,还涉及如何使用FPGA实现PS2接收。文章中提到,PS2协议在没有数据传输时,时钟线和数据线都保持高电平。传输时,PS2设备会启动时钟和数据变换,数据在时钟上升沿变化,接收端应在时钟下降沿捕获数据。作者使用FPGA进行设计,虽然没有采用典型的状态机方法,但依然实现了数据的接收。提供的代码片段展示了如何检测时钟的下降沿以及如何采集数据。"

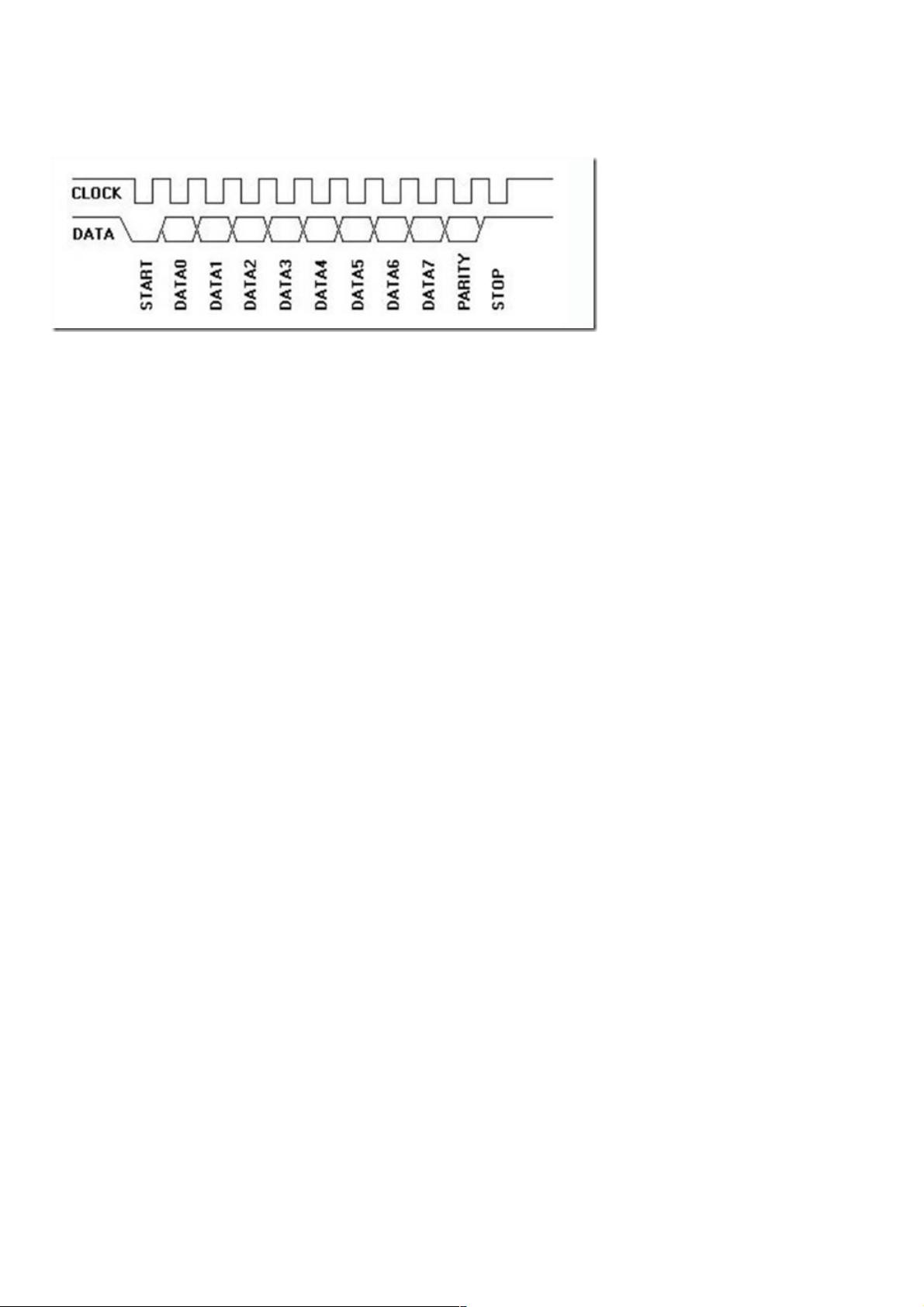

在深入探讨FPGA中的PS2协议实现之前,我们先来了解一下PS2协议的基本概念。PS2(Personal System/2)是IBM在1987年推出的一种接口标准,主要用于连接键盘和鼠标到个人计算机。该协议是串行通信协议,使用两根线:一根时钟线(Clock)和一根数据线(Data)。在无数据传输状态下,这两根线都保持高电平。当数据需要传输时,PS2设备会通过时钟线发送时钟信号,并在数据线上按照时钟同步传输数据。

在FPGA实现PS2接收的过程中,关键在于正确地捕获数据。由于数据在时钟上升沿变化,因此接收端通常会在时钟的下降沿读取数据,以确保数据稳定。这种同步方式被称为边沿触发。文中给出的代码片段展示了如何检测时钟的下降沿:

```verilog

reg ps2_clk_r;

reg ps2_clk_r_r;

wire ps2_clk_falling;

always @(posedge clk) begin

if (!rst_n) begin

ps2_clk_r <= 'b1;

ps2_clk_r_r <= 'b1;

end

else begin

ps2_clk_r <= ps2_clk;

ps2_clk_r_r <= ps2_clk_r;

end

end

assign ps2_clk_falling = ps2_clk_r_r & (!ps2_clk_r);

```

这段代码创建了两个寄存器`ps2_clk_r`和`ps2_clk_r_r`来延迟时钟信号,以便检测下降沿。当`ps2_clk_r_r`为高且`ps2_clk_r`变为低时,`ps2_clk_falling`信号将变为高,表示时钟的下降沿发生。

在实际的数据接收过程中,除了要考虑时钟同步,还需要处理数据的校验。如描述中所提到,PS2协议中每个数据字节包括8位实际数据和1位奇偶校验位。接收端需要检查接收到的数据的奇偶校验是否正确,以确认数据在传输过程中没有错误。这个过程可以通过简单的逻辑操作来实现,例如计算接收到的8位数据中1的个数,与接收到的奇偶校验位进行比较。

在FPGA设计中,作者可能使用类似以下的结构来接收并校验数据:

```verilog

reg [7:0] data_buffer;

reg parity_valid;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_buffer <= 8'b0;

parity_valid <= 1'b0;

end

else if (ps2_clk_falling) begin

data_buffer <= {data_buffer[6:0], ps2_data};

parity_valid <= (data_buffer[7] == parity_check(data_buffer[6:0]));

end

end

function bit parity_check(input [7:0] data);

integer i;

parity_check = 1'b1;

for (i = 0; i < 8; i = i + 1) begin

parity_check = parity_check ^ data[i];

end

endfunction

```

这里,`data_buffer`用于存储接收到的数据,`parity_valid`表示校验是否通过。在每次时钟下降沿,`data_buffer`左移一位并将新的数据位放入最低位,同时计算当前数据的奇偶校验并与接收到的校验位比较。

实现FPGA中的PS2接收涉及到对时钟和数据信号的精确同步,以及数据的校验。通过状态机或非状态机的方法,可以有效地控制数据接收流程,确保数据的完整性和正确性。这个过程对于理解串行通信协议、FPGA设计和数字逻辑验证具有重要的学习价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-14 上传

2021-11-02 上传

2022-09-24 上传

2012-08-28 上传

点击了解资源详情

点击了解资源详情

weixin_38693967

- 粉丝: 3

- 资源: 891

最新资源

- 高等教育出版社数据库第四版课后答案

- ads(射频)中文教程

- .NETGridView、TreeView数据绑定

- MATLAB 程式设计与应用.doc

- RTX51使用手册(中文)

- Matlab数理统计工具箱应用简介

- UCOS-II (Jean J.Labrosse 著)

- DWR中文文档(初学者学习DWR的好资料)

- The Next 700 Programming Languages

- 虚函数的理解内部细节

- 基于遗传算法的人工生命演示系统设计.pdf

- 数值方法求积分公式程序

- VC++程序员设计指南

- Architecture Of a Database System

- 新编Windows API参考大全

- Java面试宝典-完整版