9

DLPC300

www.ti.com.cn

ZHCS244C –JANUARY 2012–REVISED AUGUST 2015

Copyright © 2012–2015, Texas Instruments Incorporated

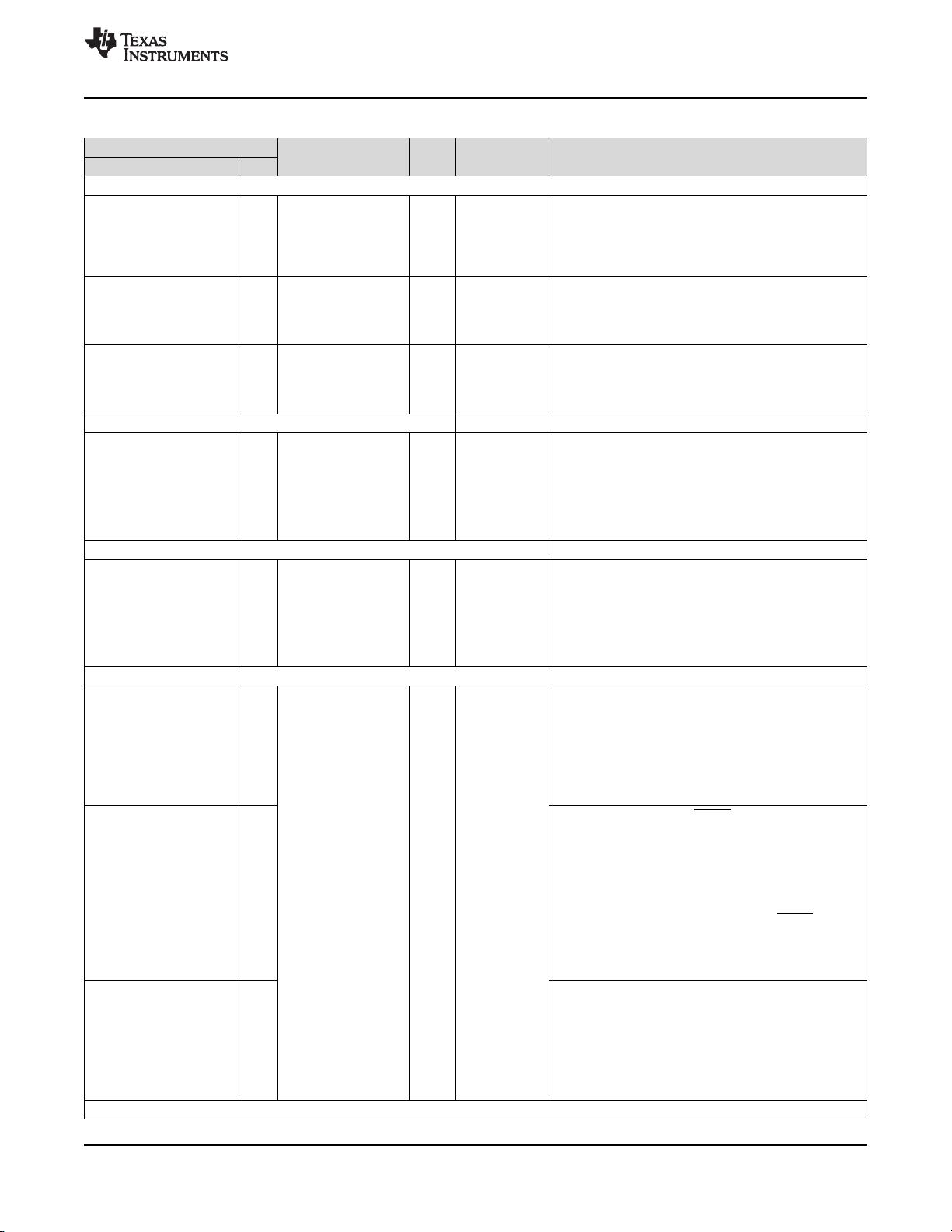

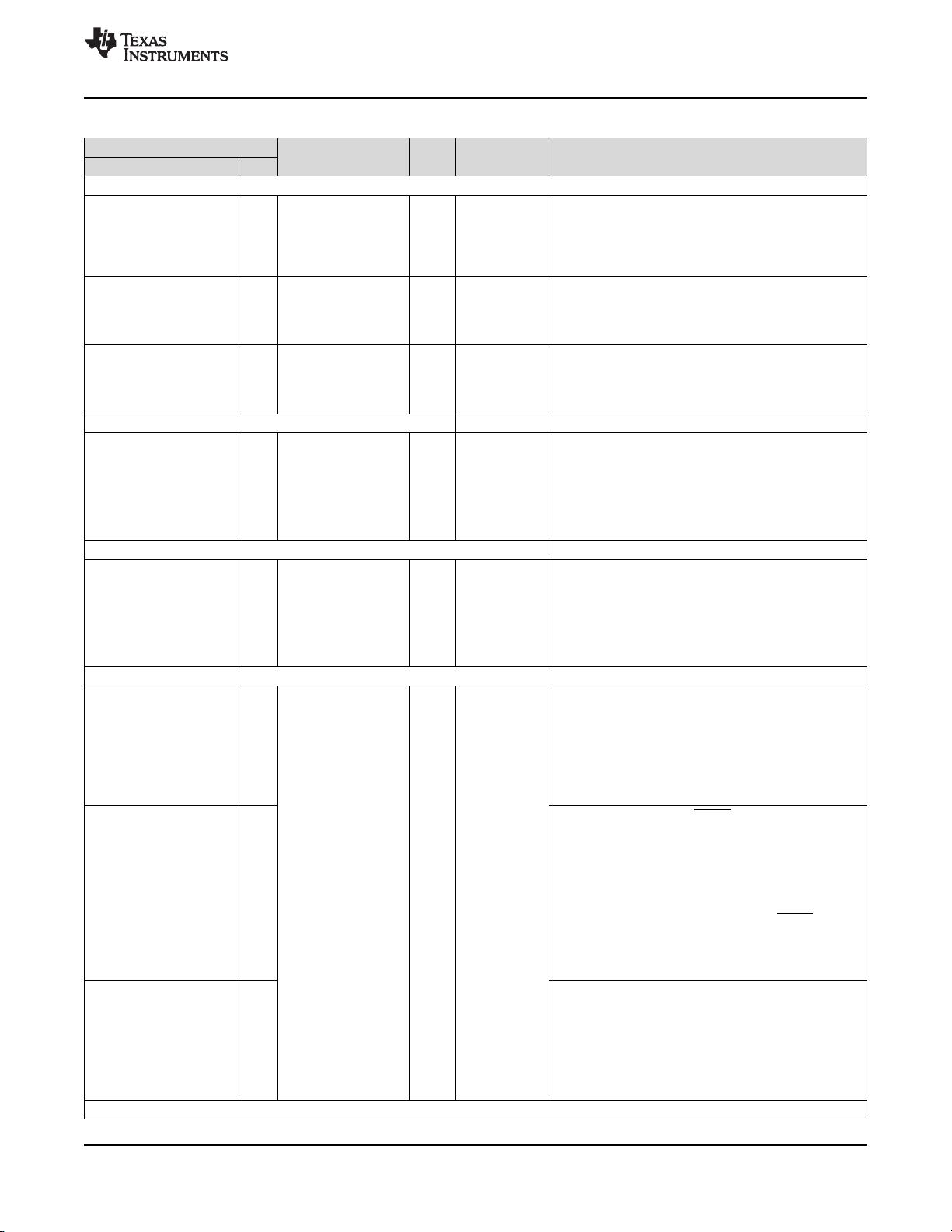

Pin Functions (continued)

PIN

I/O

POWER

I/O

TYPE

CLK SYSTEM DESCRIPTION

NAME NO.

WHITE POINT CORRECTION LIGHT SENSOR I/F

CMP_OUT A6 VCC18 I

1

Async

Successive approximation ADC comparator output (DLPC300

input). Assumes a successive approximation ADC is

implemented with a light sensor and/or thermocouple feeding

one input of an external comparator and the other side of the

comparator driven from the DLPC300 CMP_PWM pin. If not

used, this signal should be pulled down to ground.

CMP_PWM B7 VCC18 O

14

Async

Successive approximation comparator pulse-duration

modulation input. Supplies a PWM signal to drive the

successive approximation ADC comparator used in light-to-

voltage light sensor applications. Should be left unconnected if

this function is not used.

CMP_PWR P5 VCC18 B

14

Async

Power control signal for the WPC light sensor and other analog

support circuits using the DLPC300 ADC. Alternatively, it

provides general-purpose I/O to the WPC microprocessor

internal to the DLPC300. Should be left unconnected if not

used.

TRIGGER CONTROL

OUTPUT_TRIGGER

N9 VCC18 B

18

Async

Trigger output. Indicates that a pattern or image is displayed on

the screen and is ready to be captured. With an optional FPGA,

this signal is connected to the FPGA trigger input. This signal is

configured as output and driven low when the DLPR300 serial

flash PROM is loaded by the DLPC300, but the signal is not

enabled. To enable this output, a write to I

2

C LED Enable and

Buffer Control register. If not used, this signal should be pulled

down to ground through an external resistor.

PATTERN CONTROL

PATTERN_INVERT

C7 VCC18 B

18

Async

Inverts the current 1-bit pattern held in the DLPC300 buffer.

When used with an optional FPGA, this signal should be

connected to DMC_TRC of the FPGA. This signal is configured

as output and driven low when the DLPR300 serial flash PROM

is loaded by the DLPC300, but the signal is not enabled. To

enable this output, a write to I

2

C LED Enable and Buffer

Control register. If not used, this signal should be pulled down

to ground through an external resistor.

OPTIONAL FPGA BUFFER MANAGEMENT INTERFACES

RD_BUF0

B6

VCC18 B

18

Async

When not used with an optional FPGA, this signal should be

pulled down to ground through an external resistor. When used

with an optional FPGA, this signal should be connected to

RD_PTR_SDC[0] of the FPGA. RD_BUFF1 and RD_BUFF0

indicate to the FPGA one of the four buffers currently in use.

This signal is configured as output and driven low when the

DLPR300 serial flash PROM is loaded by the DLPC300, but

the signal is not enabled. To enable this output, a write to I

2

C

LED Enable and Buffer Control register.

RD_BUF1/I2C_ADDR_SEL

R9

This signal is sampled when RESET is deasserted to choose

between two predefined 7-bit I

2

C slave addresses. If

I2C_ADDR_SEL signal is pulled-low, then the DLPC300's I

2

C

slave address is 1Bh. If I2C_ADDR_SEL signal is pulled-high,

then the DLPC300's I

2

C slave address is 1Dh. When used with

an optional FPGA, this signal should be connected to

RD_PTR_SDC[1] of the FPGA. RD_BUFF1 and RD_BUFF0

indicate to the FPGA one of the four buffers currently in use.

This signal is set to input upon deassertion of RESET and

configured as output and driven low when the DLPR300 serial

flash PROM is loaded by the DLPC300, but the signal is not

enabled. To enable this output, a write to I

2

C LED Enable and

Buffer Control register.

BUFFER_SWAP

A8

When not used with an optional FPGA, this signal should be

pulled down to ground through an external resistor. When used

with an optional FPGA, this signal should be connected to

BUFF_SWAP_SEQ of the FPGA. BUFFER_SWAP indicates to

the FPGA when to advance the buffer. This signal is configured

as output and driven low when the DLPR300 serial flash PROM

is loaded by the DLPC300, but the signal is not enabled. To

enable this output, a write to I

2

C LED Enable and Buffer

Control register.

CONTROLLER MANUFACTURER TEST SUPPORT