复旦大学数字电路设计:Chapter8 设计挑战与方法

需积分: 9 177 浏览量

更新于2024-07-09

收藏 5.3MB PDF 举报

"复旦大学的数字电路设计教程,专注于Chapter 8的内容,涉及数字集成电路的设计方法学。此资料探讨了随着技术发展,数字电路设计的复杂性与设计生产力之间的矛盾,以及多种实现方法对设计选择的影响。"

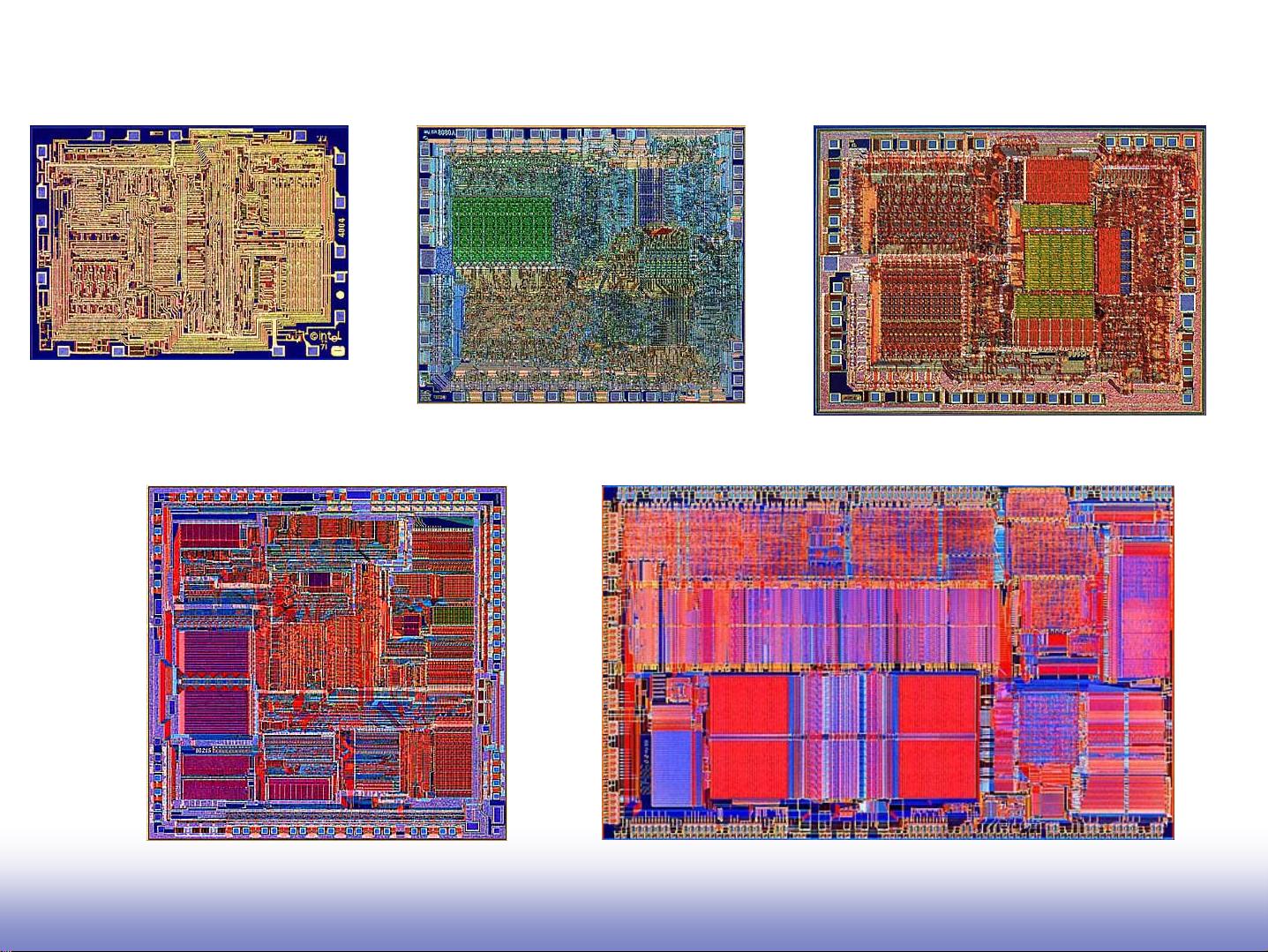

在数字集成电路设计领域,Chapter 8可能涵盖的主题包括但不限于高级逻辑设计、VLSI(超大规模集成电路)设计流程、可综合逻辑设计、逻辑优化、测试策略和功耗管理等关键概念。随着技术的进步,集成电路的规模和复杂性在以每年约58%的速度增长,而设计生产力的增长率仅为21%,这导致了设计挑战的加剧。图表显示了自1981年以来逻辑门数量与每个设计人员月的工作量之间的关系,揭示了设计复杂度的急剧增加和生产力增长的相对缓慢。

设计生产力的挑战主要源于以下几点:

1. 设计复杂度:随着摩尔定律的推进,芯片上的晶体管数量每两年几乎翻一番,增加了设计的复杂性和验证的难度。

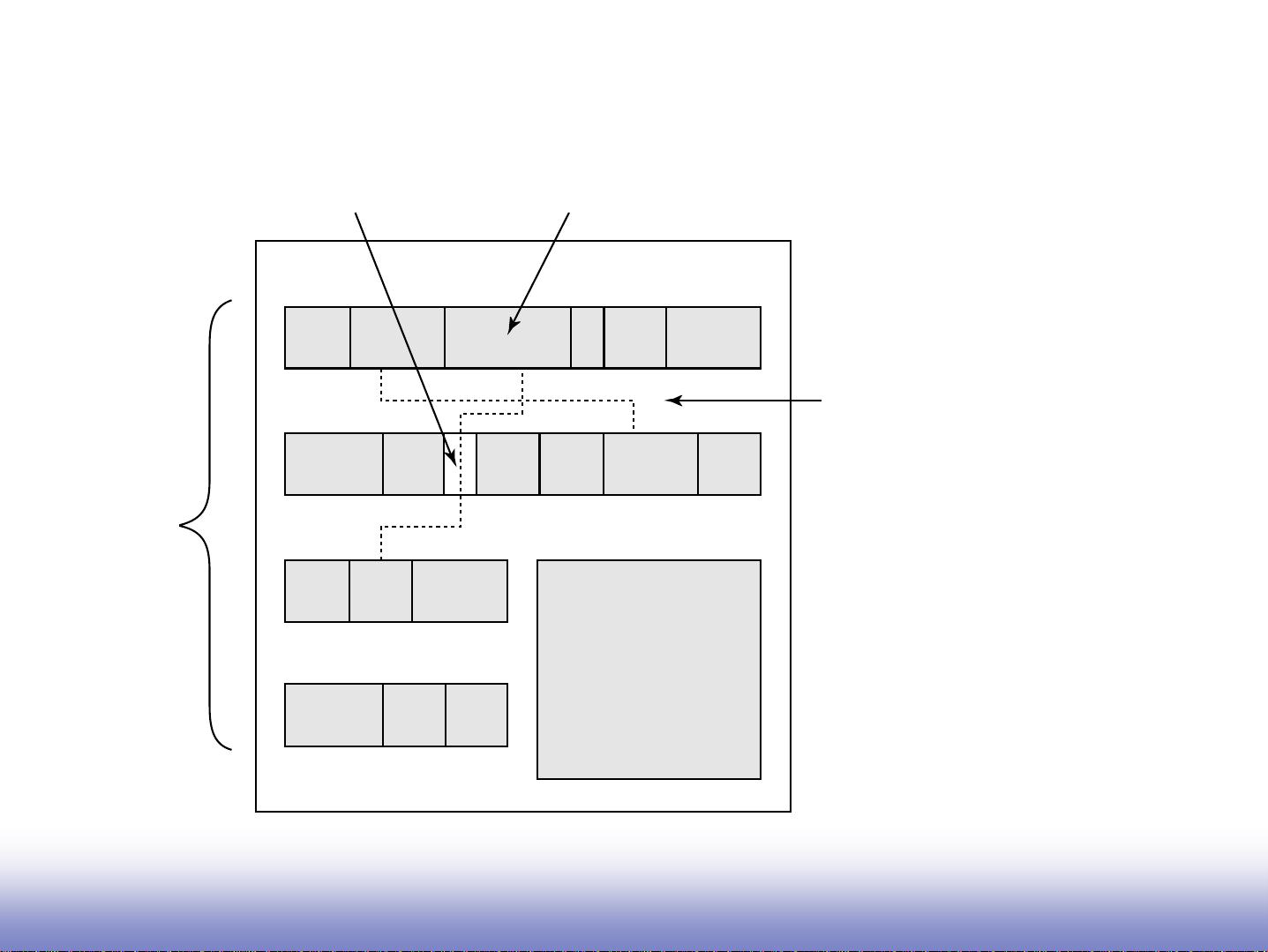

2. 多样的实现方式:现代数字设计中存在多种技术,如ASIC、FPGA和SoC,它们各自有不同的性能、灵活性和能效特点。选择最佳实现路径成为设计者面临的重要决策。

3. 设计自动化工具的限制:尽管有先进的EDA(电子设计自动化)工具,但处理大规模设计时,工具的效率和准确性仍是制约因素。

4. 功耗管理:随着集成度提高,功耗问题变得日益突出,如何在满足性能需求的同时降低功耗,是设计中的关键考量。

5. 测试与验证:随着电路的复杂性增加,测试成本和时间也成比例增长,验证整个设计的正确性变得极其复杂。

Chapter 8可能会详细讨论如何通过优化设计流程、采用高级设计方法和工具,以及利用合成逻辑来应对这些挑战。这可能包括学习如何使用硬件描述语言(如Verilog或VHDL),进行逻辑综合和布局布线,以及如何考虑物理实现对设计性能的影响。此外,课程可能还会涉及低功耗设计技术,如动态电压频率调整(DVFS)和多电压域设计。

复旦大学的这一章节旨在使学生理解并掌握解决现代数字电路设计中关键问题的策略和方法,为未来在这个快速发展的领域中进行创新和实践打下坚实基础。

129 浏览量

110 浏览量

114 浏览量

129 浏览量

118 浏览量

104 浏览量

129 浏览量

2021-05-20 上传

2021-05-20 上传

weixin_38700320

- 粉丝: 4

- 资源: 931

最新资源

- StateEstimationforRobotics-CN.pdf.tar.gz

- Desktop,c语言火车票订票管理源码,c语言

- node-font-list:获取系统中安装的字体列表

- 菲尼克斯微型继电器手册.rar

- MICROMAKEL3+ 3ds chitubox插件

- Honeywell_hackathon

- developer-knowledge:独立的增强型知识项目分层清单,可以成为更好的软件开发人员。 标题

- h2gis,H2数据库的空间扩展。.zip

- NewtonJson.rar

- shell:一种用于IBM Cloud Functions and Composer的基于电子的开发工具

- 20210315-中国联通-通信行业:5G终端白皮书V4(2021年度).rar

- 单片机频率计仿真protues

- 情人节图标 .svg素材下载

- Android_Projects:我尝试学习Android开发时所做的旧项目

- 主题默认值:Hexsoftstudio CSS默认值

- Gestrue,安卓、安卓、安卓.zip