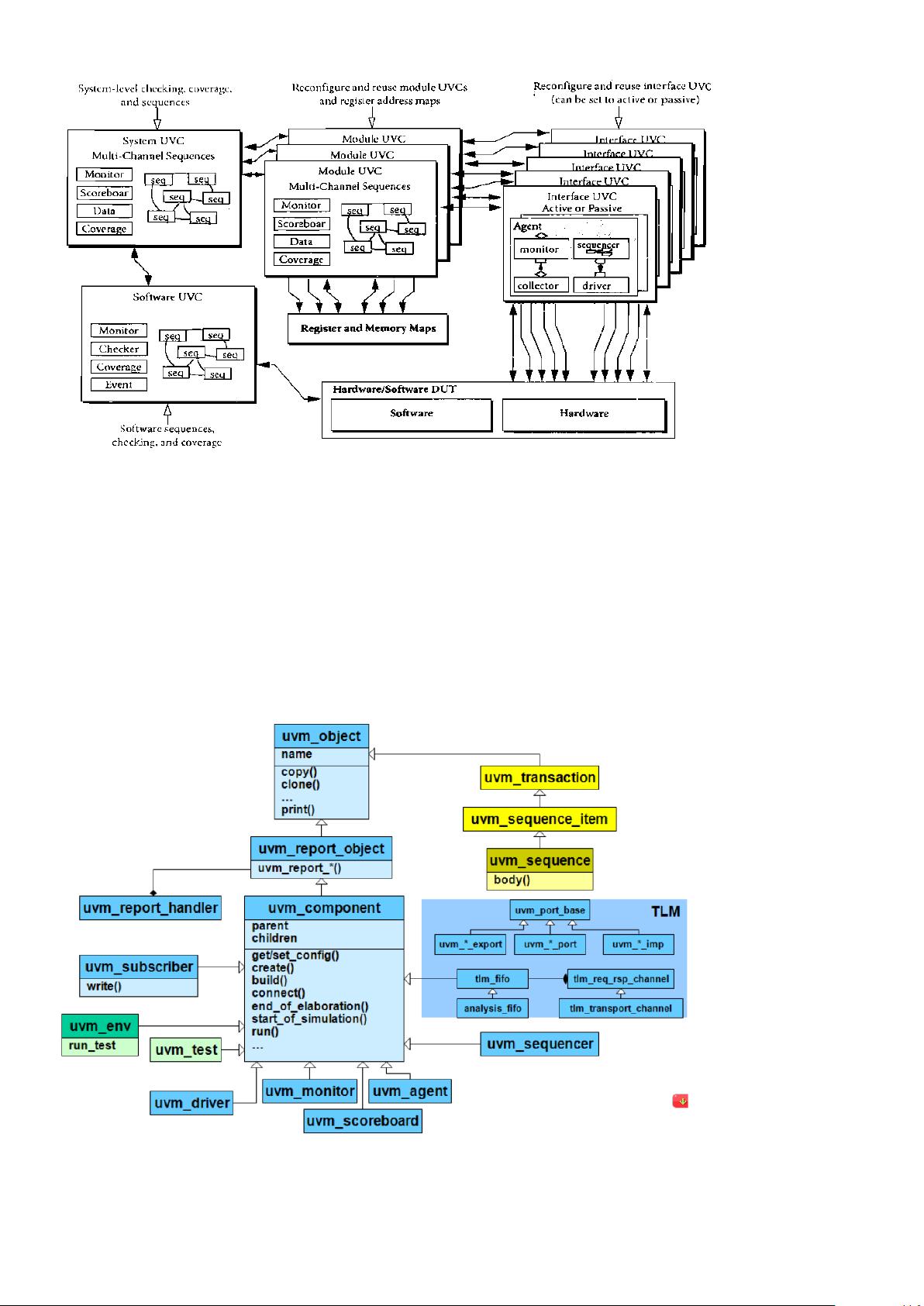

testbench is specific to the DUT and to the project, and is typically not reused in vertical reuse scenarios. Refer to Figure

2-1 to see the integration of multiple UVCs in a UVM testbench.

2.3 System and Module UVCs

As already discussed, an interface UVC captures protocol-related verification aspects. But where would you place a

device-specific set of verification aspects? For example, where would you place end-to-end coverage of multiple interfaces?

Or a DUT-specific checker? For these purposes, a module UVC is needed. A module UVC is an environment that contains

verification logic for a specific module or subsystem. It assists in verifying this subsystem, as it is vertically reused in a larger

environment.

A system UVC makes use of interface, module, and software UVCs (UVCs that can dynamically control software

execution). A system UVC might not contain its own agents, in which case it merely instantiates other UVCs and connects

them to create a larger verification environment. System UVCs are targeted at system verification—for example, a CPU,

bridge, or a cell phone. Relatively small system UVCs sometimes are called module UVCs. A system UVC typically makes use

of other UVCs, including:

Interface UVCs for connecting to the system interfaces

Other module or system UVCs, which are subsystems or modules of the current system being verified

Any system UVC can he reused in a larger system verification environment. The system UVC architecture is similar to

the interface UVC architecture and contains:

A collector for signals that connect to the DUT.

A monitor that is fed by the collector and other interface UVCs’monitors. Virtual (multiple channel) sequencers

connected to the sequencers of the interface and subsystem UVCs. While interface UVC sequencers control a single

interface, a virtual sequencer controls multiple sequencers and orchestrates the system-level scenario. Its sequence

library defines multiple-channel sequences, which simultaneously control all of the system interfaces.

A scoreboard—an untimed reference model that allows end to end checking. The scoreboard receives input from the

interface UVCs and compares the DUT responses to the testbench prediction for the same input. We recommend

using a scoreboard in the system UVC.

An address map and register files. Most systems use memory and registers, which can be modeled using a register

package. With UVM, you will have a pointer to the register database address map and register files.

2.3.1 Software UVCs

Verification poses requirements such as How can you ensure that an interrupt occurred while visiting all the software

states? Or, How can you steer the simulation to visit this specific HW/SW corner cases? SW UVCs arc- elegant solutions for

requirements such as these.

A SW UVC expands the coverage-driven verification (CDV) capabilities of a testbench to control and monitor software.

The software UVC provides run-time control to the execution of driver routines. It can control the type, time, and

parameters of routine calls, and can collect desired coverage for software state variables. Virtual sequences can be used to

seamlessly control HW interfaces and SW execution. Coverage monitors can collect coverage for HW, SW and their

associations.

Note We do not cover SW UVCs in this book, if you are interested in additional information regarding these, please

contact a Cadence representative.

Figure 2-4, Typical System-Level UVM Testbench, shows how interface, module, and system UVCs can be reused to

compose a specific verification environment, including HW/SW co-verification. Later in this book we cover the details of

how to develop this type of environment.