13GHz PLL快速建立技术:小于5us的200MHz跳频

82 浏览量

更新于2024-09-03

收藏 312KB PDF 举报

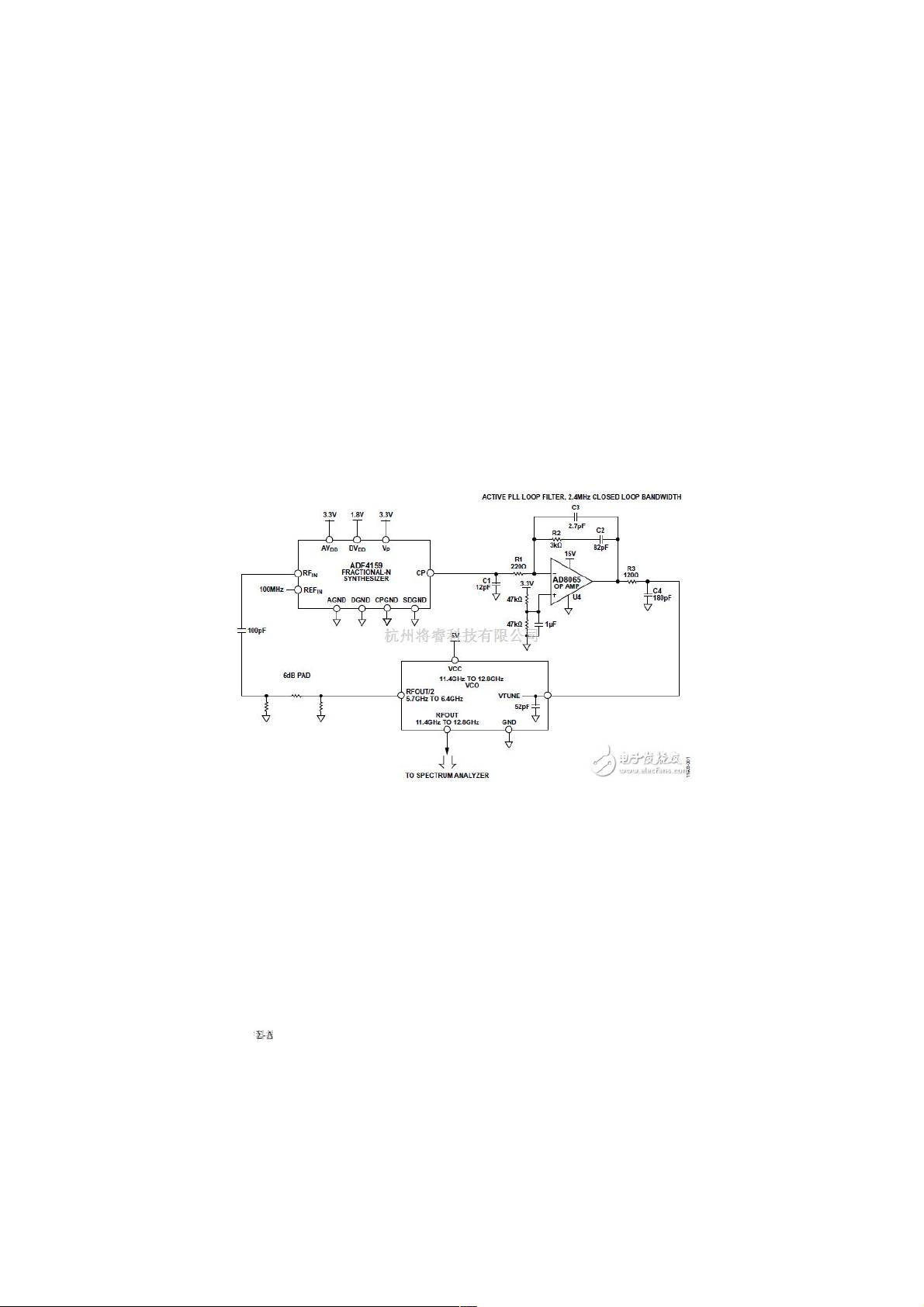

RF至13GHz超快速建立PLL是一种高性能的锁相环路频率合成技术,其核心在于电路设计的优化和关键组件的选择。电路的关键组成部分包括13 GHz的小数N分频频率合成器、宽带有源环路滤波器和高性能VCO。

1. 频率合成器:电路采用了ADF4159这种高性能鉴频鉴相器作为频率合成器,其PFD(Phase Frequency Detector)的最大工作频率可达110 MHz。这意味着它能够提供足够的带宽来处理高频信号,确保快速的频率和相位建立。

2. 有源环路滤波器:设计中采用了带宽为2.4 MHz的有源环路滤波器,这是实现快速建立时间的关键。AD8065运算放大器以其145 MHz的高增益带宽积特性,确保了滤波器的宽带性能,使得环路响应迅速,降低了锁定过程中的延迟。

3. VCO控制:AD8065运算放大器支持24 V电源电压,可以精确控制调谐电压范围,通常在0 V至18 V之间,适应多种宽带VCO的工作需求。这对于实现快速频率切换和保持良好的频率稳定至关重要。

4. 低建立时间:通过这些组件的协同工作,电路能够在5°以内的相位变化下,实现200 MHz的跳频相位在5微秒内建立完成。这样的速度远超常规PLL,对于需要快速频率响应的应用场景如无线通信、雷达等具有显著优势。

5. 环路带宽与稳定性:环路带宽决定了控制环路的响应速度,宽带环路有利于快速建立,但可能增加相位噪声和杂散信号。设计者需要在带宽与性能之间找到最佳平衡。

6. 频率范围:虽然ADF4159锁定的是12GHz VCO的RFOUT/2信号,但该电路设计的灵活性使其能与更高频率的VCO(如MACOMMAOC-009269,最高可达24GHz)配合使用,只要它们的RF输入不超过13GHz即可。

总结来说,RF至13GHz超快速建立PLL是一个利用先进元器件和技术实现高速、稳定频率锁定的解决方案,对于追求极高数据传输速率和快速响应的现代通信系统有着重要的应用价值。

2020-10-09 上传

2013-03-09 上传

点击了解资源详情

2024-11-14 上传

weixin_38695471

- 粉丝: 3

- 资源: 911

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜