13GHz PLL:超快相位建立技术与组件解析

192 浏览量

更新于2024-08-28

1

收藏 286KB PDF 举报

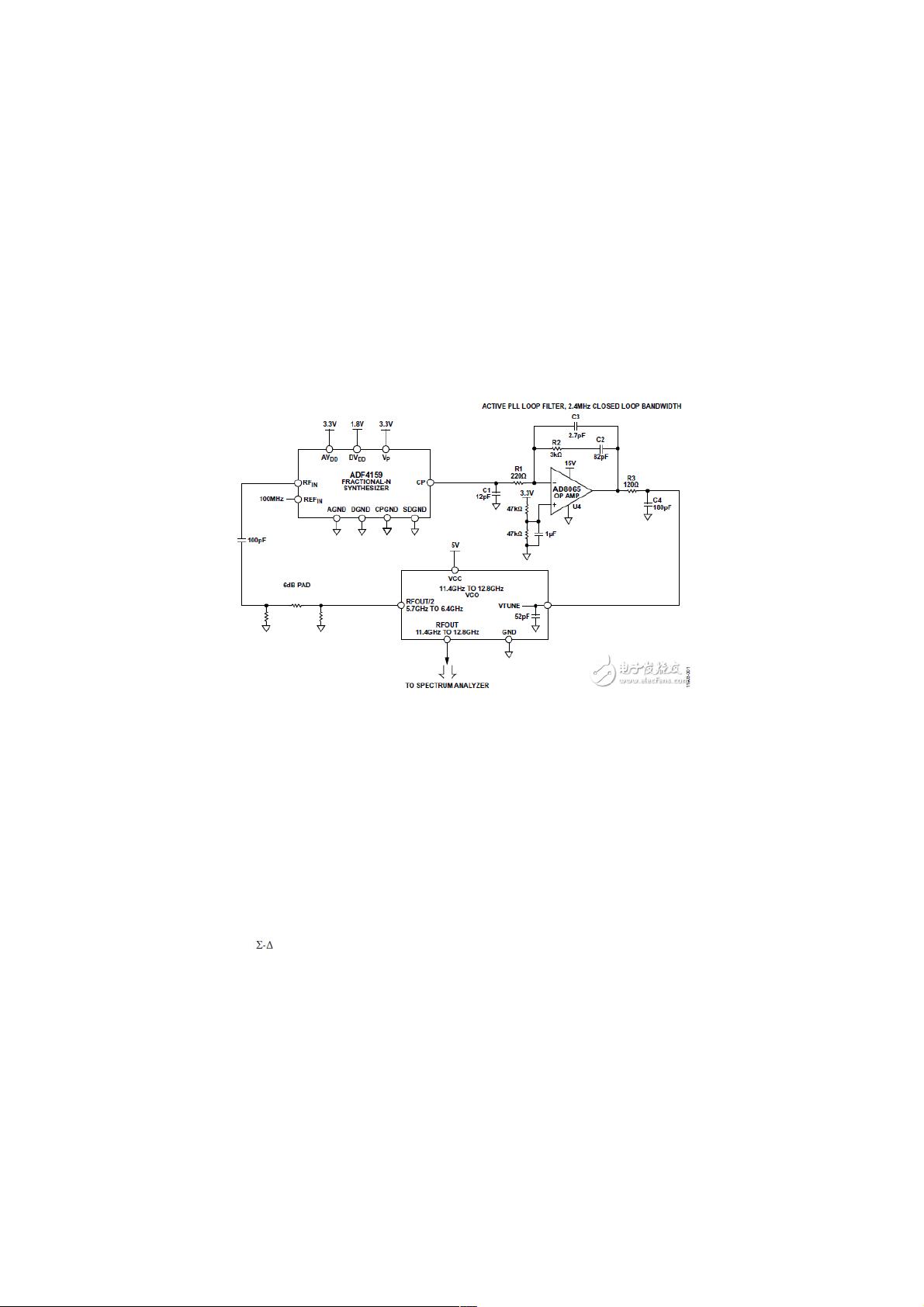

"本文介绍了一种RF至13GHz超快速建立时间的锁相环(PLL)电路设计,其中核心组件包括13 GHz的小数N分频频率合成器、宽带有源环路滤波器和电压控制振荡器(VCO)。通过采用特定的元器件配置,如ADF4159鉴频鉴相器(PFD)和AD8065运算放大器,实现了在5°以内的200 MHz跳频相位建立时间小于5微秒的卓越性能。"

PLL电路设计的关键在于其高速响应和高精度。在图1所示的电路中,13 GHz的小数N分频频率合成器是PLL的核心,它能够提供精细的频率步进和灵活的频率设定能力。小数N分频技术允许更广泛的频率选择,同时降低了相位噪声,提高了系统的整体性能。

ADF4159是一种高性能的鉴频鉴相器,其110 MHz的工作频率为整个环路提供了足够的带宽,确保了快速的相位调整。AD8065运算放大器作为有源环路滤波器的一部分,其145 MHz的高增益带宽积是实现2.4 MHz环路带宽的关键,这个宽带使得PLL能够在保持稳定性的前提下实现超快的频率切换速度。

有源环路滤波器是 PLL 控制环路的重要组成部分,它过滤了鉴相器产生的误差信号,并调节VCO的输出频率。AD8065运算放大器的工作电压范围(0V至24V)适应了大多数宽带VCO的调谐电压需求,确保了VCO可以在宽频率范围内高效工作。在图1中,11.4GHz至12.8GHz的VCO被用作例子,但根据需要,可以选用其他支持更高或更低频率的VCO。

PLL的相位建立时间与环路带宽直接相关。更宽的环路带宽意味着更快的频率响应,但也可能引入更多的噪声和杂散信号。在本设计中,通过精细平衡环路带宽(2.4 MHz)和组件特性,实现了快速相位建立时间的同时,保证了系统稳定性。

在实际应用中,ADF4159的小数N分频架构有效地降低了SDM噪声的影响。通过合理设置PFD频率(如32 MHz),可以避免在噪声峰值频率(16 MHz)附近产生不稳定。仿真结果如图2所示,12 GHz输出时的相位噪声曲线揭示了这种优化设计对噪声抑制的效果。

此RF至13GHz超快速建立PLL电路设计结合了高性能的器件和技术,实现了在高频范围内的快速频率切换和优良的相位噪声性能,适用于需要快速响应和高频率精度的通信、雷达和测试测量系统。

2018-12-06 上传

点击了解资源详情

2013-03-09 上传

2024-11-09 上传

weixin_38516706

- 粉丝: 9

- 资源: 888

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章