ARM920T的MMU与Cache解析

需积分: 9 68 浏览量

更新于2024-07-18

收藏 736KB DOC 举报

匿名")来标识,这部分称为堆(Heap)。地址空间中的其他部分如0xb77fe000-0xb7ffffff属于动态链接库(DynamicLinker)和其他共享对象(SharedObjects),它们被映射到磁盘上的相应文件。

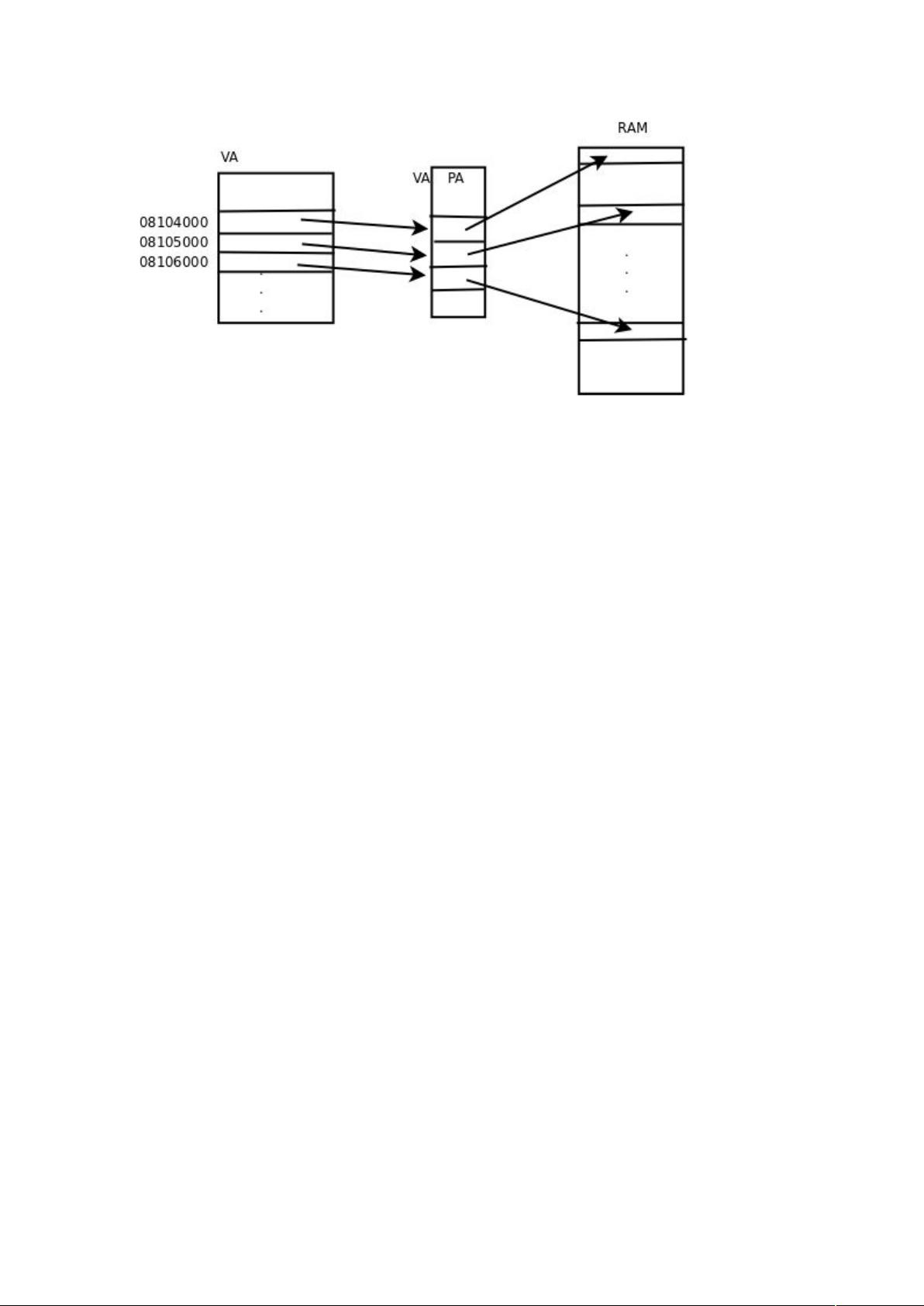

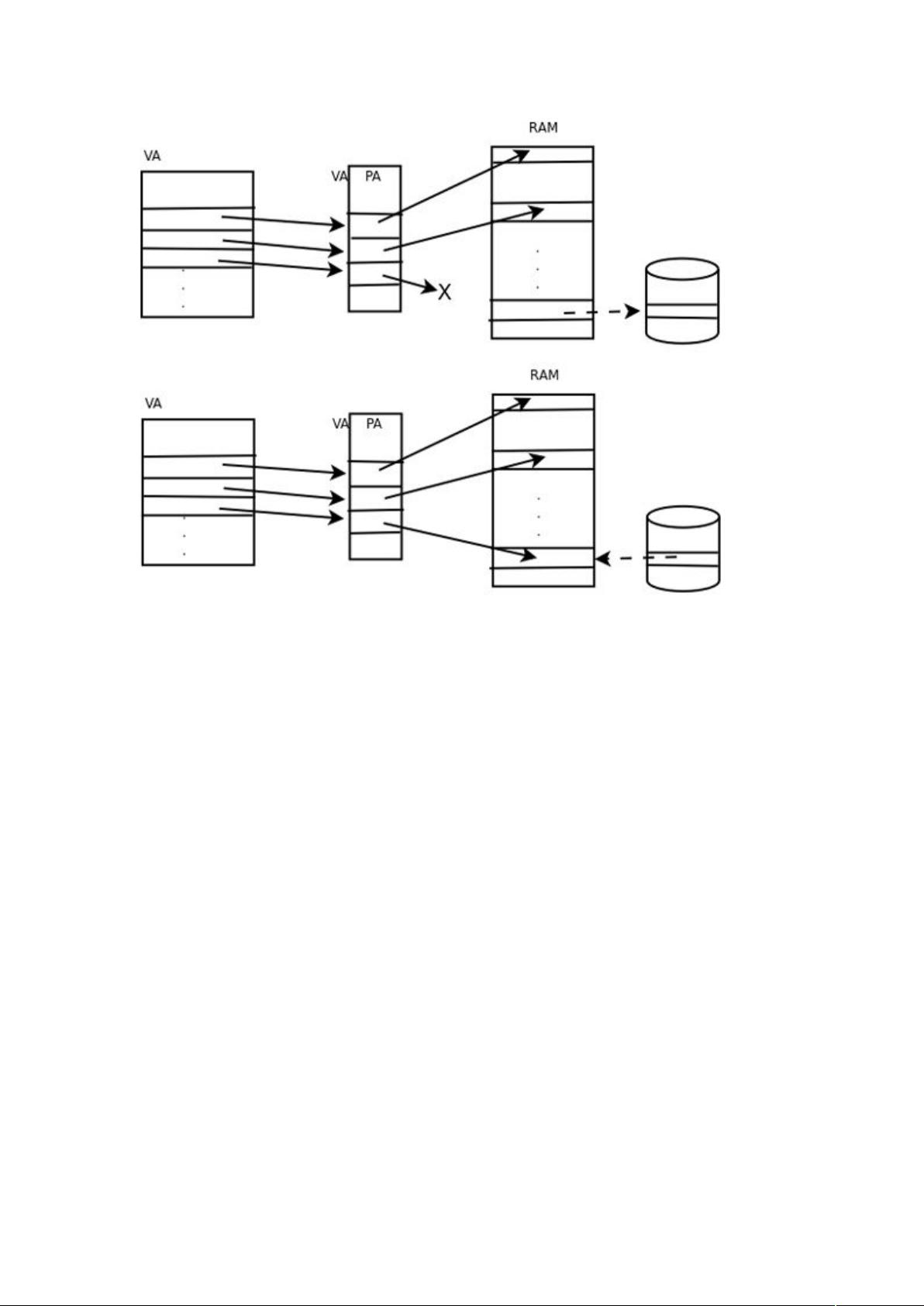

虚拟内存管理的核心是页表(PageTable),它由操作系统维护,记录了每个虚拟页如何映射到物理页。在ARM架构中,页表结构由多级页表组成,如在ARM920T中,通常采用两级页表,第一级页表(L1 Page Table)指向第二级页表(L2 Page Table),第二级页表则直接包含页表项(Page Table Entry,PTE),每个PTE包含了物理地址、访问权限等信息。

ARM920T的CP15协处理器

在ARM体系结构中,CP15协处理器(Coprocessor 15)是专门用于管理内存系统和MMU的。它提供了访问和控制虚拟内存系统、缓存、调试和性能监控等功能的接口。通过特定的指令,CPU可以读写CP15寄存器来配置MMU和Cache。

MMU

内存管理单元(MMU)的主要职责是实现虚拟地址到物理地址的转换。在ARM920T中,MMU支持页全局目录(PGD)、页中级目录(PMD)和页表条目(PTE)三级页表结构。当CPU访问虚拟地址时,MMU会通过页表找到对应的物理地址,并进行访问权限检查,确保合法访问。此外,MMU还可以实现内存保护,通过设置页表项的权限位,限制对某些区域的读写访问。

Cache

Cache是一种高速缓冲存储器,位于CPU和主内存之间,用于减少CPU访问主内存的延迟。ARM920T通常包含数据Cache和指令Cache,分别用于存储最近使用的数据和指令。Cache分为多个块(Block),每个块对应主内存中的一小片区域。当CPU尝试访问内存时,Cache首先检查是否已有所需数据,如果存在(命中),则直接从Cache读取;若不存在(未命中),则从主内存加载,并替换掉Cache中不常使用的数据。

操作MMU和Cache的内核启动代码

在操作系统启动初期,内核必须初始化MMU和Cache,以便正确地映射内存和启用缓存。这通常涉及设置页表、初始化CP15寄存器、配置Cache策略等步骤。例如,内核会为内核映像、物理内存分配页表项,然后启用MMU,使CPU开始使用虚拟地址空间。同时,内核还需要配置Cache的行为,如开启数据和指令Cache、设置写回或写穿策略、以及禁用缓存一致性协议(在多处理器系统中)等。

参考资料索引

1. ARM Architecture Reference Manual: ARMv4T-ARMv8, for ARMv8-A Architecture Profile

2. ARM920T Technical Reference Manual

3. Linux Device Drivers, 3rd Edition

总结,MMU与Cache在现代嵌入式操作系统中起着至关重要的作用。MMU通过虚拟内存管理提供内存保护和高效利用,而Cache则通过减少内存访问延迟提高系统性能。理解并掌握这两者的工作原理和配置方法,对于开发和优化嵌入式系统至关重要。

2009-09-21 上传

2013-02-28 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-02-27 上传

weixin_40987531

- 粉丝: 0

- 资源: 4

最新资源

- dostavka24:Dostavka24管理面板

- rpi-monitor-cam-led

- 004泥浆护壁回转钻孔灌注桩施工工艺.zip

- abbyjs:启发于MingGeJs,我也想写个霸气的自述文件和霸气的jQuery

- busfactor:如果fariz被公交车撞到了怎么办?

- DirectX修复工具&下载地址.zip

- uk-companies-scraper:部分出版物这是未来

- Sticky-nav-bar

- Hendrix-开源

- Proyecto-DWEC:Prosarecto del2ºtrimestre de Desarrollo网站和客户端

- 旅游及票务网站模版

- base-repo:GOSCPS基本存储库

- 【QGIS跨平台编译】之【FreeXL跨平台编译】:源码及跨平台编译工程(支撑QGIS跨平台编译,以及二次研发)

- 哈希表是什么及它的作用

- MONGO和MANGO一样甜

- grimrock-import:从Grimrock 1导入到Grimrock 2的资产集合