VLSI Design 3

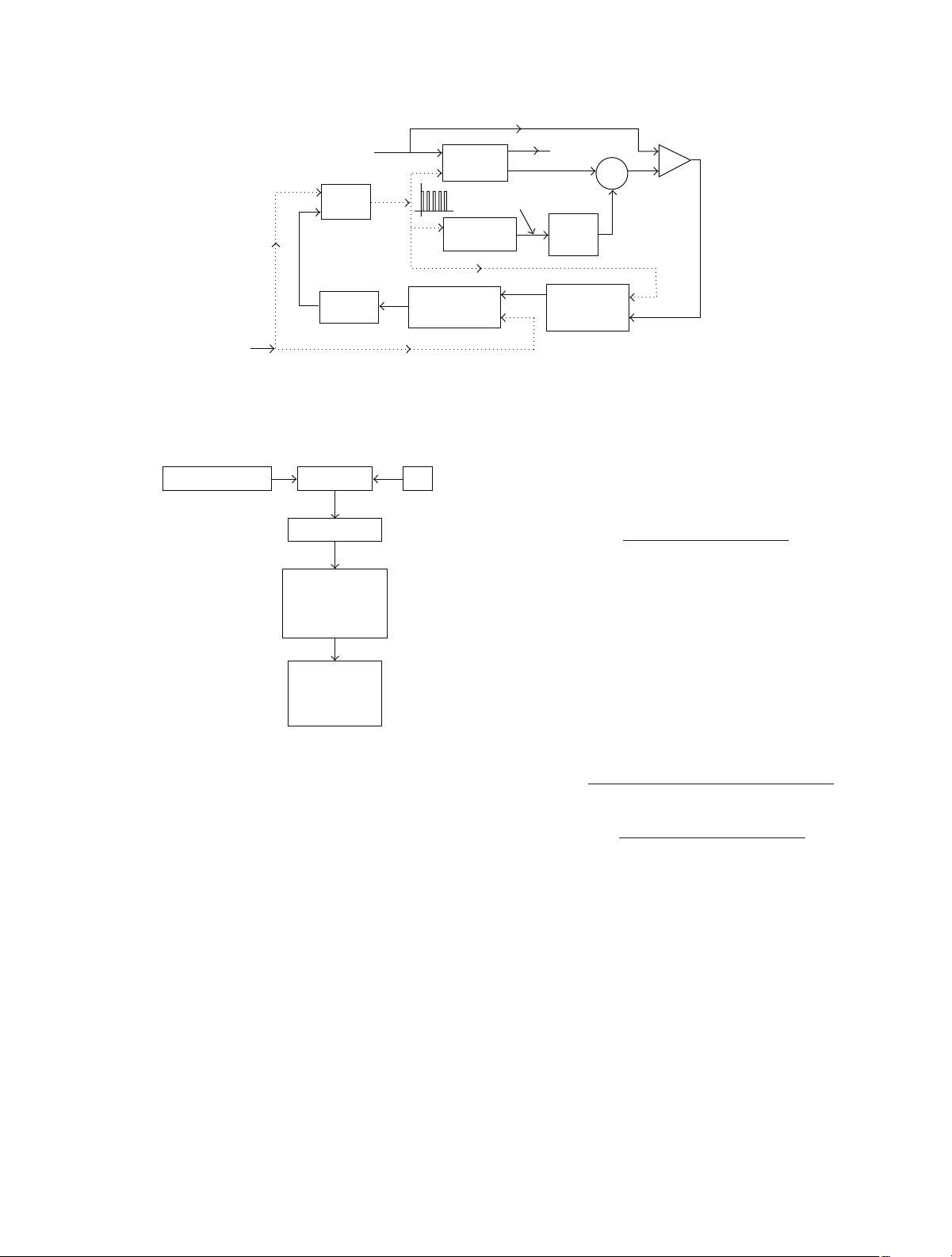

(Periodic signal)

Input

ena0

NCO

f

s

Sampling

pulses

Limiter

ena0

= 25.6kHz

PI controller

ena0

Moving

averager

ena

ena

Counter

Address

LUT

Cos

Cosine

Sine

SDFT

ena

Phase

detector

×

+

Figure 2: Block diagram of restructured phase-locking scheme.

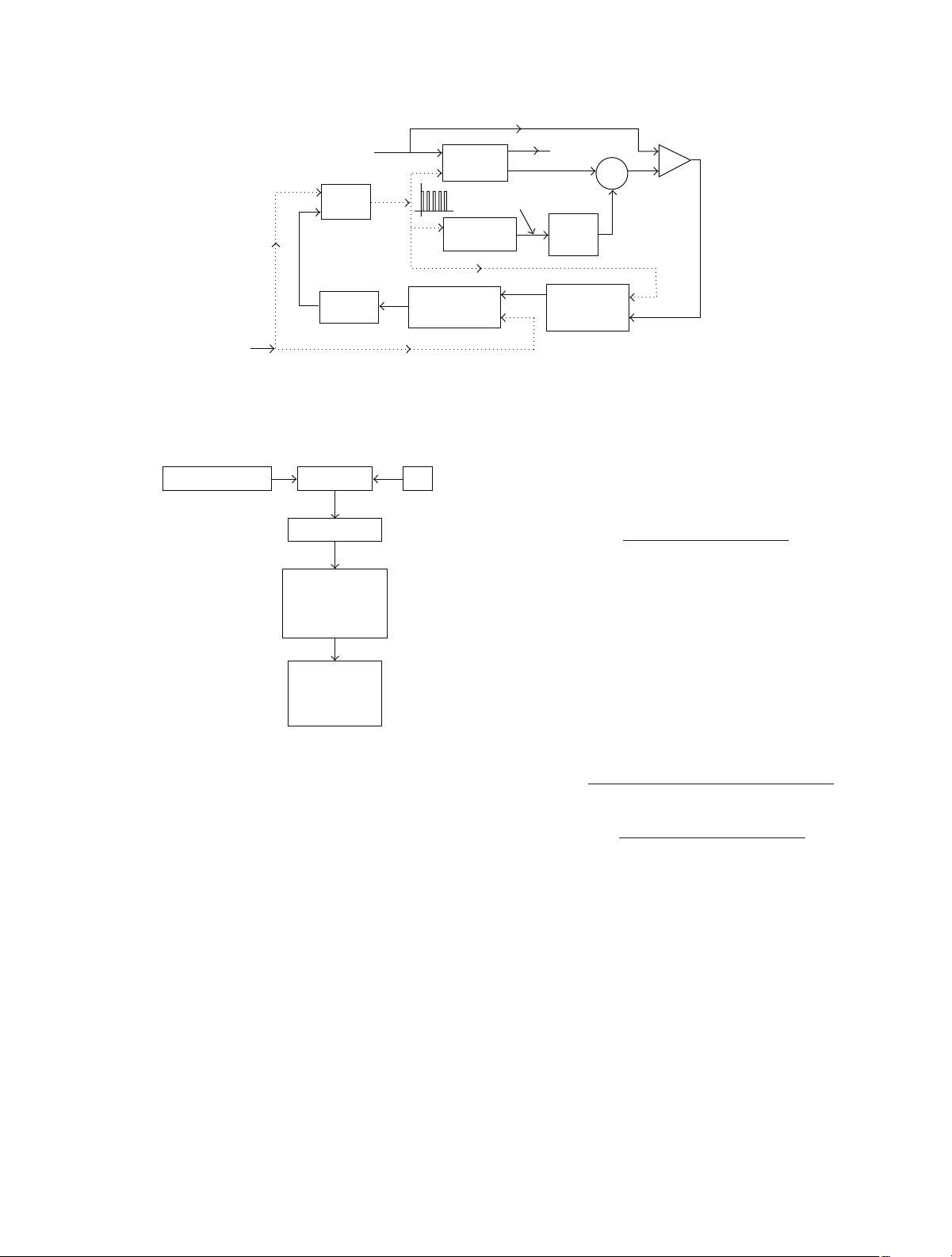

MATLAB/Simulink DSP builder

IP

Signal compiler

Ve r i l o g o r V H DL

.Tcl files to run

synthesis,

place, and route

Synthesis and

Quartus-II

software place

and route

Design in

MATLAB

/Simulink

Convert to

FPGA design

System verification

and construction

Figure 3: Synthesis flow of Matlab/Simulink-DSP builder and

Quartus-II.

signal from the LUT reduces the steady residual error present

in the control signal of the NCO [13]. The modification

results in the NCO output frequency becoming very accurate

compared to the simple integrated phase-locking scheme

(IPLL), and hence provides fine phase locking with the

fundamental component of the input signal.

2.1. DSP Builder-Quartus-II Tool. The MATLAB/Simulink-

DSP builder software had been used for realizing the

proposed Sliding DFT-based RPLL scheme. DSP Builder

signal compiler block reads Simulink model files (.mdl)

which are built using DSP builder and MegaCore blocks and

generates VHDL files and Tool command languages (.Tcl)

scripts for synthesis [14], hardware implementation, and

simulation. The synthesis flow of the DSP builder tool and

Quartus-II to generate the VHDL codes is shown in Figure 3.

The generated VHDL codes can be downloaded into FPGA

from PC through JTAG cable for processing.

2.2. Sliding DFT. The SDFT transfer function including the

damping factor “r” can be expressed as

H

k

(

z

)

=

1 − r

N

z

−N

z

−1

re

j2πk/N

1 − re

j2πk/N

z

−1

,

r<1,

[

k

= 0, 1, 2, 3, ..., N − 1

]

,

(1)

where k is the bin index, which can vary from 0 to N

− 1,

and N is the window width. The damping factor r<1

is introduced in the SDFT transfer function [15]toavoid

numerical instability. The in-phase and quadrature signals

can be obtained from SDFT block. For k

= 1, the SDFT can

extract the fundamental component present in the received

signal. The real and imaginary parts of the SDFT transfer

function can be written as

Re

[

H

1

(

z

)

]

=

1 − r

N

z

−N

z

−1

r cos

(

2π/N

)

− r

2

z

−1

1 − 2r cos

(

2π/N

)

z

−1

+ r

2

z

−2

,

Im

[

H

1

(

z

)

]

=

1 − r

N

z

−N

z

−1

(

r sin

(

2π/N

))

1 − 2r cos

(

2π/N

)

z

−1

+ r

2

z

−2

.

(2)

The block diagram realization of the SDFT transfer function

giveninequationin(1) is shown in Figure 4(a).Acomb

filter and a resonator are connected in cascade in the

SDFT structure. For the sake of clarity, bus-width and port

symbols were removed in the realization diagram shown in

Figure 4(a). The SDFT transfer function has N number of

zeros and a single pole lying on the unit circle in the z-

plane. For k

= 1, the single pole at z = e

j2π/N

cancels the

zero corresponding to that location. The SDFT is a tuned

filter, which passes only fundamental frequency present in

the input signal and rejects all other harmonics and d.c.

The pole-zero diagram of the SDFT is shown in Figure 4(b).

The damping factor r is chosen as 0.9997. For maintaining

the accuracy, a floating-point bit format of [2 : 18] (bus

width) has been used for the variables in the SDFT block.

The magnitude of the input signal is chosen small enough to

avoid over-flow.