EDA技术应用:Quartus II、状态机与VHDL实战

本文将深入探讨EDA(电子设计自动化)的各种程序和技术,包括Quartus II设计流程、传统电子电路设计与EDA设计的对比、VHDL的状态机设计、EDA技术的发展与应用、IP核概念及其应用、CPLD与FPGA的区别、EDA中的“综合”概念、VHDL的阻塞型与非阻塞型过程赋值语句的理解,以及Quartus II的功能仿真与时序仿真的差异。同时,通过示例代码展示了二选一选择器、3-8译码器和优先级编码器的设计。

在EDA领域,Quartus II是一款广泛使用的软件工具,其设计流程主要包括:创建项目、输入设计、编译、仿真、实现和下载。例如,在设计一个简单的二选一选择器时,我们可以使用VHDL编写实体和结构体,通过进程(PROCESS)根据输入信号`sel`的值来决定输出`q`是取`d0`还是`d1`。

传统的电子电路设计通常涉及手工绘制电路图和计算,而EDA设计则通过硬件描述语言(如VHDL或Verilog)实现,大大提高了设计效率和准确性。VHDL中的状态机设计方法允许开发者用行为描述的方式定义电路的行为,增强了代码的可读性和可维护性。

EDA技术的发展与应用已经涵盖了从IC设计到系统集成的各个层面,IP核( Intellectual Property Core)是其中的关键组成部分,它代表了预先验证过的、可重复使用的硬件模块。IP核的应用可以加速设计周期,降低风险。

CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)都是实现数字逻辑设计的平台,CPLD通常具有固定的互连结构和较少的可编程逻辑单元,适合小规模、固定功能的项目;而FPGA则拥有高度可配置的逻辑块和布线资源,适用于大规模、高性能的复杂设计。

EDA中的“综合”过程是将高级语言描述转化为逻辑门级网表的过程,它涉及到优化和映射策略。对于VHDL,理解阻塞型(<=)和非阻塞型(:=)过程赋值语句的区别至关重要,前者立即更新变量,后者则在当前进程结束时才更新。

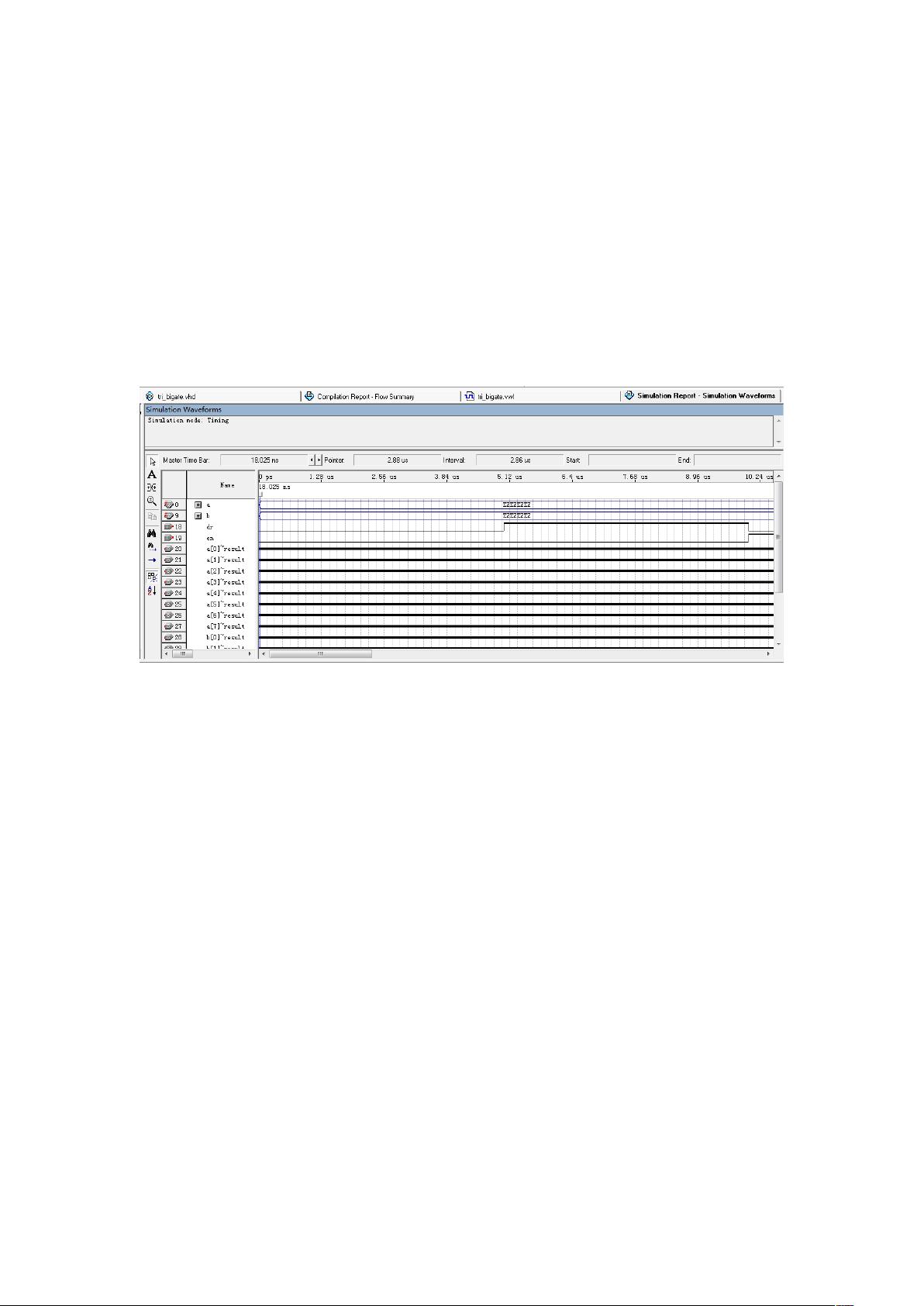

Quartus II提供了功能仿真(Functional Simulation)和时序仿真(Timing Simulation)两种验证手段。功能仿真关注设计逻辑的正确性,而时序仿真则考虑了实际时钟周期和延迟,更接近实际硬件行为。

最后,通过3-8译码器和优先级编码器的例子,我们可以看到如何用VHDL实现这些常见的数字逻辑电路。译码器通过CASE语句实现多路选择,优先级编码器则根据输入信号的优先级确定最高有效位的信号。

EDA技术通过各种程序和方法极大地推动了电子设计的自动化,降低了设计复杂度,提高了设计质量。无论是初学者还是经验丰富的工程师,理解和掌握这些知识点都是至关重要的。

2019-12-14 上传

2023-05-16 上传

2023-05-24 上传

2023-08-19 上传

2023-10-26 上传

2023-05-24 上传

2023-12-16 上传

shijiajian

- 粉丝: 0

- 资源: 1

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作