高性能全差分BiCMOS采样/保持电路设计

143 浏览量

更新于2024-08-30

收藏 274KB PDF 举报

"全差分BiCMOS采样/保持电路仿真设计"

在现代电子系统中,模数转换器(ADC)扮演着至关重要的角色,它作为数字和模拟信号之间的桥梁,广泛应用于各种领域,如通信、图像处理和数据采集等。ADC的性能直接影响到整个系统的精度和速度,而采样/保持(S/H)电路作为ADC的关键组成部分,其性能对ADC的整体效能至关重要。传统的S/H电路往往存在失真大和静态工作点不稳定的缺点,这对提高ADC的性能构成了挑战。

针对这些问题,研究者们提出了多种解决方案。文献[1]中设计了一种电荷翻转型S/H电路,然而忽略了开关的导通电阻对电路性能的影响,导致较大的信号失真。另一方面,文献[2]的S/H电路虽然考虑了开关的影响,但没有充分考虑全差分运算放大器(OPA)的共模输出电压对静态工作点稳定性的潜在影响。

为了解决这些问题,本设计采用了0.25微米的BiCMOS(双极-互补金属氧化物半导体)工艺,这是一种结合了双极晶体管高速特性和CMOS电路低功耗优势的技术,特别适合于高速、高精度的电路设计。基于这种工艺,设计了一款10位的全差分BiCMOS S/H电路,目标是实现更高的速率和精度。

电路设计中,关键改进包括自举开关电路和双通道开关电容共模反馈电路(CMFB)。自举开关设计可以减少开关导通电阻带来的失真,提高采样效率。双通道CMFB则有助于稳定静态工作点,抵消共模输出电压的影响,从而提高电路的共模抑制比(CMRR)和线性度。

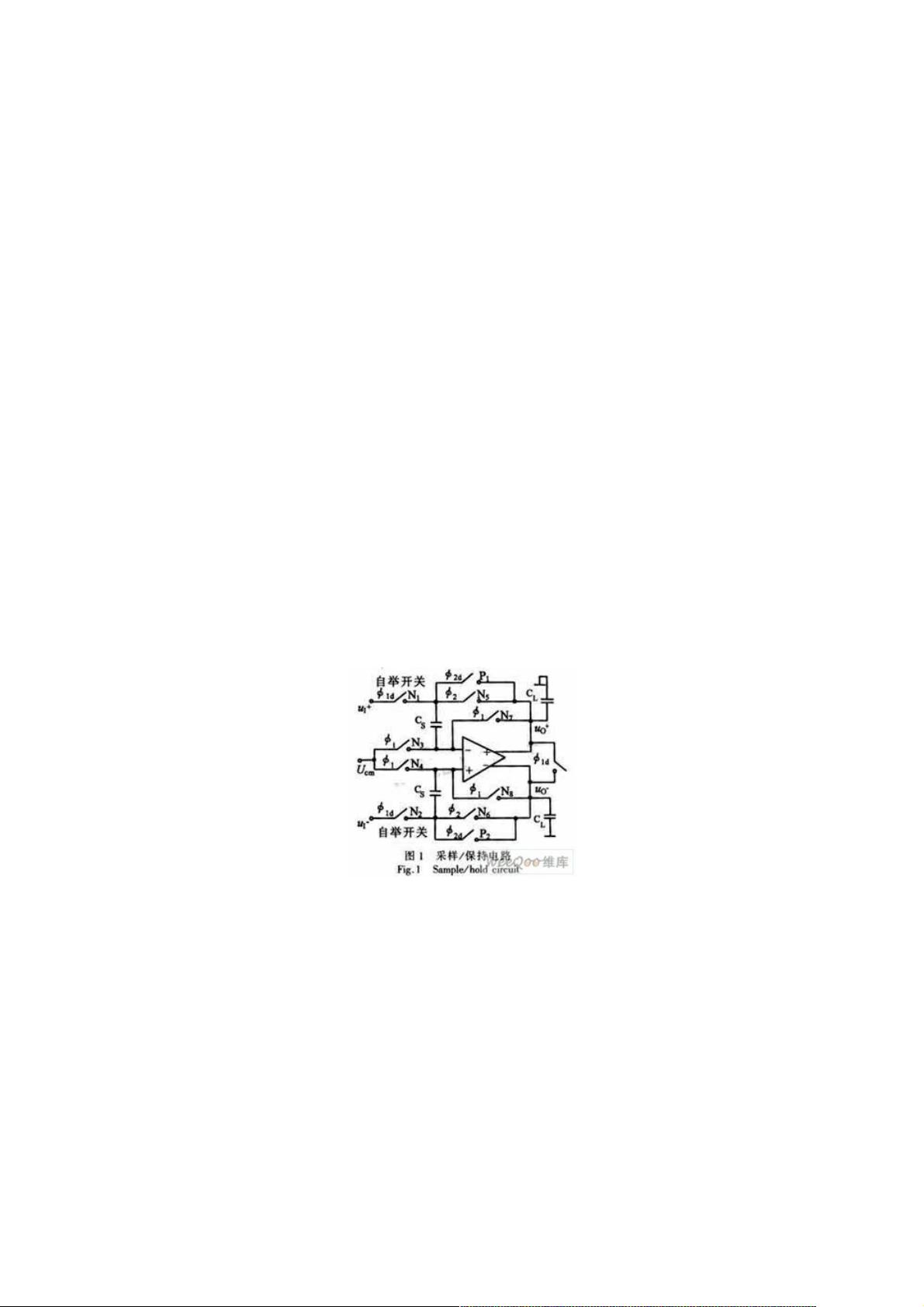

图1展示了S/H电路的基本结构,包括运放的共模输入电压Ucm,以及采用自举开关设计的N1和N2,以及NMOS开关N3到N8。在特定的时钟信号控制下,这些开关在采样和保持阶段交替工作。在采样阶段,输入电压uI通过电容CS被存储,而在保持阶段,电容CS通过反馈通道维持输出电压,保证输出端负载CL的稳定性。自举开关的使用使得UGS(开关管栅-源电压)与输入电压uI的关系能够被精确控制,如公式(1)所示,以优化线性响应和减少失真。

通过细致的仿真和优化,这款全差分BiCMOS S/H电路实现了高速和高精度的采样效果,为高性能ADC的设计提供了有力的支持。仿真结果和实际应用验证了该设计方案的有效性,表明了在解决传统S/H电路问题上的显著进步,为未来的ADC设计提供了新的思路和技术基础。

2020-11-07 上传

2021-01-19 上传

点击了解资源详情

2020-10-23 上传

点击了解资源详情

点击了解资源详情

2021-02-03 上传

2020-10-19 上传

点击了解资源详情

weixin_38675746

- 粉丝: 6

- 资源: 956