CPU流水线暂停机制设计与实现分析

需积分: 0 32 浏览量

更新于2024-08-04

收藏 271KB DOCX 举报

"这篇文档介绍了流水线暂停机制的设计与实现,主要关注于如何在CPU的流水线中实现暂停功能,以防止数据错误。文中提到了一个CTRL模块来控制流水线的暂停请求,并提供了相应的Verilog代码示例。"

在计算机体系结构中,流水线是一种优化处理器性能的技术,通过将指令的执行过程分解为多个连续的步骤,每个步骤在独立的硬件单元中并行处理,从而提高处理速度。然而,当遇到某些情况如分支、异常或特定指令需要多时钟周期完成时,流水线需要暂停以避免数据冲突和错误。本文档详细阐述了流水线暂停机制的设计和实现方法。

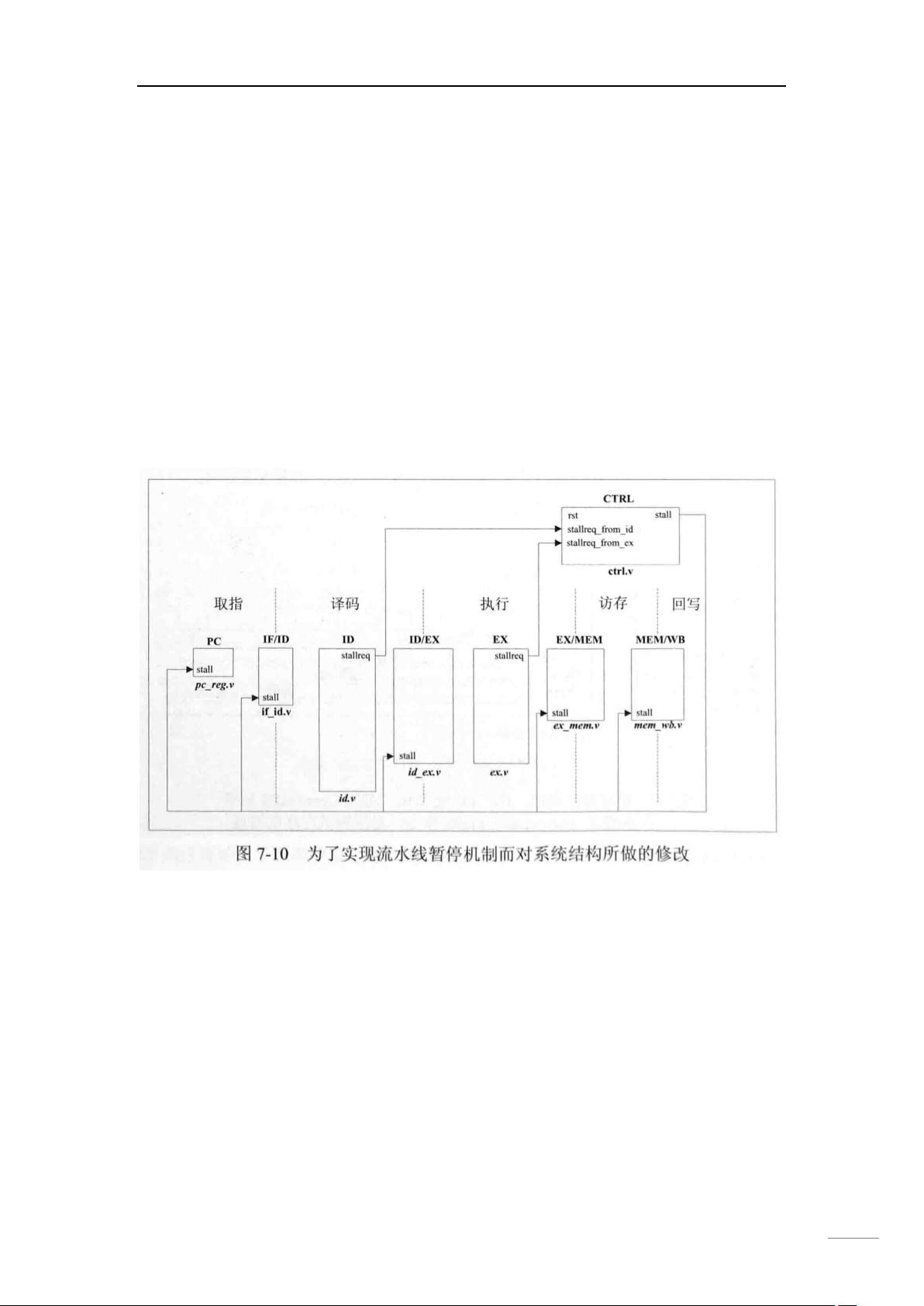

首先,设计思路是当某条指令在执行(EX)阶段需要暂停时,从这个阶段开始,前导阶段都要暂停,而后续阶段可以继续。这样可以防止新数据覆盖暂停指令的中间结果。为此,设计了一个名为CTRL的模块,该模块负责接收来自各个阶段的暂停请求信号,并根据这些请求控制流水线的运行状态。

CTRL模块的接口包括一个6位的`stall`信号,每个位对应流水线的不同阶段,如:

- `stall[0]`:表示PC是否保持不变,1表示不变;

- `stall[1]`:控制取值(ID)阶段是否暂停;

- `stall[2]`:控制译码(DE)阶段是否暂停;

- `stall[3]`:控制执行(EX)阶段是否暂停;

- `stall[4]`:控制访存(MEM)阶段是否暂停;

- `stall[5]`:控制回写(WB)阶段是否暂停。

CTRL模块的Verilog代码展示了如何根据来自ID和EX阶段的`stallreq`信号来设置`stall`的状态。当收到暂停请求时,会相应地设置`stall`的位,以指示流水线的哪些阶段应暂停。

接下来,文中提到了对PC(程序计数器)模块的修改,新增了与CTRL模块交互的`stall`接口。当接收到CTRL模块的暂停信号时,PC模块会停止递增,保持当前地址,直到暂停解除。

流水线暂停机制的关键在于正确地控制不同阶段的暂停和恢复,确保在不影响性能的前提下,能够准确处理那些需要额外时钟周期的指令。这种机制对于现代处理器来说至关重要,因为它可以在不影响大部分指令执行的同时,处理复杂的情况,如分支预测、异常处理以及多周期指令的执行。

2008-04-05 上传

2014-07-14 上传

2011-06-07 上传

2023-06-06 上传

2023-04-12 上传

2023-06-06 上传

2023-06-12 上传

2023-05-28 上传

2023-06-10 上传

2023-06-28 上传

WaiyuetFung

- 粉丝: 385

- 资源: 316

最新资源

- 多传感器数据融合手册:国外原版技术指南

- MyEclipse快捷键大全,提升编程效率

- 从零开始的编程学习:Linux汇编语言入门

- EJB3.0实例教程:从入门到精通

- 深入理解jQuery源码:解析与分析

- MMC-1电机控制ASSP芯片用户手册

- HS1101相对湿度传感器技术规格与应用

- Shell基础入门:权限管理与常用命令详解

- 2003年全国大学生电子设计竞赛:电压控制LC振荡器与宽带放大器

- Android手机用户代理(User Agent)详解与示例

- Java代码规范:提升软件质量和团队协作的关键

- 浙江电信移动业务接入与ISAG接口实战指南

- 电子密码锁设计:安全便捷的新型锁具

- NavTech SDAL格式规范1.7版:车辆导航数据标准

- Surfer8中文入门手册:绘制等高线与克服语言障碍

- 排序算法全解析:冒泡、选择、插入、Shell、快速排序