FPGA实现的可调DDS信号发生器设计与详解

需积分: 9 165 浏览量

更新于2024-07-27

2

收藏 2.5MB PPT 举报

本资源主要介绍了一项关于基于FPGA的DDS信号发生器的设计与实现项目,作为电子系统综合设计课程的一部分,旨在让学生掌握FPGA设计流程、VHDL编程以及DDS(Direct Digital Synthesis,直接数字合成)原理。以下是关键知识点的详细解析:

1. 实验背景与目标:

- 该课程项目提供了三个实验课题供选择,其中重点是基于FPGA的DDS信号发生器。目的是让学生通过实际操作理解FPGA设计流程,熟悉VHDL语言,并能设计出能够输出可变频率(5Hz-100kHz)正弦波的DDS信号发生器,频率步进值小于1Hz。

2. 设备与资源需求:

- 实验需要的主要设备包括PC机、Quartus II软件和DE2开发板。这些工具在设计过程中起到至关重要的作用,如设计、编程和硬件仿真。

3. 实验内容与要求:

- 实验要求学生设计一个DDS信号发生器,输出正弦波的频率与频率控制字M和相位控制字P相关。具体任务包括绘制顶层逻辑图,分析频率精度与控制字的关系,评估FPGA资源利用率,提供模块仿真时序图以及详细的程序代码。

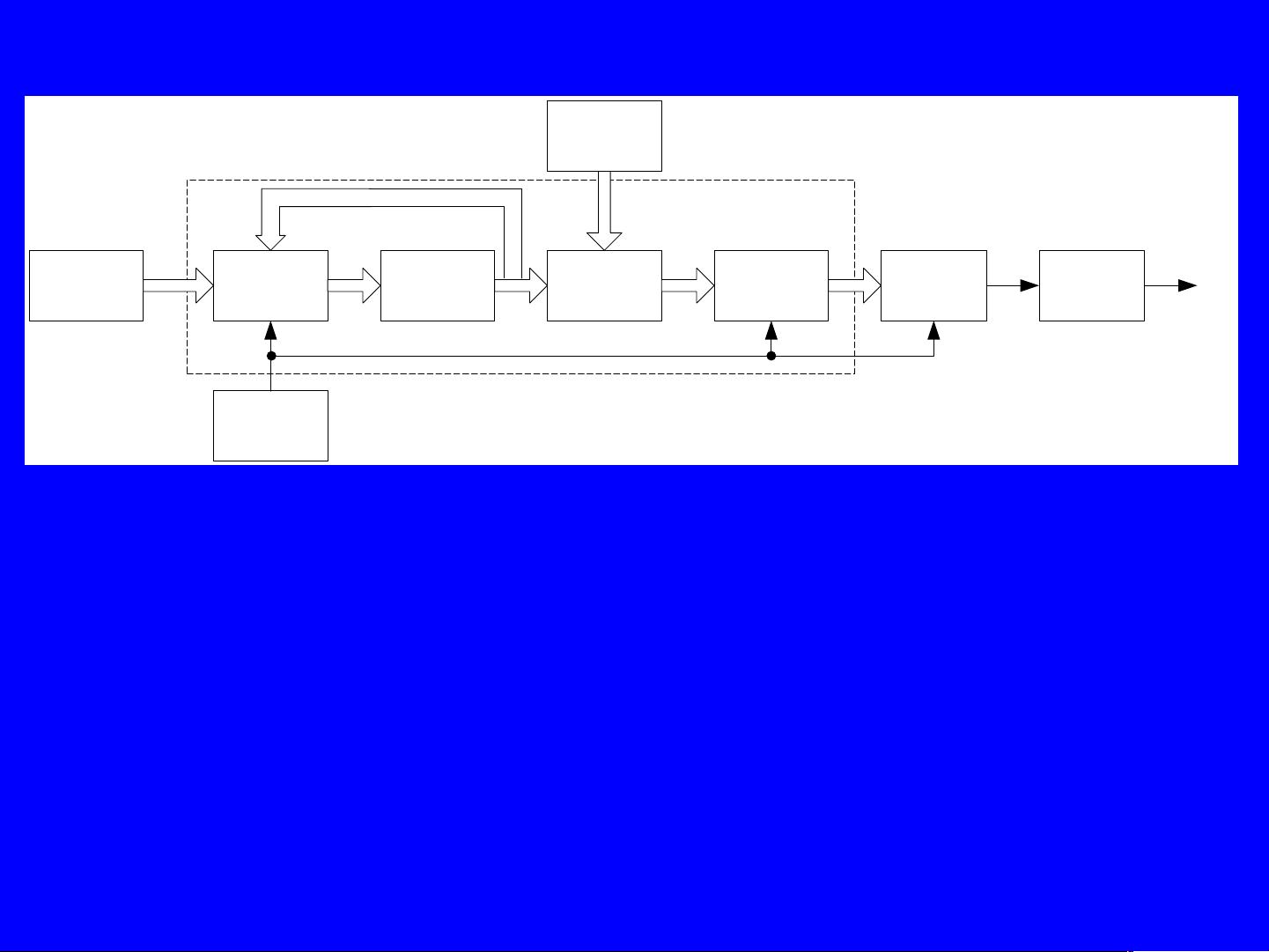

4. 设计原理:

- DDS信号发生器的核心是相位累加器,它通过累加器和相位寄存器工作,相位寄存器按照频率控制字M的步长更新。正弦波的频率由M和相位寄存器的位数N决定,最小分辨率随M和N的关系而变化。当M等于2N-1时,可以获得最高基波合成频率。

5. 方案论证与详细设计:

- 学生需要在报告中详细阐述设计方案,包括设计流程、模块划分、数据结构的选择以及如何确保正弦波的纯度。此外,文档格式规范要求使用特定字体和字号,图形需用Visio绘制并附带图名和图号。

6. 系统调试与仿真:

- 实验成果需要通过系统调试和硬件仿真验证,确保输出的正弦波符合设计规格。同时,报告中应包含调试过程中的发现和改进思路。

通过这个项目,学生不仅能提升FPGA设计技能,还能深入理解DDS信号生成的原理,培养理论与实践相结合的能力。

2008-12-07 上传

2010-11-26 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

ASD569965

- 粉丝: 1

- 资源: 1

最新资源

- 掌握Jive for Android SDK:示例应用的使用指南

- Python中的贝叶斯建模与概率编程指南

- 自动化NBA球员统计分析与电子邮件报告工具

- 下载安卓购物经理带源代码完整项目

- 图片压缩包中的内容解密

- C++基础教程视频-数据类型与运算符详解

- 探索Java中的曼德布罗图形绘制

- VTK9.3.0 64位SDK包发布,图像处理开发利器

- 自导向运载平台的行业设计方案解读

- 自定义 Datadog 代理检查:Python 实现与应用

- 基于Python实现的商品推荐系统源码与项目说明

- PMing繁体版字体下载,设计师必备素材

- 软件工程餐厅项目存储库:Java语言实践

- 康佳LED55R6000U电视机固件升级指南

- Sublime Text状态栏插件:ShowOpenFiles功能详解

- 一站式部署thinksns社交系统,小白轻松上手