FPGA面试必备:同步异步逻辑解析及笔试重点

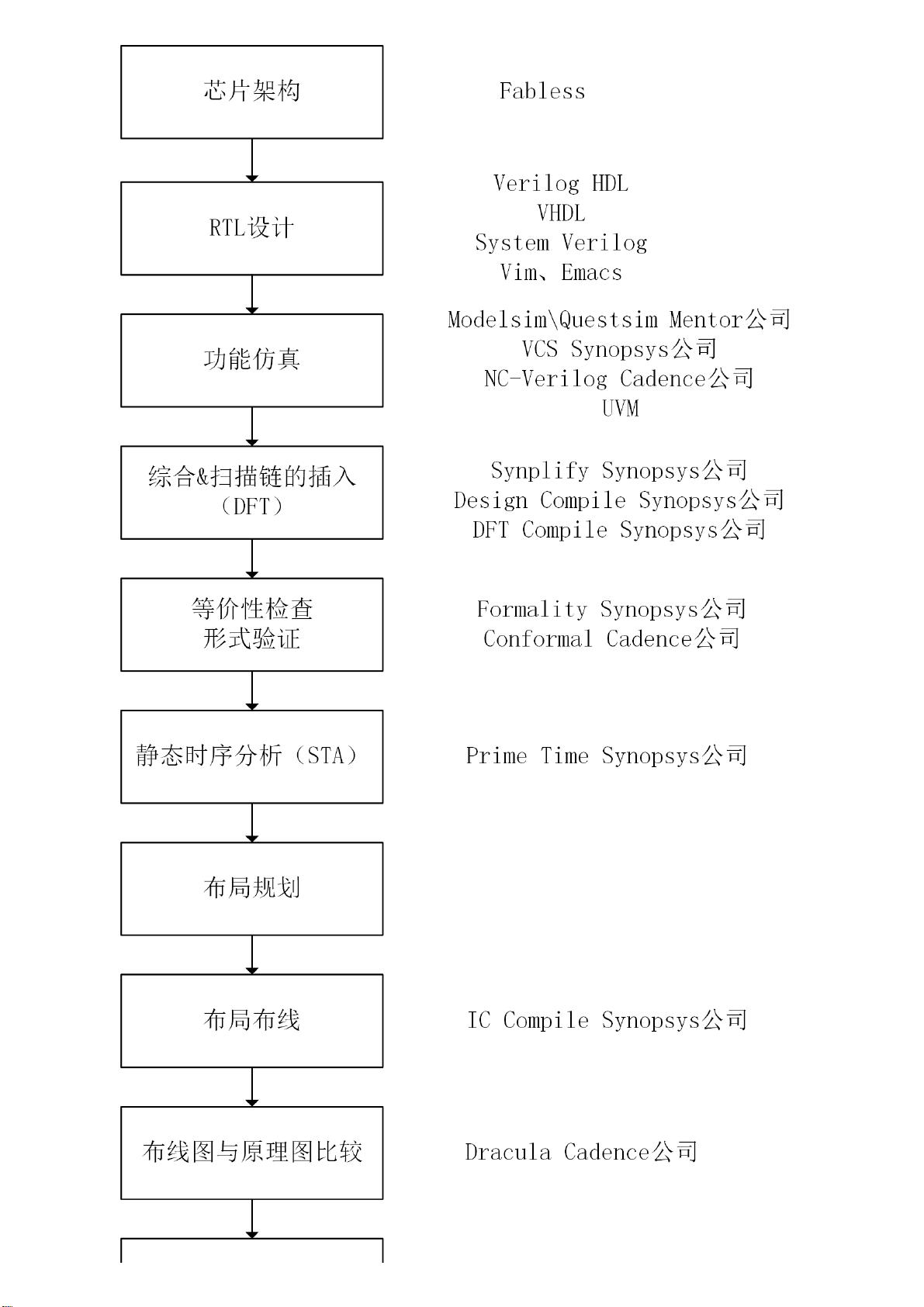

"FPGA面试题集,包含数字IC和FPGA开发的相关问题" 这篇内容主要汇总了一些关于FPGA和数字集成电路面试中常见的技术问题,尤其是关于同步逻辑和异步逻辑、时序设计等方面的知识点。 1. **同步逻辑与异步逻辑**: - 同步逻辑是指电路中的所有时序元件(如触发器)共享同一个时钟信号,它们的状态变化严格遵循时钟的节奏。这样的设计使得电路的行为更加稳定和可预测。 - 异步逻辑则不依赖于单一的全局时钟,各个组件可能有各自独立的时钟或者不使用时钟,状态的改变由输入信号的直接变化驱动。这可能导致复杂性和不确定性增加。 2. **同步电路与异步电路的区别**: - 同步电路的所有触发器都由同一个时钟信号控制,确保所有操作在同一时钟周期内完成,提高了电路的一致性和可预测性。 - 异步电路中,不同触发器可能有不同的时钟源,它们的状态变化可能不同时发生,增加了设计的复杂度和潜在的错误来源。 3. **时序设计的实质**: - 时序设计是FPGA设计中的关键环节,它主要关注如何确保每个触发器在正确的时间接收正确的数据,以满足建立时间和保持时间的要求,避免触发器进入亚稳态。 4. **建立时间与保持时间**: - 建立时间是指在时钟边缘到来前,数据输入必须保持稳定的时间长度,以保证触发器能够正确捕捉输入信号。 - 保持时间则是指在时钟边缘后,数据输入必须保持不变的时间,以防止在触发器处理数据的过程中发生错误。 5. **建立时间和保持时间的重要性**: - 不满足这两个时间要求可能导致触发器进入亚稳态,即输出处于不稳定状态,可能会在0和1之间随机跳变。这种状态需要一定时间才能恢复,而且恢复后的值可能与原始输入不一致,从而影响整个系统的功能。 6. **亚稳态的解决**: - 为了避免亚稳态的传播,通常会使用两级触发器结构,确保异步输入信号经过第一级触发器的转换后,在第二级触发器之前达到稳定,以满足下一级的建立和保持时间要求。 这些知识点在FPGA和数字IC的面试中至关重要,理解并掌握它们是成为一名合格的数字IC或FPGA开发者的基础。通过深入学习和实践,可以进一步提升设计能力和解决实际问题的能力。在准备面试时,求职者应当对这些问题有深入的理解,并能够应用到实际设计场景中。

剩余118页未读,继续阅读

- 粉丝: 191

- 资源: 12

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 构建Cadence PSpice仿真模型库教程

- VMware 10.0安装指南:步骤详解与网络、文件共享解决方案

- 中国互联网20周年必读:影响行业的100本经典书籍

- SQL Server 2000 Analysis Services的经典MDX查询示例

- VC6.0 MFC操作Excel教程:亲测Win7下的应用与保存技巧

- 使用Python NetworkX处理网络图

- 科技驱动:计算机控制技术的革新与应用

- MF-1型机器人硬件与robobasic编程详解

- ADC性能指标解析:超越位数、SNR和谐波

- 通用示波器改造为逻辑分析仪:0-1字符显示与电路设计

- C++实现TCP控制台客户端

- SOA架构下ESB在卷烟厂的信息整合与决策支持

- 三维人脸识别:技术进展与应用解析

- 单张人脸图像的眼镜边框自动去除方法

- C语言绘制图形:余弦曲线与正弦函数示例

- Matlab 文件操作入门:fopen、fclose、fprintf、fscanf 等函数使用详解

信息提交成功

信息提交成功