FPGA时序优化策略详解:全面指南与常见问题解决

需积分: 32 13 浏览量

更新于2024-07-22

1

收藏 3.06MB PDF 举报

FPGA时序优化策略是设计高效、高性能FPGA系统的关键步骤,它涉及到理解和应用一系列技术和方法来确保设计满足速度和功能的需求,同时避免时序冲突。本文档是针对Altera公司的Quartus II软件设计系列,特别是关于优化技术中的时序优化部分,提供了宝贵的指导。

首先,时序优化的通用建议包括:

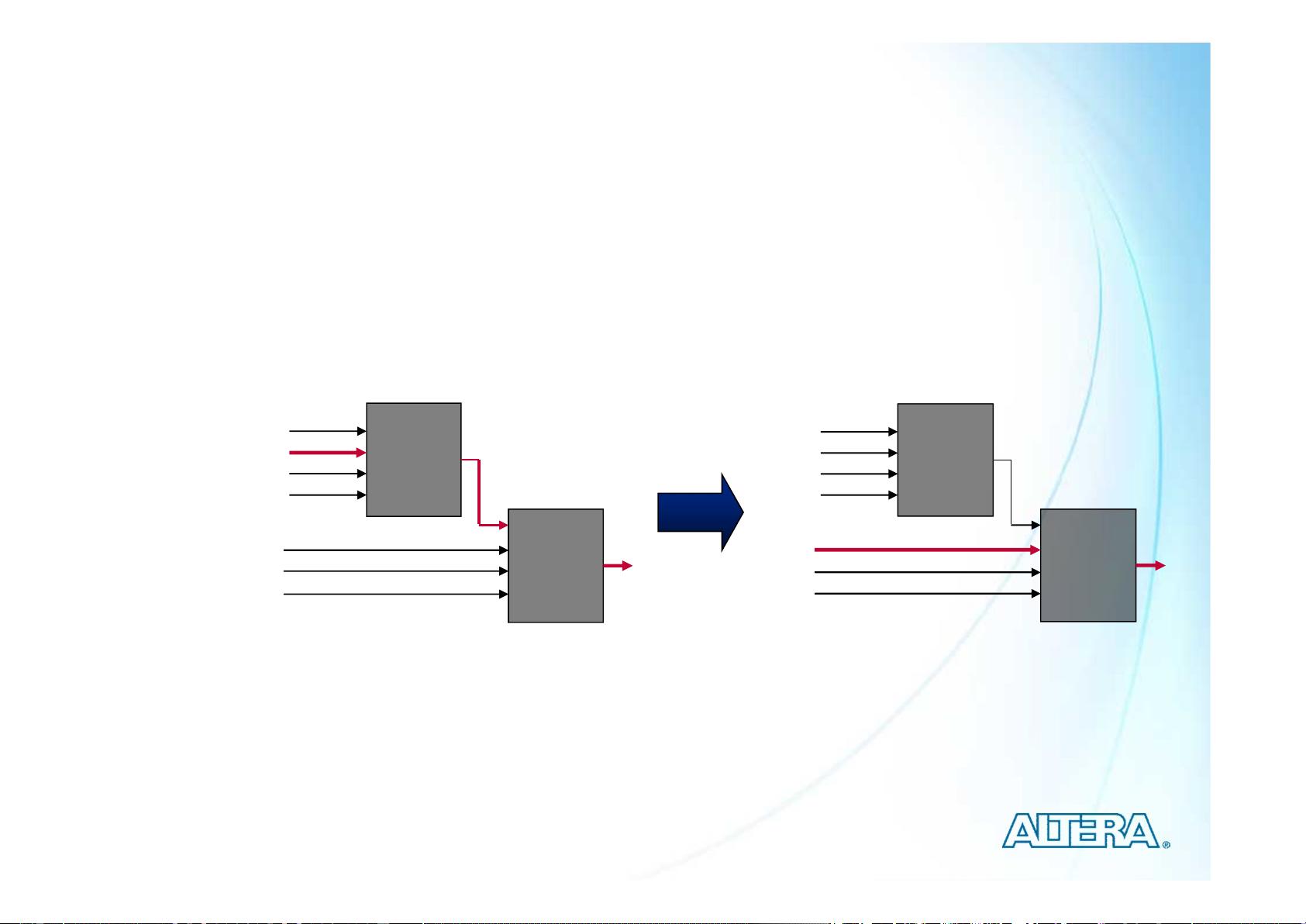

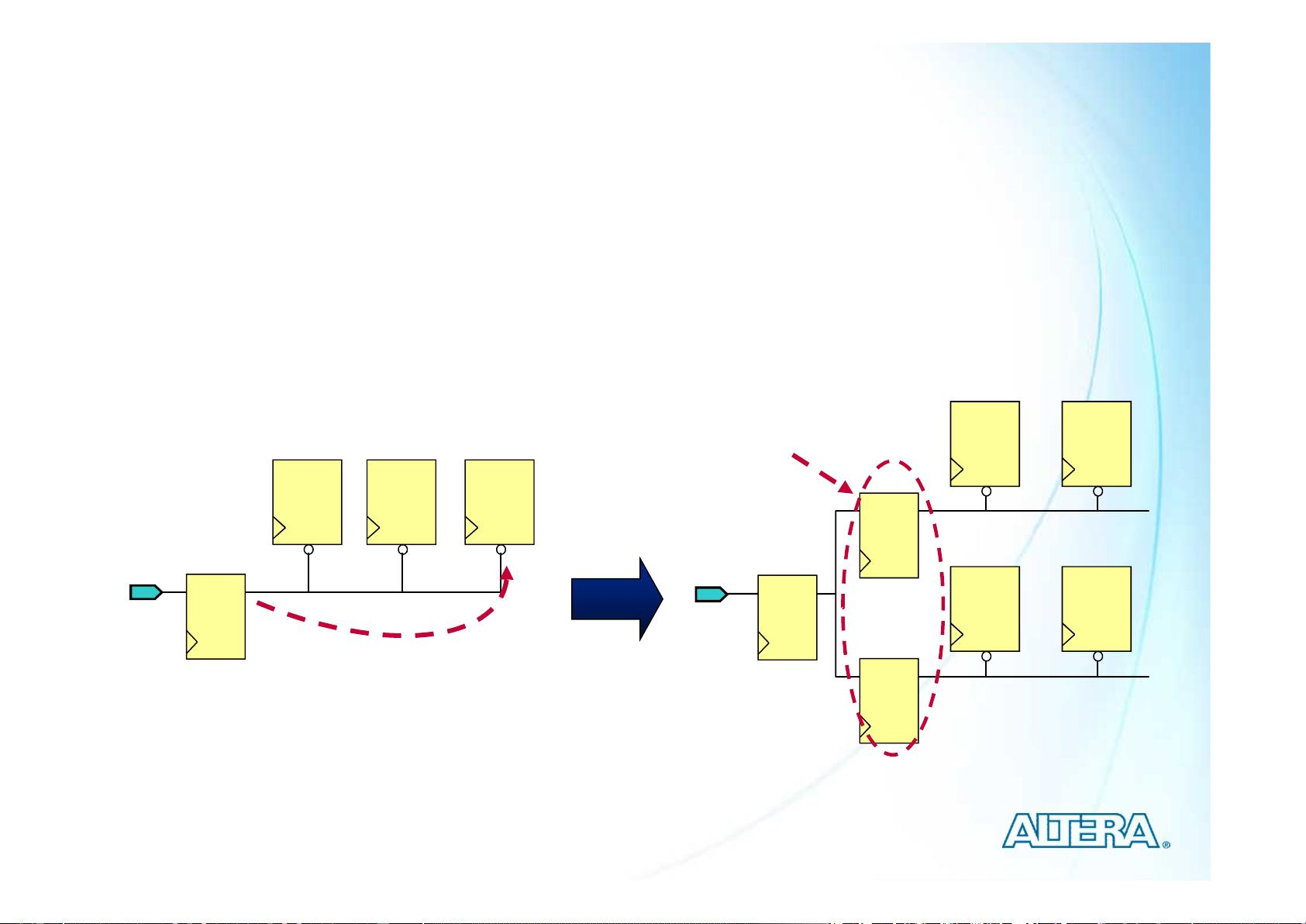

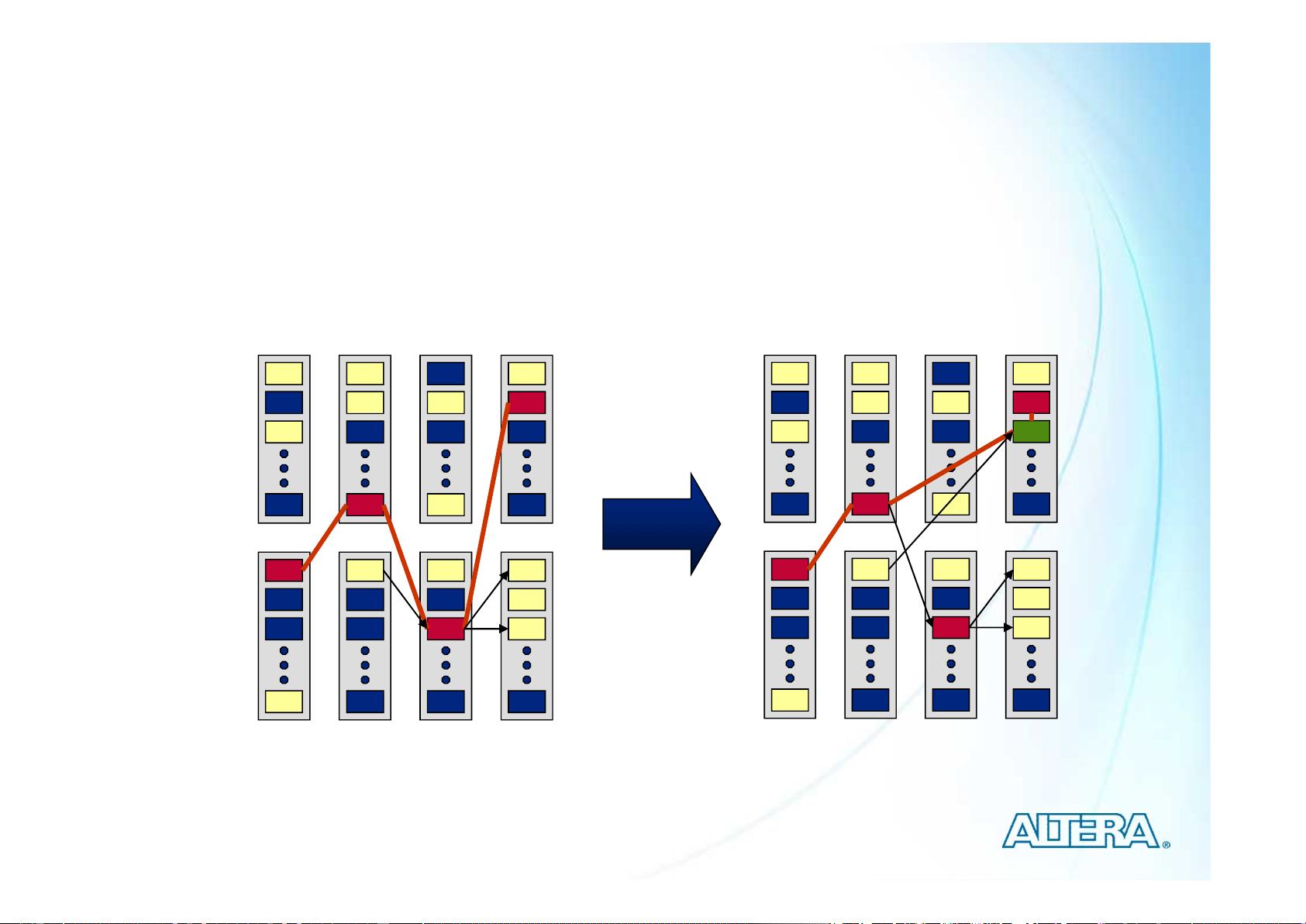

1. **钟(Clocks)**:优化设计时要考虑全局速度,这意味着选择合适的时钟频率并确保所有模块同步到主时钟。钟的设计应采用层次结构方法,从顶层到底层逐级进行。同时,启用网表优化和物理合成等高级工具,以提高性能和降低延迟。

- **全局优化**:通过调整系统时钟,减少整体延迟,提升设计的性能。

- **层次化优化**:在设计层次结构中,每个层次的时钟应该独立设置,根据需求提供不同的时钟速率。

- **特定时钟域**:针对不同功能区域或子系统,可能需要独立的时钟域,以避免信号传播时的延迟问题。

2. **输入/输出(I/O)**:I/O接口的时序特性也至关重要,需要确保数据传输速率与I/O引脚的驱动能力和负载相匹配,以防止数据丢失或错误。

3. **异步控制信号(Asynchronous Control Signals)**:避免在时序关键路径上使用异步信号,因为它们可能会引入不确定性。如果必须使用,需仔细设计和管理。

文档还提到了利用工具如**Timing Optimization Advisor**和**Quartus II Handbook**中的建议,这些工具能帮助识别和解决常见的时序问题,如过时的延时、扇出限制超出、时钟树分析等。

FPGA时序优化策略是设计师在设计流程中不可忽视的重要环节,它涵盖时钟网络的优化、接口管理、信号处理等多个层面,目的是确保设计能够在满足功能的同时,达到预期的性能和可靠性。通过遵循这些策略,设计师可以有效提高FPGA系统的效率和稳定性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-09-25 上传

2021-07-13 上传

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2018-10-30 上传

fcc2008

- 粉丝: 55

- 资源: 242

最新资源

- AMD-1.1-py3-none-any.whl.zip

- Business::Associates-开源

- 自己编的进度条VC代码IProgDlg

- jjk-mvvm-demo

- vue.js_dynamic_table:用Vue.js编写的单页应用程序,用于演示如何使用动态表(添加,编辑和删除元素)

- BlocksGame

- AMQPStorm-2.7.1-py2.py3-none-any.whl.zip

- boat-java:一个简单的 Java 程序,使用 Boats 说明类继承

- screenshot upload tool-开源

- gotta-go-fast-vim:适用于vim的语言不可知入门套件

- flutter_intro:Flutter专案的新功能介绍和逐步使用者指南的更好方法

- YFreeSoftware:一个 Android 应用程序,让人们知道专有应用程序可以在未经用户许可的情况下获取哪些信息

- AMQPEz-1.0.0-py3-none-any.whl.zip

- RDF Editor in Java-开源

- 51系列密码锁:Proteus仿真+Keil程序

- tallermecanico.github.io