使用Virtex-4 FPGA实现DDR2控制器

需积分: 4 69 浏览量

更新于2024-09-23

收藏 306KB PDF 举报

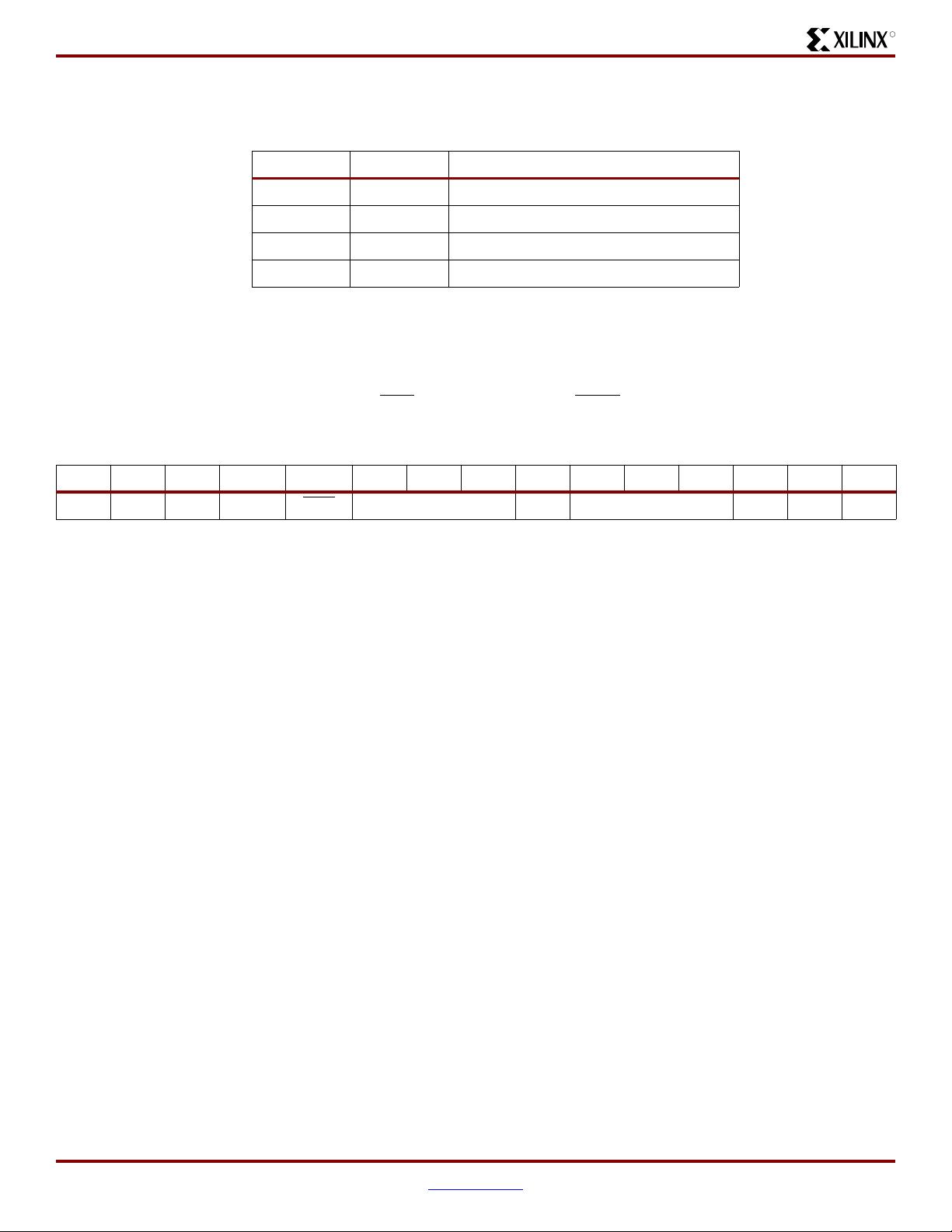

"DDR2 Controller Using Virtex-4 Devices 是一篇技术文档,主要讨论如何利用Xilinx公司的Virtex-4系列FPGA实现对DDR2 SDRAM(Double Data Rate Second Generation Synchronous Dynamic Random Access Memory)的读写控制。文档可能包含详细的设计原理、配置方法、时序分析以及在实际应用中的注意事项。Xilinx是一家著名的 FPGA 厂商,其Virtex-4系列是当时较为先进的FPGA产品,适用于高性能计算和嵌入式系统设计。DDR2内存技术相比第一代DDR有更高的数据传输速率和更低的功耗,是当时主流的内存解决方案。该文档可能是Xilinx官方发布的应用笔记XAPP702的1.8版本,日期为2007年4月23日,旨在帮助开发者有效地利用Virtex-4 FPGA来设计DDR2控制器。"

DDR2 SDRAM是第二代同步动态随机存取内存,其主要特点包括双倍数据速率(DDR),即在时钟周期的上升沿和下降沿都能传输数据,显著提高了数据传输速度。相对于DDR,DDR2还引入了更精细的时钟管理,如八 bank 结构和更小的CAS延迟(CL),从而进一步提升了性能。此外,DDR2通过降低工作电压(1.8V相对于DDR的2.5V),降低了系统功耗。

在使用Virtex-4 FPGA实现DDR2控制器时,设计者需要关注以下几个关键点:

1. **时序设计**:DDR2的高速特性要求控制器必须精确地控制地址、命令和数据的时序,确保与内存芯片的接口同步。这通常需要深入理解DDR2的时序规范,并在FPGA逻辑中实现相应的定时约束。

2. **接口协议**:FPGA需要提供适当的接口信号,包括时钟、地址、命令、数据和控制信号。这些信号需要在正确的时间点有效,以满足DDR2的协议要求。

3. **控制器逻辑**:Virtex-4 FPGA内部的逻辑资源(LUTs、FFs等)用于构建DDR2控制器,负责产生必要的控制信号,管理和调度内存访问请求。

4. **时钟管理**:由于DDR2的数据传输依赖于复杂的时钟同步,因此设计中可能需要使用FPGA的锁相环(PLL)或分频器(DLL)来生成正确的时钟信号。

5. **电源管理**:由于DDR2的工作电压较低,设计时应考虑FPGA的电源配置,以确保兼容性并减少功耗。

6. **IP核使用**:Xilinx可能提供了预验证的DDR2控制器IP核,可以直接集成到设计中,简化开发过程。

7. **测试与验证**:设计完成后,需要进行详尽的仿真和硬件测试,确保控制器在各种条件下均能正确运行,无错误传输数据。

8. **合规性**:由于文档中提到的免责声明,开发者在使用该设计时需要确保不侵犯任何专利权,并自行负责实施的合法性。

"DDR2 Controller Using Virtex-4 Devices"这篇文档将为FPGA开发者提供有关如何高效、可靠地在Virtex-4平台上设计DDR2内存控制器的详细指南,涵盖设计、实现、测试和合规性等多个方面。

2010-05-08 上传

2013-03-07 上传

2014-06-19 上传

2022-07-15 上传

2009-03-12 上传

2014-06-19 上传

2008-10-29 上传

2013-09-02 上传

jncarol

- 粉丝: 0

- 资源: 1

最新资源

- 低通滤波和同态滤波hm3.zip

- traffic-ha-rss:Android 道路交通应用程序,可从公路局 RSS 提要中提取数据并将其显示为基于 RecyclerView 的列表和 Google 地图

- Huawei.7zHuawei.7z

- ant-design-vue-4.0.0-beta.3.zip

- 原有房屋_csdn

- 该设计用于超声波成像系统的八个 16 通道接收 AFE IC 供电-电路方案

- 单片机数据发送程序-综合文档

- Excel-VBA实用技巧范例-利用文件对象模型FSO操作驱动器.zip

- node-v0.10.45.tar.gz

- 实现视网膜断层图中Vitreous、NFL、GCL、INL、OPL、ONL、OS、RPE八层的图像分割识别+代码操作视频

- laravel-dropbox-driver:Dropbox的存储扩展

- 设备安装工程施工组织设计-香格里拉酒店机电安装施工组织设计

- ant-design-vue-3.3.0-beta.3.zip

- slic_reg:重新考虑使用可变形超级体素的基于学习者的患者间注册的设计(MIDL 2021)

- proximitysensorlocker

- 基于Python实现的直播念弹幕脚本 + 直播发弹幕脚本