FPGA实现4位七段数码管动态显示系统

"4位七段数码管动态显示系统设计基于FPGA实现,采用VHDL编程语言,通过LED显示接口实现数据或工作状态的显示。动态显示技术节省了 FPGA 引脚资源,利用视觉暂留效应达到多数码管同时显示的效果,并能有效降低功耗。控制电路的关键在于数码管间的延时控制,合适的延时既能避免闪烁,又能实现不同的显示效果。"

在电子设计领域,4位七段数码管动态显示系统是一种常见的显示解决方案,尤其在单片机应用系统中用于人机交互。这个系统的设计主要集中在如何在有限的硬件资源下实现高效的显示功能。FPGA(Field-Programmable Gate Array),作为一种可编程逻辑器件,因其灵活性和并行处理能力,成为了实现这种复杂显示系统的理想选择。

VHDL(VHSIC Hardware Description Language)是硬件描述语言,用于设计和描述数字系统的逻辑行为。在这个设计中,VHDL 被用来编写LED显示接口的代码,控制LED数码管的亮灭状态,以显示所需的信息。LED显示器通常由8段组成,分为共阴极和共阳极两种类型,它们的控制原理在于通过改变各段的电压状态来点亮或熄灭对应的段,从而组合成各种数字和字母。

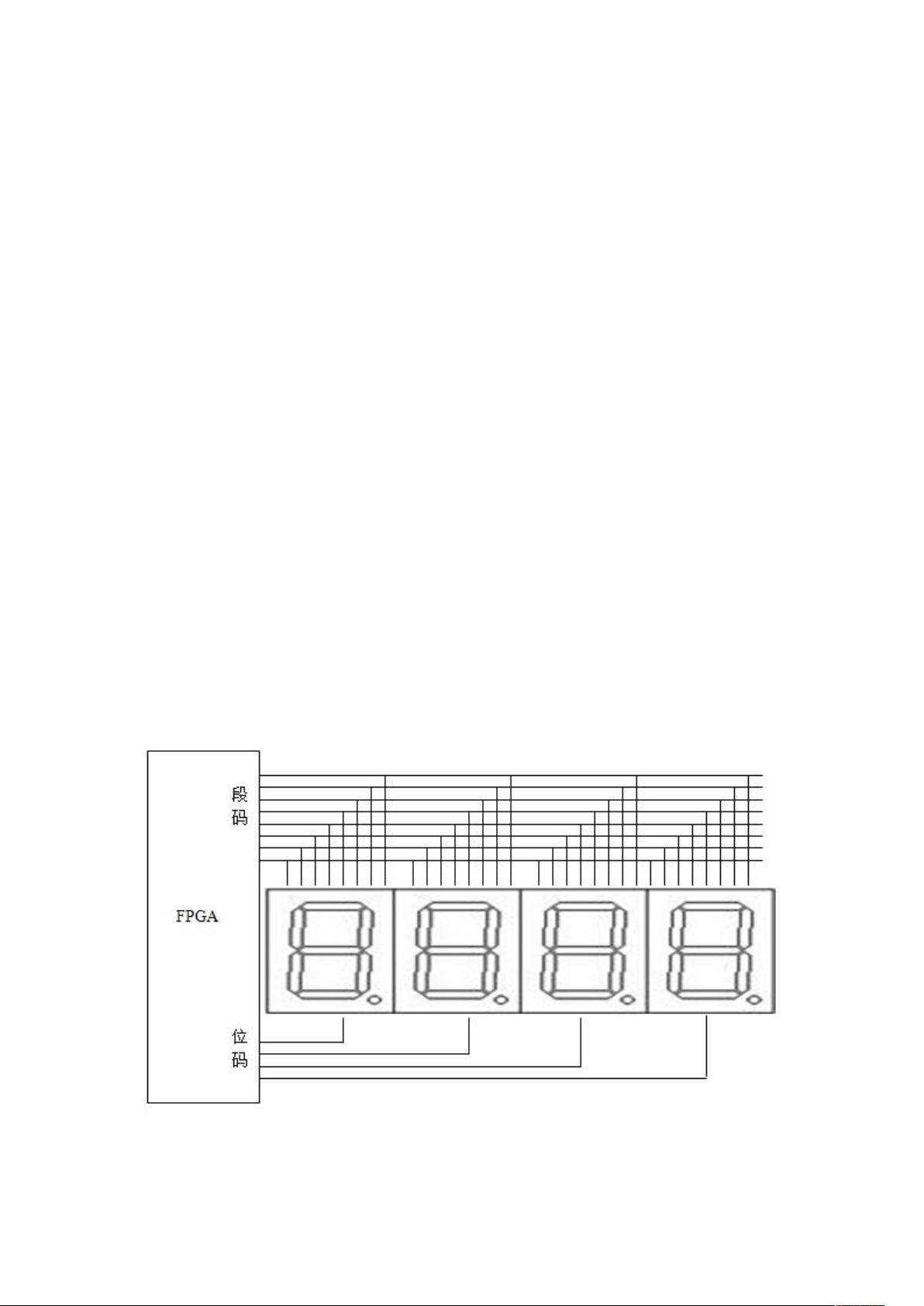

动态显示策略是解决多个LED数码管显示问题的有效方法。在静态显示中,每个数码管需要8条控制线,对于4位数码管就是32条线,这在资源有限的FPGA上是不可接受的。动态显示则通过轮流点亮每个数码管并快速切换,利用人眼的视觉暂留现象,使人感觉所有数码管同时亮起。图3.8所示的控制电路展示了这一机制,其中片选信号用于选择当前要显示的数码管,数据则在选定的数码管上写入。

关键在于控制数码管的导通时间,即延时。理想的延时应足够短,使得每秒至少刷新16次,这样人眼无法察觉到闪烁,但又不能过短,以免影响LED的亮度。通常0.005秒的延时可以提供良好的显示效果。延时的调整还可以产生不同的显示效果,例如延长延时可以实现数码管逐个显示,增加了视觉趣味性。

4位七段数码管动态显示系统的设计与FPGA实现是一项结合了硬件逻辑设计、VHDL编程和视觉心理学的工程任务。通过精心设计的控制逻辑和恰当的延时控制,可以在有限的硬件资源下实现高效、稳定且节能的显示系统。这种技术广泛应用于各种嵌入式系统和仪表设备中,为用户提供直观的系统状态信息。

175 浏览量

2022-08-03 上传

2021-12-14 上传

点击了解资源详情

2020-12-24 上传

2022-07-09 上传

window1115

- 粉丝: 0

- 资源: 1

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常