FPGA实现:七段数码管动态显示IP设计与解析

需积分: 12 169 浏览量

更新于2024-07-23

收藏 717KB PDF 举报

【资源摘要信息】: "七段数码管动态显示IP的研究及设计主要关注FPGA中的七段数码管显示技术,特别是Seg7_ControllerIP的设计与实现。该IP用于驱动八位七段数码管进行动态显示,通过Avalon-MM接口与系统交互,并提供了详细的硬件和软件部分的说明。"

在本文档中,作者张亚峰详细介绍了Seg7_ControllerIP的功能、硬件结构、软件部分以及如何在实际项目中应用。IP的核心功能是驱动七段数码管进行动态显示,这种技术可以节省硬件资源,提高显示效率。

1. **IP说明**

- **功能**:Seg7_ControllerIP是一个专为七段数码管设计的驱动控制器,支持八位数码管的动态显示。它能够有效地控制数码管的每个段,呈现数字或字母信息。

- **寄存器**:IP包含两个寄存器,用于存储要显示的数据和控制信号,具体映射在表1.1中。

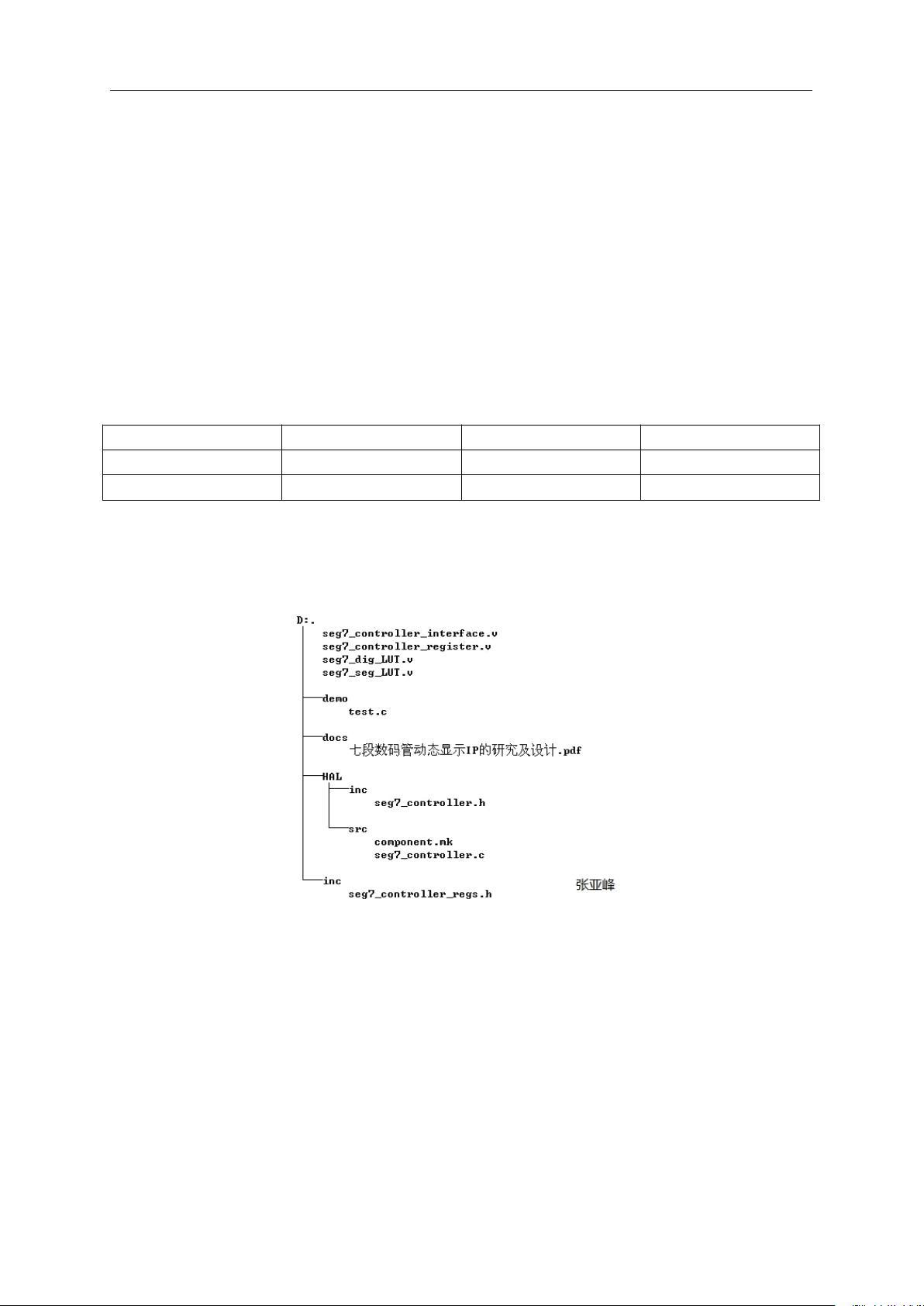

- **目录结构**:IP的目录结构清晰,便于用户理解和使用,包括HDL模块和源代码,以及软件部分的HAL和相关文件。

2. **IP硬件部分**

- **Avalon-MM接口**:Seg7_ControllerIP采用了Avalon-MM接口,这是Altera FPGA中的一种标准内存接口,用于主设备和从设备间的通信。接口包括写操作,去除了读操作,同时提供了从设备读写的时序描述。

- **HDL模块及源代码**:HDL模块包含了控制器的逻辑设计,分为模块介绍和源代码两部分,源代码是实现IP功能的关键,用于生成FPGA的配置。

3. **IP软件部分**

- **目录结构**:软件部分的目录结构与硬件类似,包含HAL(硬件抽象层)和源代码,方便集成到系统中。

- **HAL及源代码**:HAL提供了对IP的软件访问接口,包括寄存器地图和HAL库,使得软件开发者能够方便地控制七段数码管的显示。

- **添加到SOPCBuilderComponentLibrary**:说明了如何将Seg7_ControllerIP添加到SOPC构建系统中。

4. **NiosII自动抓取IP的HAL**

- **编写component.mk文件**:详细阐述了如何编写组件配置文件component.mk,以便NiosII处理器能够识别并使用Seg7_ControllerIP。

5. **IP使用举例**

- **在SOPCBuilder中添加seg7_controller**:指导用户在设计环境中添加Seg7_ControllerIP,并配置相应的系统连接。

- **在NiosII中使用范例**:提供了示例代码test.c,演示了如何通过NiosII处理器控制七段数码管显示,并展示了使用效果。

6. **参考文献**:列出相关参考资料,供进一步学习和研究。

这份文档详尽地阐述了Seg7_ControllerIP的设计原理、实现细节和使用方法,对于理解FPGA中的七段数码管动态显示技术以及如何在实际项目中应用这一技术具有重要价值。

点击了解资源详情

2020-10-26 上传

2021-09-30 上传

2020-11-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

senco_zheng

- 粉丝: 0

- 资源: 3

最新资源

- PowerDesigner数据库建模技术.pdf

- 呼叫中心运营指标体系.doc

- Linux操作系统下入门

- MVC ASP .NET

- JSP语法简明入门教程大全

- 谭浩强C语言设计第三版

- php的资料php优化

- 在ModelSimSE中添加ALTERA仿真库的详细步骤

- FLEX组件拖放详细描述

- 删除一段时间没有登入域的用户或计算机.txt

- 单片机c语言学习很好的资料

- Expert Oracle Database Architecture 9I And 10G Programming Techniques And Solutions.pdf

- javascript help sheet

- C语言指针简单详细教程

- javascript 实例大全

- I2C Spec Rev2.10