掌握时序控制:Vivado七段数码管显示项目设计全解

发布时间: 2024-12-20 12:20:44 阅读量: 10 订阅数: 14

基于vivado实现七段数码管显示

# 摘要

本文综合探讨了Vivado项目设计基础、七段数码管工作原理及时序控制的理论与实践应用。第一章为Vivado项目设计的初步介绍,着重阐述了时序控制的基本概念。第二章详细解释了七段数码管的工作原理和设计要求,为实践部分打下理论基础。第三章深入分析了时钟管理和同步、分频器设计及时序约束与分析等时序控制的理论知识,并提供了设计实践指导。第四章通过一个具体的七段数码管显示项目,展示了硬件设计、软件编码、整合与验证的完整实践流程。第五章展望了项目优化改进的方向,包括代码优化和硬件资源利用,同时探讨了时序控制技术在其他领域的潜在应用及未来技术趋势。本文为数字电路设计者提供了一个从基础理论到应用实践的全面指南,并对未来技术发展提供了深入的洞见。

# 关键字

Vivado项目设计;时序控制;七段数码管;硬件设计;软件编码;技术展望

参考资源链接:[基于Vivado的七段数码管动态与静态显示设计](https://wenku.csdn.net/doc/3mnvg33j38?spm=1055.2635.3001.10343)

# 1. Vivado项目设计基础与时序控制概念

在本章中,我们将深入探讨Vivado设计套件的基础知识,为理解和实施复杂的FPGA项目打下坚实基础。我们首先会介绍Vivado的设计流程和关键概念,确保每位读者都能够跟随文章的节奏。

## 1.1 Vivado设计流程概述

Vivado是一个由Xilinx公司开发的先进的设计套件,它采用了基于数据流的设计方法,让设计师能够进行高效的硬件描述语言(HDL)编码、仿真以及综合。在Vivado中,设计流程通常包括项目创建、源代码编写、仿真、综合、实现以及生成比特流文件等步骤。掌握这些步骤对于保证设计的正确性和优化性能至关重要。

## 1.2 时序控制的重要性

时序控制在FPGA设计中扮演着核心角色。它指的是在设计中确保所有的信号和操作都有明确的时间关系,以避免竞态条件和数据损坏。时序控制不仅涉及到硬件设计,还包括适当的时序约束,这是确保设计成功运行于目标FPGA的关键因素。

```mermaid

flowchart LR

A[创建Vivado项目] --> B[编写HDL代码]

B --> C[仿真测试]

C --> D[综合]

D --> E[实现]

E --> F[生成比特流]

F --> G[下载并测试]

```

通过这个流程图,我们可以清晰地看到Vivado设计流程的每一步,从创建项目开始,到最终测试验证,每一个环节都是确保设计成功的关键。在后续章节中,我们将逐一探讨这些环节,并且着重于时序控制的应用和优化。

# 2. 七段数码管的工作原理与设计要求

## 2.1 七段数码管的工作原理

### 2.1.1 数码管的基本结构

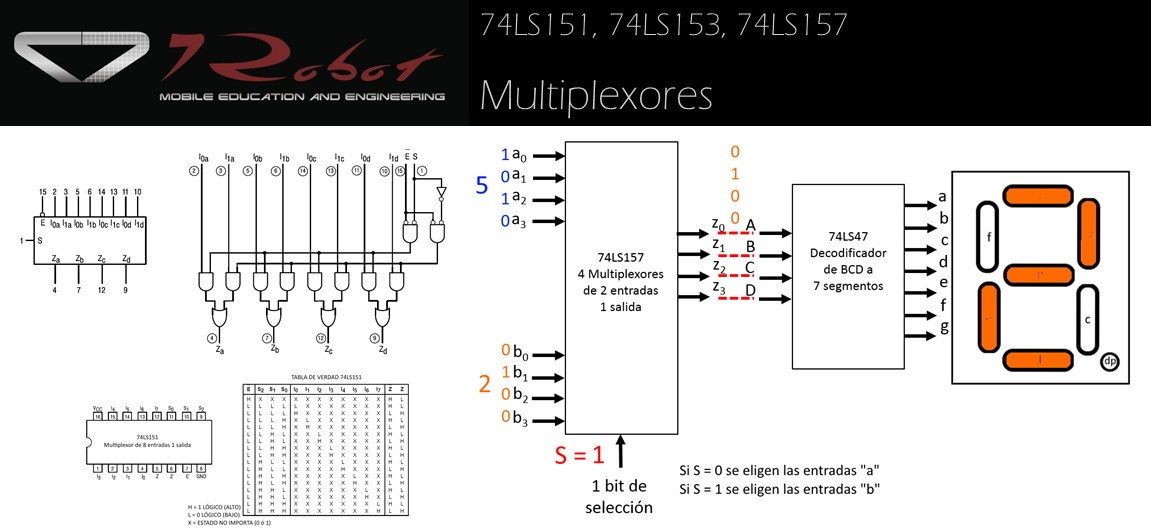

七段数码管是最常见的显示设备之一,广泛应用于计算器、钟表、仪表和其他数字显示场合。它由七个LED段组成,排列成一个“8”字形,每个段可以通过控制其对应的GPIO(通用输入输出)引脚来点亮或熄灭。这七个段被标记为A到G,其中A到F段用于构成数字,而G段用于小数点的显示。通过选择性地点亮这些段,可以显示从0到9的数字以及其他一些字符,如字母E或H等。

### 2.1.2 数字显示的逻辑

在显示数字时,根据想要显示的数字,选择相应的段来点亮。例如,要显示数字“1”,只需要点亮B和C两个段。所有段的控制通常通过一个共阳或共阴的连接方式来实现,这意味着所有的阳极或阴极都被连接在一起,并且通过单独控制每个段的另一端来点亮或熄灭它们。共阳或共阴连接方式决定了驱动信号的逻辑电平。

### 2.1.3 七段数码管的驱动方式

七段数码管的驱动可以采用静态驱动或动态驱动两种方式。在静态驱动方式中,每个段都直接连接到处理器的输出引脚,这种方法电路简单,但需要大量的I/O引脚。动态驱动方式则利用了人眼的视觉暂留特性,通过快速交替显示不同的数字来给人视觉上的连续显示,这样可以大大减少所需的I/O引脚数量。动态驱动中,通常使用一个解码器来驱动数码管,处理器通过改变解码器的输入来显示不同的数字或字符。

## 2.2 七段数码管的设计要求

### 2.2.1 设计的可靠性

七段数码管的设计必须考虑可靠性,这意味着设备需要在不同的工作条件下都能稳定工作,不会因环境变化、供电波动等因素而产生误显示。为此,设计中可能需要加入一些保护措施,比如电流限制电阻,以避免由于电流过大导致LED损坏。

### 2.2.2 低功耗设计

考虑到七段数码管通常是电源消耗的一个主要部分,设计时还需要注意低功耗要求。这可以通过选择低功耗的LED、优化驱动电路以及采用适当的显示策略来实现。例如,动态驱动方式不仅能够减少I/O引脚的使用,同时也能降低功耗。

### 2.2.3 易于集成与扩展

七段数码管的设计应该便于集成到更大的系统中,并且在后续的项目中可以方便地进行扩展和修改。这需要在设计阶段就考虑好模块化和标准化,使用封装良好的组件和接口,以及合理的布局规划,以确保当系统要求变化时,可以轻松地添加新功能或进行升级。

## 2.3 设计工具与方法

### 2.3.1 电路设计软件

在设计七段数码管的硬件电路时,通常会使用专业的电路设计软件,如Altium Designer、Eagle或KiCad等。这些软件提供了绘制原理图、PCB布局和设计仿真等功能,设计者可以利用这些工具完成电路设计的每个步骤。

### 2.3.2 验证与仿真

在设计完成之后,需要对电路进行验证和仿真,以确保设计的正确性。验证可以通过实际搭建电路并测试其功能来完成,而仿真则可以在软件环境中进行,通过模拟信号的流动和各个组件的行为来预测电路的工作状态。仿真可以帮助发现设计中的潜在问题,并在实际制作电路板之前进行修正。

### 2.3.3 测试与调试

测试是硬件设计中不可或缺的一个环节。设计者需要通过编写测试程序,利用逻辑分析仪、多用表等工具来测量电路的实际表现,与预期的输出进行对比。如果发现偏差,则需要进行调试,这可能涉及电路的物理修改,或者修改代码来改变硬件的工作模式。

# 3. Vivado时序控制理论与实践

## 3.1 时钟管理与同步

### 3.1.1 时钟资源与管理工具

在FPGA设计中,时钟资源是整个系统同步的基石。Vivado提供了丰富的时钟管理工具,允许设计师以一种灵活且高效的方式管理时钟域。时钟资源包括专用的时钟引脚、内部可编程时钟管理单元(MMCM)和相位锁定环(PLL)等。MMCM和PLL可以生成多个时钟输出,同时进行时钟分频、相位调整和抖动过滤等操作。

设计时钟管理网络时,需要考虑时钟的偏斜(Skew)和抖动(Jitter)。偏斜指的是时钟信号在不同寄存器间的到达时间差异,而抖动是指时钟周期的随机变化。Vivado提供了时钟规划工具和时钟约束语言(XDC),设计师可以通过编写约束来控制时钟偏斜,并优化设计的时钟网络,确保系统同步和稳定性。

在Vivado中,我们可以使用Clocking Wizard IP核来快速设计时钟管理解决方案。这个IP核可以自动生成MMCM或PLL的配置代码,并允许用户自定义时钟频率、相位和偏移等参数。

```tcl

# XDC约束示例:定义一个新的时钟源

create_clock -name sys_clk -period 10.000 -waveform {0.000 5.000} [get_ports {sys_clk}]

```

### 3.1.2 同步机制的设计原则

为了确保数据在时钟域之间的正确传递

0

0