零基础入门Vivado:七段数码管显示设计全攻略

发布时间: 2024-12-20 11:58:31 阅读量: 31 订阅数: 38

# 摘要

本文旨在详细探讨Vivado设计套件的使用方法、七段数码管的显示原理与基础,并通过实践设计来深入理解其高级功能实现。首先,文章概述了Vivado设计套件的基本概念及其安装过程。接着,深入分析了七段数码管的显示原理,包括其工作原理、分类及特性,并详细介绍了如何在Vivado项目中进行创建与管理。文章还涵盖了硬件描述语言(HDL)的基础知识,为后续的电路设计实践打下了坚实的理论基础。在实践章节中,作者详细讲述了如何设计电路、编写逻辑代码、进行仿真和调试,以及硬件实现与验证的具体步骤。此外,文章还探讨了七段数码管的动态显示技术、高级控制功能和用户交互设计,扩展了数码管的应用范围。最后,针对Vivado项目,提供了优化策略、常见问题的诊断与解决方法,以及项目优化的最佳实践,以帮助设计者提升设计效率和质量。

# 关键字

Vivado设计套件;七段数码管;硬件描述语言;仿真与调试;动态显示技术;项目优化策略

参考资源链接:[基于Vivado的七段数码管动态与静态显示设计](https://wenku.csdn.net/doc/3mnvg33j38?spm=1055.2635.3001.10343)

# 1. Vivado设计套件概述及安装

## Vivado设计套件的简介

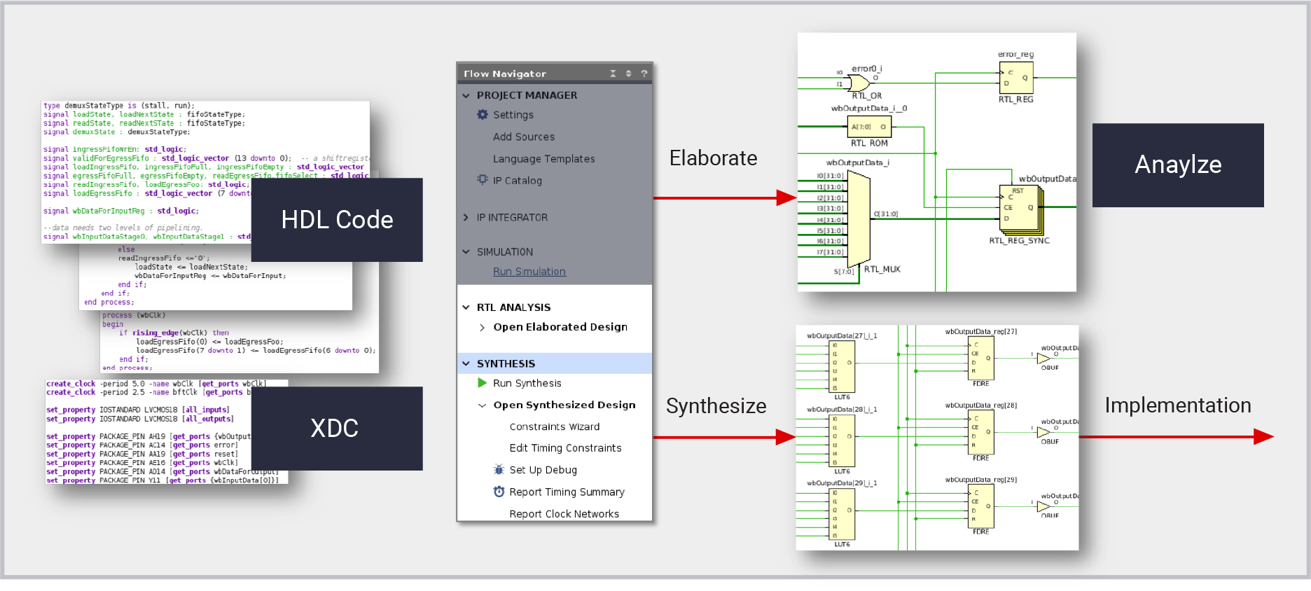

Vivado设计套件是Xilinx推出的用于FPGA和SoC开发的先进设计环境。它是一个全面的、基于IP集成和系统级的设计环境,集成了逻辑设计、综合、实现和验证流程。Vivado的用户界面经过优化,大大提高了设计效率,同时它支持高级HDL仿真和逻辑分析工具,为设计人员提供了更加直观和易用的开发体验。

## 安装Vivado设计套件的基本步骤

1. **下载安装文件**:从Xilinx官网下载最新版本的Vivado安装程序。

2. **运行安装向导**:双击下载的安装程序文件,启动安装向导。

3. **选择安装组件**:根据您的开发需求选择需要安装的组件,例如特定的开发板支持、IP核等。

4. **确认许可协议**:阅读并接受Vivado软件许可协议。

5. **开始安装**:按照向导提示完成安装,通常需要一定的时间根据您的系统性能而定。

6. **启动和验证安装**:安装完成后,启动Vivado并验证安装是否成功。

```sh

# 通常在Linux环境下,安装命令可能如下:

sudo ./Vivado_202X.X_web_install

```

## Vivado的系统要求与推荐配置

安装Vivado之前,需要确保系统满足其最小要求,并且为了获得最佳性能,最好遵循推荐配置。通常,高内存(至少16GB)、高速处理器和足够的硬盘空间是进行FPGA设计和仿真的基本配置。在安装过程中,Vivado安装程序会自动检查硬件配置并给出推荐。对于设计者来说,一个性能良好的计算机系统是高效进行FPGA开发的关键。

```sh

# 检查系统配置是否满足最小要求

# 示例命令(在Linux环境下)

cat /proc/meminfo | grep MemTotal

cat /proc/cpuinfo

```

通过本章,我们对Vivado设计套件有了一个初步的了解,以及如何进行安装。接下来,我们将深入探讨七段数码管的显示原理与基础,为进入FPGA设计领域打下基础。

# 2. 七段数码管显示原理与基础

### 2.1 数码管显示原理解析

#### 2.1.1 数码管的工作原理

七段数码管是一种电子显示设备,广泛应用于数字显示领域,如时钟、计算器、数字仪表等。它由七个发光二极管组成,排列成一个“8”字型。通过控制这七个LED的点亮与熄灭,可以显示0到9的十个数字以及部分字母和符号。数码管的每个段分别由a到g七个字母来表示,通过向这些段提供电流,控制对应的LED亮起,就可以组合出不同的数字和字符。

数码管可以是共阴极或共阳极类型。在共阴极数码管中,所有的LED的负极都连接在一起,并接地,而正极分别连接到控制引脚;在共阳极数码管中,所有的LED的正极都连接在一起,并接电源,负极分别连接到控制引脚。根据数码管的类型,需要控制不同的引脚来点亮LED。

```mermaid

flowchart LR

A[共阴极数码管] -->|控制引脚高电平| B[LED点亮]

A -->|控制引脚低电平| C[LED熄灭]

D[共阳极数码管] -->|控制引脚低电平| E[LED点亮]

D -->|控制引脚高电平| F[LED熄灭]

```

#### 2.1.2 数码管的分类及特性

数码管按照其结构和用途可以分为直插式和贴片式两大类。直插式数码管的LED引脚较长,适合手工焊接,常用于单片机等DIY项目。贴片式数码管体积小,适合自动化贴片,常用于手机和便携式设备等对体积要求较高的产品。

除了结构上的分类,数码管还可以根据其显示特性进行分类。例如,根据显示的颜色可以分为红色、绿色、黄色等不同颜色的数码管;根据功能可以分为只有数字显示和可以显示字母及特殊符号的多种功能数码管。

### 2.2 Vivado项目创建与管理

#### 2.2.1 创建第一个Vivado项目

创建Vivado项目是设计流程的第一步。首先,打开Vivado设计套件,选择“Create Project”,接着在弹出的向导中输入项目名称和路径,选择项目类型(RTL Project)和目标设备(FPGA或Zynq SoC)。随后,添加源文件(例如Verilog或VHDL文件),并配置项目的约束文件(如XDC文件)。完成这些步骤后,就可以开始项目的设计和实现工作。

#### 2.2.2 项目文件结构和管理

Vivado项目文件结构包含了多种文件类型,如源文件(.v或.vhd)、仿真文件(.tcl)、约束文件(.xdc)、综合脚本文件(.tcl)和报告文件等。项目管理涉及文件的组织、版本控制和编译设置等。良好的项目文件管理有助于提高开发效率并维护项目秩序。

```mermaid

graph LR

A[项目根目录] -->|Verilog源文件| B[.v文件]

A -->|VHDL源文件| C[.vhd文件]

A -->|仿真文件| D[.tcl文件]

A -->|约束文件| E[.xdc文件]

A -->|报告文件| F[.rpt文件]

```

### 2.3 硬件描述语言基础

#### 2.3.1 HDL入门知识

硬件描述语言(HDL)是用于描述电子系统硬件设计的语言,主要有两种:VHDL和Verilog。HDL允许设计师通过描述硬件功能和结构的方式来设计电路,它支持从抽象的算法级描述到具体门级描述的各个设计层次。HDL的设计过程开始于行为级描述,然后逐步细化到逻辑门级。

#### 2.3.2 语法基础与编写简单代码

编写HDL代码的基本步骤包括定义模块、声明端口、编写行为描述以及指定时序。例如,一个简单的Verilog代码模块可能如下所示:

```verilog

module simple_counter(

input clk, // 时钟信号

input reset, // 复位信号

output reg [3:0] out // 4位输出计数值

);

// 内部寄存器

reg [3:0] count;

// 计数器行为描述

always @(posedge clk or posedge reset) begin

if (reset) begin

count <= 4'd0; // 同步复位

end else begin

count <= count + 1'b1; // 同步计数

end

end

// 将内部计数值输出

always @(count) begin

out <= count;

end

endmodule

```

在这段代码中,定义了一个名为`simple_counter`的模块,它有一个时钟输入`clk`,一个复位输入`reset`,以及一个4位宽的输出`out`。模块内部有一个4位计数器`count`,在每个时钟上升沿和复位信号的上升沿操作。当复位信号为高时,计数器被清零;否则,计数器值加一。输出值`out`始终等于内部计数值`count`。

# 3. 七段数码管显示设计实践

## 3.1 设计电路与实现逻辑

### 3.1.1 确定数码管显示需求

设计一个七段数码管显示系统,我们首先需要确定基本的需求。这些需求包括:

- 显示数字0至9。

- 通过简单的逻辑切换显示不同的数字。

- 若有可能,实现一些基本的动态显示效果,比如流水灯效果。

我们的设计将从这些基础需求开始,并在后续章节中逐步完善功能。

### 3.1.2 编写逻辑代码

接下来,我们将使用硬件描述语言(HDL)来编写实现这些需求的逻辑代码。假设我们使用的是Vivado环境,我们将创建一个VHDL或Verilog模块来描述我们的逻辑。

这里是一个使用Verilog实现的简单例子,假设我们将数字0至9依次显示在数码管上。

```verilog

module seven_segment_display(

input wire [3:0] digit, // 输入4位二进制表示的数字

output reg [6:0] seg // 输出7段数码管的控制信号

);

// 根据输入的数字来设置数码管的段信号

always @(digit) begin

case(digit)

4'h0: seg = 7'b1000000; // 二进制表示法:7位二进制数控制7段LED

4'h1: seg = 7'b1111001;

4'h2: seg = 7'b0100100;

4'h3: seg = 7'b0110000;

// 中间省略...

4'h9: seg = 7'b0010000;

default: seg = 7'b1111111; // 默认情况下关闭所有段

endcase

end

endmodule

```

在上述代码中,`digit`是一个4位的输入信号,用于接收从0到9的数字。`seg`是一个7位的输出信号,每一位对应数码管的一段,分别表示a至g七个段。通过`always`块中的`case`语句,我们根据输入的数字来设置`seg`输出,从而控制数码管显示相应的数字。

## 3.2 Vivado中的仿真与调试

### 3.2.1 仿真环境搭建

在Vivado中进行仿真首先需要创建一个仿真环境。这通常包括一个测试台(Testbench),它是用来模拟真实世界信号和响应的Verilog或VHDL文件。

```verilog

`timescale 1ns / 1ps

module tb_seven_segment_display();

// 测试台信号声明

reg [3:0] digit;

wire [6:0] seg;

// 实例化待测试模块

seven_segment_display uut (

.digit(digit),

.seg(seg)

);

// 测试过程

initial begin

// 初始化输入信号

digit = 4'h0;

// 每隔10ns切换显示数字

#10 digit = digit + 1;

if (digit > 4'h9) digit = 4'h0;

end

endmodule

```

在上述测试台代码中,我们声明了输入和输出信号,实例化了待测试的模块,并设置了一个简单的测试过程。这个过程会在每10纳秒增加输入信号`digit`的值,并在数字超过9后重新从0开始。

### 3.2.2 功能验证与错误调试

仿真执行之后,我们需要验证模块功能是否正确。如果发现与预期行为不符,我们将进行错误调试。

在Vivado的仿真工具中,我们可以观察波形图来判断每个信号的正确性。如果发现错误,我们返回到代码中寻找可能的逻辑错误或拼写错误,并进行修改。

## 3.3 硬件实现与验证

### 3.3.1 将设计下载至FPGA板卡

将设计实现到FPGA板卡,我们首先需要生成一个比特流文件。在Vivado中,我们可以通过"Generate Bitstream"命令来实现。

完成比特流生成后,我们使用Vivado的硬件服务器功能将比特流下载到FPGA开发板。下载过程中,Vivado会通过JTAG或其它接口与FPGA板卡通信,完成比特流的写入。

### 3.3.2 实际硬件测试与分析

下载完成后,我们对FPGA板卡进行实际测试。通常包括以下步骤:

1. 为FPGA开发板供电。

2. 观察七段数码管的显示是否符合预期。

3. 如果发现问题,回到Vivado中检查仿真结果和代码。

完成测试后,可能需要根据实际硬件的反馈调整设计或进一步优化。

在本章节中,我们已经学习了七段数码管显示设计实践的核心内容,包括如何确定显示需求,编写逻辑代码,并在Vivado中进行仿真与调试,最后完成硬件的实现与验证。通过这些步骤,我们能够更好地理解在FPGA上实现七段数码管显示的整个流程。

# 4. 七段数码管的高级功能实现

## 4.1 动态显示与多路复用技术

### 4.1.1 动态显示的工作原理

动态显示技术是利用人眼的视觉暂留特性,在短时间内快速切换显示内容,从而形成视觉上的连续显示效果。对于七段数码管而言,动态显示通常涉及多个数码管的快速切换,这种技术可以有效地减少所需的IO口数量,并提高显示的灵活性和功能性。

动态显示中使用的多路复用技术是关键所在,它允许通过较少的IO口控制多个数码管。每个数码管依次点亮一小段时间,然后切换到下一个,循环往复。由于切换速度足够快,人眼就会产生连续显示的错觉。

### 4.1.2 编写多路复用代码

在Vivado中,要实现动态显示和多路复用,需要编写相应的逻辑代码。以下是一个简单的多路复用代码示例,该示例代码用于控制四个七段数码管的显示。

```verilog

module dynamic_display(

input clk, // 时钟信号

output reg [3:0] an, // 数码管位选信号

output reg [6:0] seg // 数码管段选信号

);

// 定义显示内容和位选信号的初始值

reg [6:0] seg_reg [3:0];

initial begin

seg_reg[0] = 7'b1111110; // '0'

seg_reg[1] = 7'b0110000; // '1'

seg_reg[2] = 7'b1101101; // '2'

seg_reg[3] = 7'b1111001; // '3'

end

// 计数器,用于生成扫描频率

reg [15:0] counter = 0;

always @(posedge clk) begin

counter <= counter + 1;

end

// 产生位选信号,进行数码管的多路复用

integer i;

always @(posedge clk) begin

an <= 4'b1110; // 默认无位选

seg <= seg_reg[0]; // 默认显示第一路数码管

for (i = 0; i < 4; i = i + 1) begin

if (counter == i) begin

an <= ~(1 << i); // 选择当前位

seg <= seg_reg[i]; // 显示当前位内容

end

end

end

endmodule

```

上述代码首先定义了一个模块`dynamic_display`,其中包含了时钟信号`clk`、位选信号`an`和段选信号`seg`。`seg_reg`数组存储了四个数码管的初始显示内容。在时钟上升沿,计数器`counter`用于产生扫描频率,然后通过一个循环来选择相应的数码管进行显示。该代码通过快速切换`an`信号实现多路复用,从而控制四个数码管依次显示。

### 4.2 高级控制功能设计

#### 4.2.1 设计时间控制逻辑

为了给七段数码管增加时间显示功能,我们需要设计一个时间控制逻辑模块,该模块可以产生时钟脉冲,并根据这些脉冲来更新显示内容。以下是时间控制逻辑模块的代码示例。

```verilog

module timer_control(

input clk, // 外部时钟信号

input reset, // 复位信号

output reg [5:0] sec, // 秒计数器

output reg [5:0] min, // 分计数器

output reg [5:0] hour // 时计数器

);

// 每秒的脉冲计数,假设外部时钟为50MHz

localparam ONE_SECOND_PULSE = 50_000_000;

reg [25:0] pulse_counter = 0; // 定义26位计数器

// 时钟脉冲计数逻辑

always @(posedge clk or posedge reset) begin

if (reset) begin

pulse_counter <= 0;

sec <= 0;

min <= 0;

hour <= 0;

end else begin

if (pulse_counter == ONE_SECOND_PULSE - 1) begin

pulse_counter <= 0;

sec <= sec + 1;

if (sec == 59) begin

sec <= 0;

min <= min + 1;

if (min == 59) begin

min <= 0;

hour <= hour + 1;

if (hour == 23) begin

hour <= 0;

end

end

end

end else begin

pulse_counter <= pulse_counter + 1;

end

end

end

endmodule

```

在这个模块中,我们定义了秒、分、时三个计数器,以及一个脉冲计数器`pulse_counter`。假设外部时钟频率为50MHz,则每秒的脉冲数为50,000,000。每当计数器达到这个数值时,秒计数器`sec`就会加一,如果秒数满60,则分钟计数器`min`增加,以此类推,实现一个简单的时钟功能。

#### 4.2.2 实现亮度调节功能

为了调节七段数码管的亮度,可以通过改变数码管的点亮时间占空比来实现。以下是一个简单的亮度调节代码示例。

```verilog

module brightness_control(

input clk, // 外部时钟信号

input [1:0] brightness_level, // 亮度等级选择

output reg [3:0] an, // 数码管位选信号

output reg [6:0] seg // 数码管段选信号

);

// 定义不同亮度等级对应的占空比

reg [15:0] duty_cycle[3:0];

initial begin

duty_cycle[0] = 16'h0000; // 最暗

duty_cycle[1] = 16'h4000; // 中等偏暗

duty_cycle[2] = 16'h8000; // 中等

duty_cycle[3] = 16'hC000; // 最亮

end

// 亮度控制计数器

reg [15:0] brightness_counter = 0;

always @(posedge clk) begin

brightness_counter <= brightness_counter + 1;

case(brightness_level)

2'b00: an <= ~(an & (seg >= duty_cycle[0]));

2'b01: an <= ~(an & (seg >= duty_cycle[1]));

2'b10: an <= ~(an & (seg >= duty_cycle[2]));

2'b11: an <= ~(an & (seg >= duty_cycle[3]));

endcase

end

endmodule

```

在这个模块中,我们定义了一个亮度等级选择输入`brightness_level`,通过它可以调节数码管的显示亮度。亮度控制部分使用了一个计数器`brightness_counter`来循环遍历所有数码管,并根据`duty_cycle`数组来控制每个数码管的点亮时间占空比。通过改变`brightness_level`的值,我们可以实现不同数码管的亮度调节。

### 4.3 用户交互设计

#### 4.3.1 外部输入设备接口设计

为了提升用户交互体验,我们可以设计一个外部输入设备接口,用于接收用户的输入信号,例如按钮、旋钮等。以下是一个简单的外部输入设备接口设计代码示例。

```verilog

module input_interface(

input clk, // 外部时钟信号

input rst_n, // 复位信号,低电平有效

input [3:0] btn, // 按钮输入

output reg [3:0] btn_reg // 按钮寄存器,用于消抖

);

// 按钮消抖逻辑

reg [15:0] debounce_counter = 0;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

debounce_counter <= 0;

btn_reg <= 4'b0000;

end else begin

debounce_counter <= debounce_counter + 1;

if (debounce_counter == 16'hFFFF) begin

btn_reg <= btn;

debounce_counter <= 0;

end

end

end

endmodule

```

在这个模块中,我们通过一个计数器`debounce_counter`实现按钮消抖功能,`btn`是外部按钮输入信号,`btn_reg`是经过消抖处理后的输出信号。当检测到按钮状态稳定时,`btn_reg`的值会更新,否则计数器继续计数直到达到最大值。

#### 4.3.2 用户界面逻辑实现

为了提供良好的用户界面体验,我们需要实现一个用户界面逻辑,它将根据用户输入以及当前设备状态来进行显示内容的更新。以下是一个简单的用户界面逻辑代码示例。

```verilog

module user_interface(

input clk, // 外部时钟信号

input rst_n, // 复位信号,低电平有效

input [3:0] btn_reg, // 消抖后的按钮信号

input [5:0] sec, // 当前秒数

input [5:0] min, // 当前分钟数

input [5:0] hour, // 当前小时数

output reg [3:0] an, // 数码管位选信号

output reg [6:0] seg // 数码管段选信号

);

// 用户界面状态机

reg [1:0] state = 0;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= 0;

an <= 4'b1110;

seg <= 7'b1111110; // 默认显示0

end else begin

case (state)

2'b00: begin

an <= 4'b1110;

seg <= seg_0;

end

2'b01: begin

an <= 4'b1101;

seg <= seg_1;

end

// ... 更多状态处理

default: begin

an <= 4'b1111;

seg <= 7'b1111111; // 关闭显示

end

endcase

// ... 状态转移逻辑

end

end

endmodule

```

在这个模块中,我们设计了一个简单的状态机来处理用户的输入和设备状态。根据`btn_reg`中的按钮状态,可以更改用户界面的显示内容。`an`和`seg`输出用于控制数码管的显示。该代码是一个状态机的框架示例,具体的状态转移逻辑和显示内容需要根据实际应用进行设计。

以上各节内容体现了Vivado中七段数码管显示设计的高级功能实现方法。动态显示与多路复用技术允许我们在有限的IO口上控制多个数码管,而高级控制功能设计如时间控制逻辑和亮度调节功能则大幅提升了数码管的实用性和用户体验。最后,用户交互设计部分演示了如何通过外部输入设备接口和用户界面逻辑实现与用户的互动。这些章节展示了在实际项目中,如何将基本的七段数码管显示功能拓展到更加复杂和实用的应用场景。

# 5. Vivado项目优化与故障排除

在现代的FPGA开发流程中,优化项目性能和解决可能出现的问题是至关重要的环节。Vivado作为Xilinx提供的先进设计套件,提供了丰富的工具和功能来帮助设计者完成这些任务。本章节将详细介绍在使用Vivado进行项目优化时可以采取的策略,以及如何诊断和解决项目中常见的问题。此外,我们还将探索最佳的设计实践,包括设计复用、模块化以及项目文档的编写与维护。

## 5.1 项目优化策略

在FPGA项目设计后期,优化工作显得尤为重要,它旨在提高系统性能,降低资源占用,提升功耗效率。优化策略可以从多个维度入手,包括但不限于代码优化、逻辑优化、布局布线优化等。

### 5.1.1 代码优化技巧

代码优化是提高性能、减少资源消耗的重要手段。以下是一些常用的代码优化技巧:

- **减少不必要的逻辑**:通过逻辑简化,减少不必要的逻辑门数量,例如,使用布尔代数简化表达式。

- **避免使用复杂的算术运算**:复杂的算术运算会导致更多的资源消耗,尽可能使用简单的算术结构。

- **利用并行处理**:尽可能多地使用并行处理来加快执行速度,合理分配资源以避免瓶颈。

```verilog

// 简化的算术运算示例

always @(posedge clk) begin

sum <= a + b; // 简单加法

product <= a * b; // 避免使用复杂的乘法器

end

```

### 5.1.2 资源使用与性能优化

资源使用和性能优化需要综合考虑项目的目标和约束。以下是几个关键点:

- **时钟管理**:使用合理的时钟域,避免时钟网络的过度复杂化。

- **RAM和DSP资源利用**:优化存储和数字信号处理资源的使用,减少资源浪费。

- **逻辑合成优化**:合理选择逻辑合成的策略,根据目标芯片的特性来定制优化。

## 5.2 常见问题诊断与解决

Vivado项目在开发过程中可能会遇到各种问题,正确诊断和快速解决问题是提高开发效率的关键。

### 5.2.1 Vivado常见错误分析

Vivado的错误信息通常会提供大量关于问题的线索,例如:

- **综合错误**:综合阶段出现的错误通常与HDL代码有关,检查语法错误和逻辑不一致的地方。

- **时序约束问题**:时序约束不当会导致时序问题,需要仔细检查时序约束文件(.xdc)。

- **布局布线问题**:错误的布局布线可能导致资源冲突,利用Vivado的分析工具进行检查。

### 5.2.2 故障排除步骤与方法

解决Vivado项目问题的一般步骤包括:

- **查看错误信息**:首先查看Vivado提供的错误信息。

- **检查日志文件**:Vivado的编译日志通常能够提供更详细的信息。

- **进行模块化测试**:将项目分解为多个模块进行独立测试,定位问题所在。

## 5.3 设计的最佳实践

良好的设计习惯不仅可以提高设计效率,还能增强设计的可维护性和可重用性。

### 5.3.1 设计复用与模块化

设计复用是减少开发时间、提高产品质量的有效途径。模块化设计有助于:

- **提高复用性**:设计独立的模块,使其在不同项目中复用。

- **简化调试过程**:模块化的设计让每个模块可以单独进行测试和验证。

### 5.3.2 项目文档编写与维护

良好的文档编写和维护习惯对于项目长期的可维护性至关重要。文档应包括但不限于:

- **设计说明**:清楚地说明设计的目的、功能和接口。

- **使用指南**:为模块的使用者提供详细的操作指南和示例代码。

- **维护记录**:记录项目开发过程中的重要变更和优化。

通过深入学习和实践上述Vivado项目优化与故障排除的知识,项目设计者可以显著提升设计效率和质量,最终开发出稳定可靠且性能优越的FPGA应用产品。

0

0