强场强下电磁脉冲传感器校准技术与EMC设计策略

174 浏览量

更新于2024-08-28

收藏 293KB PDF 举报

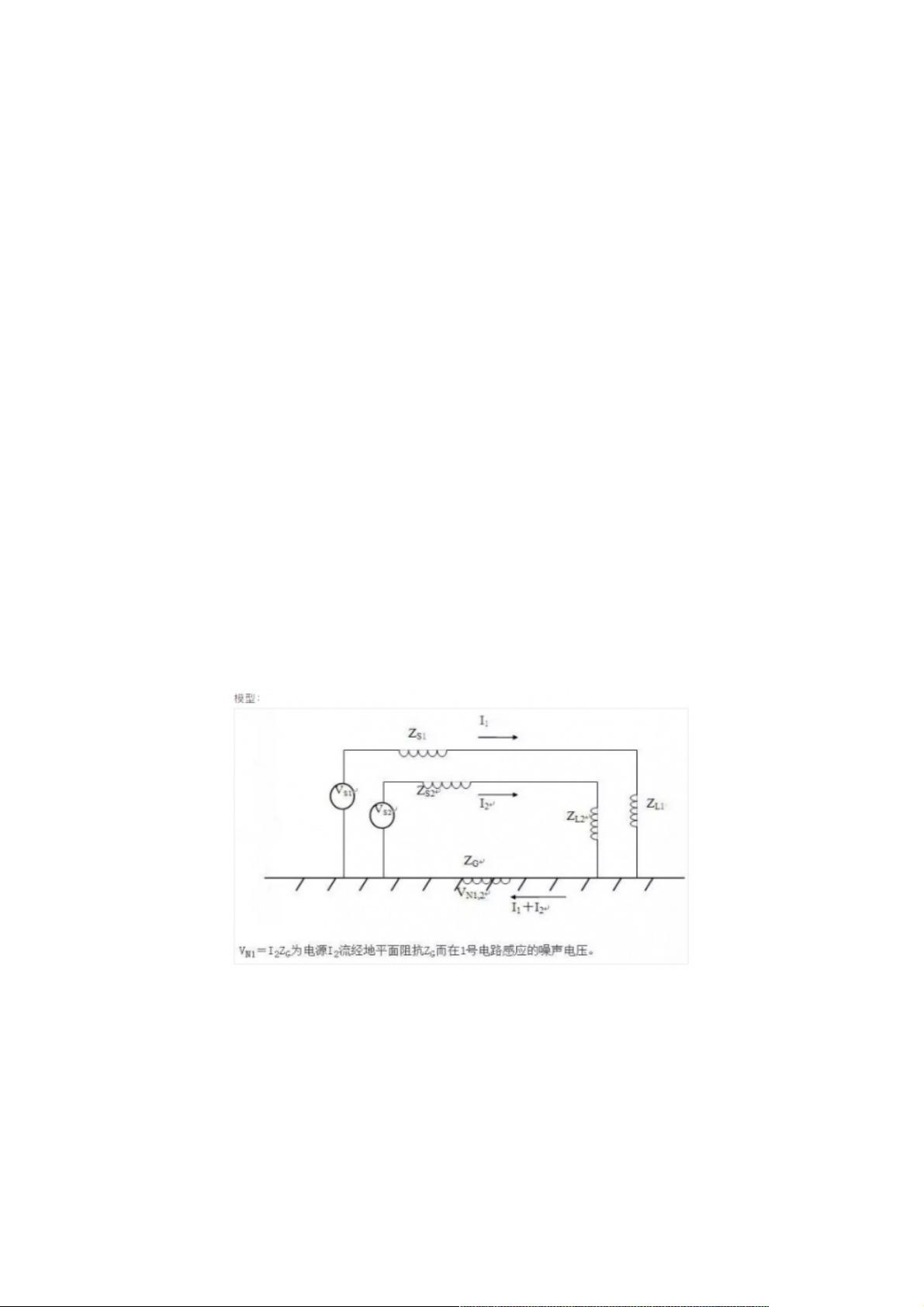

本文介绍了电磁脉冲传感器在强场强下的校准方法,涉及电磁兼容(EMC)的基本原理和技术,以及在高速逻辑电路设计中的重要性。EMC研究的核心是干扰源、传输途径和接收器,其控制技术包括屏蔽、滤波和接地,目的是减少电磁干扰。规范强调了单板设计中的EMC考虑,如公共阻抗耦合、串扰、辐射和噪声拾取等问题。

正文:

在电磁兼容领域,电磁脉冲传感器的校准在强场强环境下尤为关键,因为这些环境可能导致严重的干扰问题。干扰的三要素是干扰源、传播路径和接收器,而EMC研究的焦点在于如何控制和管理这三个方面。基本的干扰抑制手段包括屏蔽,通过物理隔离来防止电磁能量传播;滤波,利用电容、电感元件消除特定频段的干扰;以及接地,提供低阻抗通路,使干扰电流流向大地。

在单板设计中,考虑EMC可以显著降低样机阶段的电磁干扰。设计时需关注的问题有公共阻抗耦合,即不同电路共享同一阻抗,导致噪声耦合;串扰,高频率信号通过互连布线间的耦合影响其他信号;高频载流导线产生的辐射;以及通过印制线形成的回路拾取的噪声。对于高速逻辑电路,这些问题尤为突出,因为随着频率增加,电源和地线的阻抗会增大,耦合效应更明显,信号反射和串扰也更容易发生。

为解决这些问题,提出了以下策略:

1. 遵循“五一五规则”,即当时钟频率超过5MHz或脉冲上升时间小于5ns时,应使用多层PCB板,以提供更好的信号隔离和电源分布。

2. 不同电源平面应避免重叠,以减少相互之间的干扰。

3. 实现模拟和数字电路的独立回路,采用单点接地,以减少公共阻抗耦合。

4. 宽电源线和回线可以降低阻抗,缩短印制线长度则能减少噪声传播。

5. 减小环路面积,降低两环路交链面积,以减少辐射和耦合。

6. 优化电源分配系统,使用去耦电容,确保电源的稳定性。

布局方面,应遵循以下原则:

- 晶振应靠近处理器放置,以减少信号传输距离和潜在的噪声引入。

- 分区布局,模拟电路和数字电路在PCB板上应有明确的区域划分。

- 高频组件尽量布置在PCB边缘,便于辐射外泄,同时逐层放置以减小串扰。

通过理解并应用这些概念和设计原则,可以在强电磁场环境中对电磁脉冲传感器进行有效校准,确保其在复杂电磁环境下的稳定性和准确性。同时,这也有助于整体系统的EMC性能提升,减少电磁干扰,保证电子设备的正常运行。

2020-01-14 上传

2021-09-15 上传

2021-09-15 上传

点击了解资源详情

点击了解资源详情

2024-11-01 上传

weixin_38571759

- 粉丝: 6

- 资源: 897

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程