16 Intel® Xeon Phi™ Processor

Datasheet - Volume 2, December 2016

9.2.49 RTL22: Redirection Table Low DWORD.....................................................373

9.2.50 RTH22: Redirection Table High DWORD ...................................................375

9.2.51 RTL23: Redirection Table Low DWORD.....................................................375

9.2.52 RTH23:Redirection Table High DWORD .................................................... 377

Figures

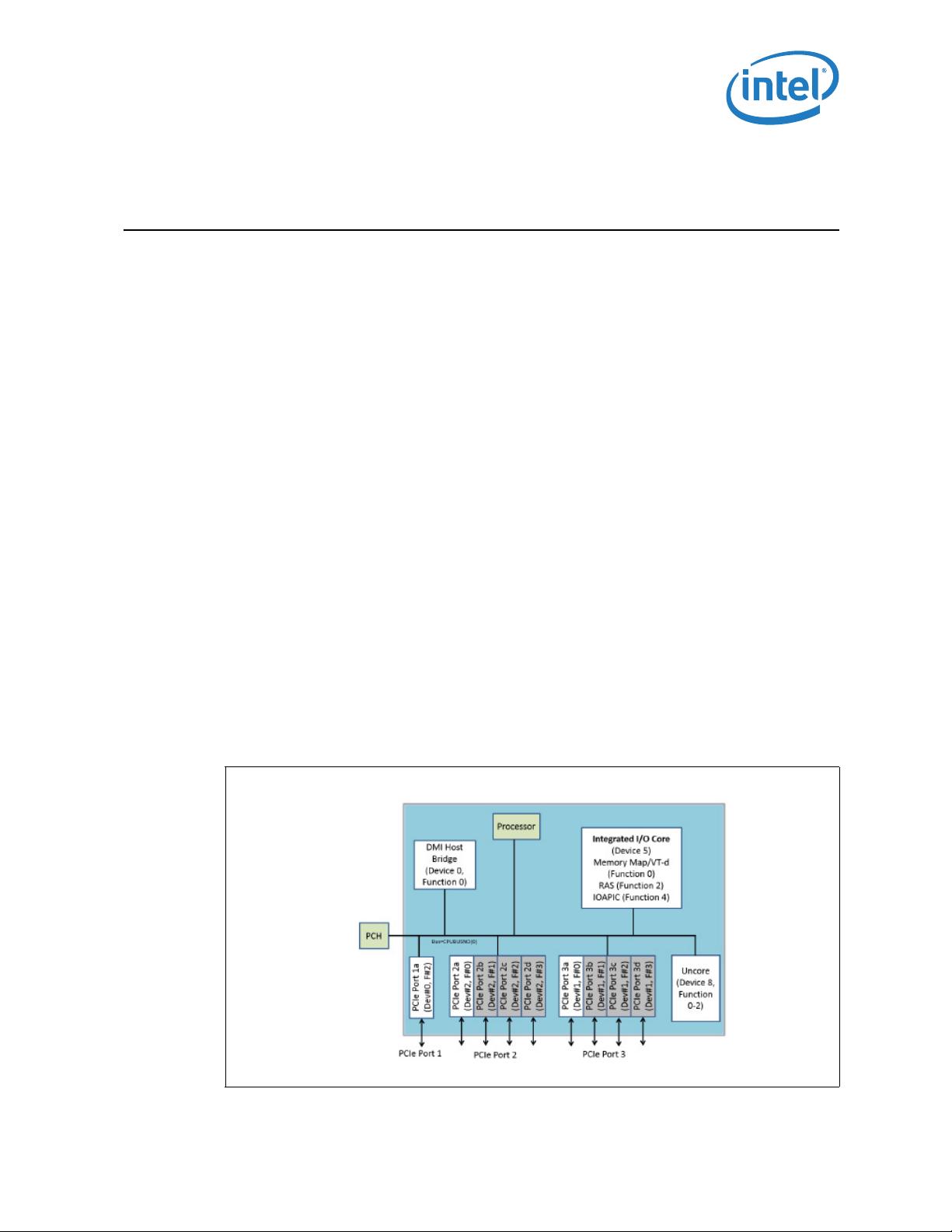

1-1 Processor Integrated I/O Device Map....................................................................19

1-2 Processor Uncore Devices Map.............................................................................21

6-1 PCIe Root Port Configuration Register Map Offset 0x00 – 0x1FF ............................. 128

6-2 PCIe Root Port Configuration Register Map Offset 0x200 – 0x3FF ........................... 129

6-3 PCIe Root Port Configuration Register Map Offset 0x400 - 0x4FF ............................ 130

7-1 Memory Map and Intel VT-d Configuration Register Map Offset 0x00 - 0x1FF ...........230

7-2 Memory Map and Intel VT-d Register Map Offset 0x200 - 0x3FF ............................. 231

7-3 Intel VT-d Memory Register Map Offset 0x00 - 0x20B ...........................................236

7-4 Intel VT-d Memory Register Map Offset 0x1000 - 0x120B...................................... 237

8-1 RAS Configuration Register Map Offset 0x00 - 0x1FF ............................................ 278

8-2 RAS Configuration Register Map Offset 0x200 - 0x3FF .......................................... 279

9-1 IOxAPIC Configuration Register Map Offset 0x00 - 0x2FF ......................................317

9-2 IOxAPIC MMIO Register Map Offset 0x00 - 0x4F ..................................................327

9-3 IOxAPIC MMIO Register Map Offset 0x00 - 0x4F ..................................................329

Tables

1-1 Functions Specifically Handled by the Processor .....................................................23

1-2 Glossary...........................................................................................................26

1-3 Register Attribute Definitions...............................................................................28

2-1 Summary of Bus: 2, Device: 23, Function: 4 (CFG) ................................................31

2-2 Summary of Bus: 2, Device: 24, Function: 4 (CFG) ................................................36

3-1 MC0 Register ID/Name Mapping ..........................................................................41

3-2 Physical to Logical Memory channel mapping .........................................................43

3-3 Summary of Bus: 2, Device: 10, Function: 0 (CFG) ................................................43

3-4 Summary of Bus: 2, Device: 10, Function: 1 (CFG) ................................................46

3-5 Summary of Bus: 2, Device: 10, Function: 2 (CFG) ................................................55

3-6 Summary of Bus: 2, Device: 8, Function: 0 (CFG)..................................................60

3-7 Summary of Bus: 2, Device: 8, Function: 1 (CFG)..................................................81

4-1 Summary of Bus: 1, Device: 30, Function: 0 (CFG) ................................................89

4-2 Summary of Bus: 1, Device: 30, Function: 1 (CFG) ................................................97

4-3 Summary of Bus: 1, Device: 30, Function: 2 (CFG) ................................................99

4-4 Summary of Bus: 1, Device: 30, Function: 3 (CFG) .............................................. 103

5-1 BDF BAR# for Various MMIO BARs in IIO ............................................................125