Design Compiler详解:从RTL综合原理到实践操作

需积分: 12 98 浏览量

更新于2024-07-23

收藏 2.73MB PDF 举报

综合与Design Compiler是电子设计自动化(EDA)流程中的关键环节,尤其在硬件描述语言(HDL)如Verilog或VHDL的设计过程中起着至关重要的作用。Design Compiler是Synopsys公司提供的一个强大的电路综合工具,主要用于将高级语言描述的电路转换成实际可制造的门级电路。

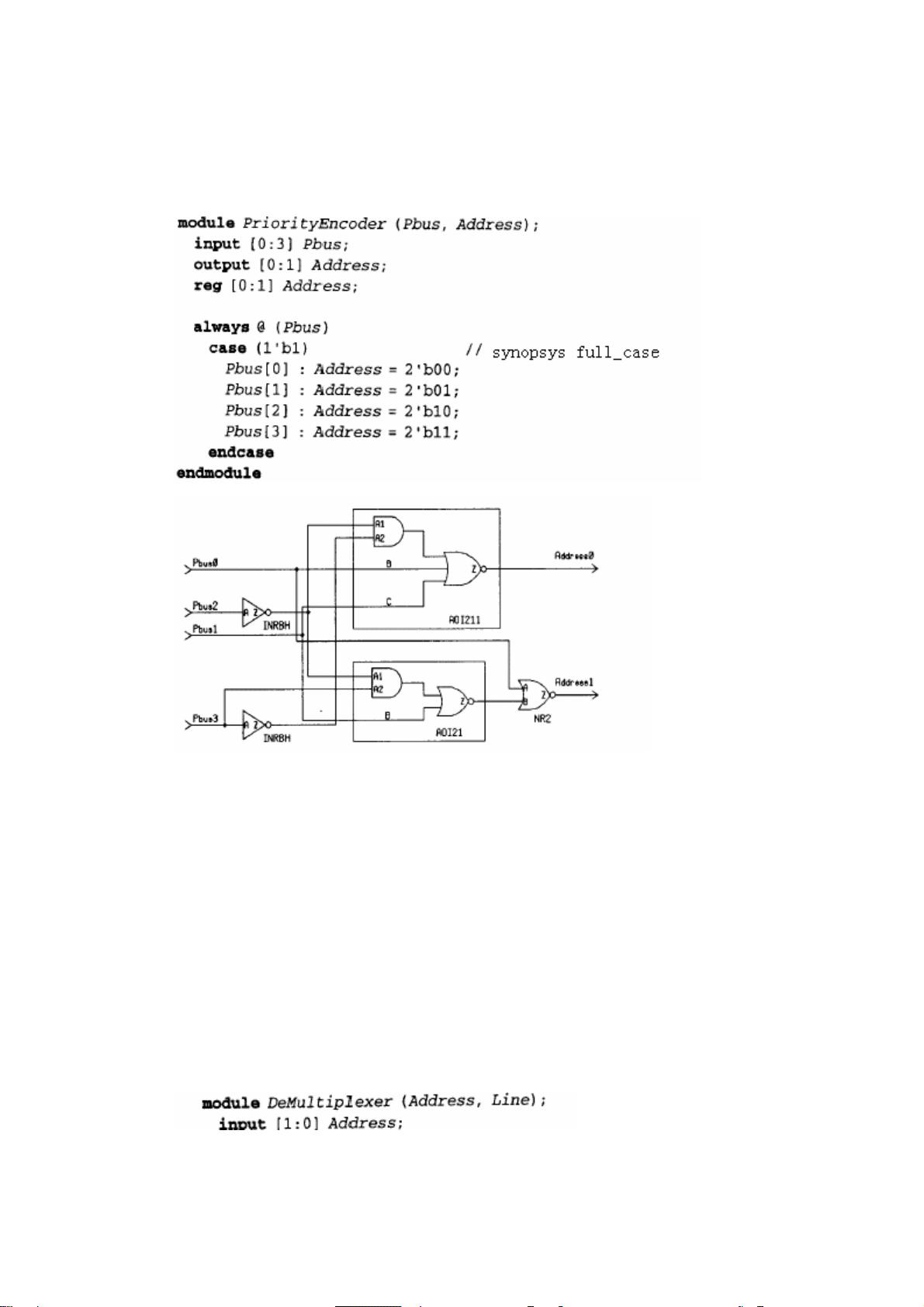

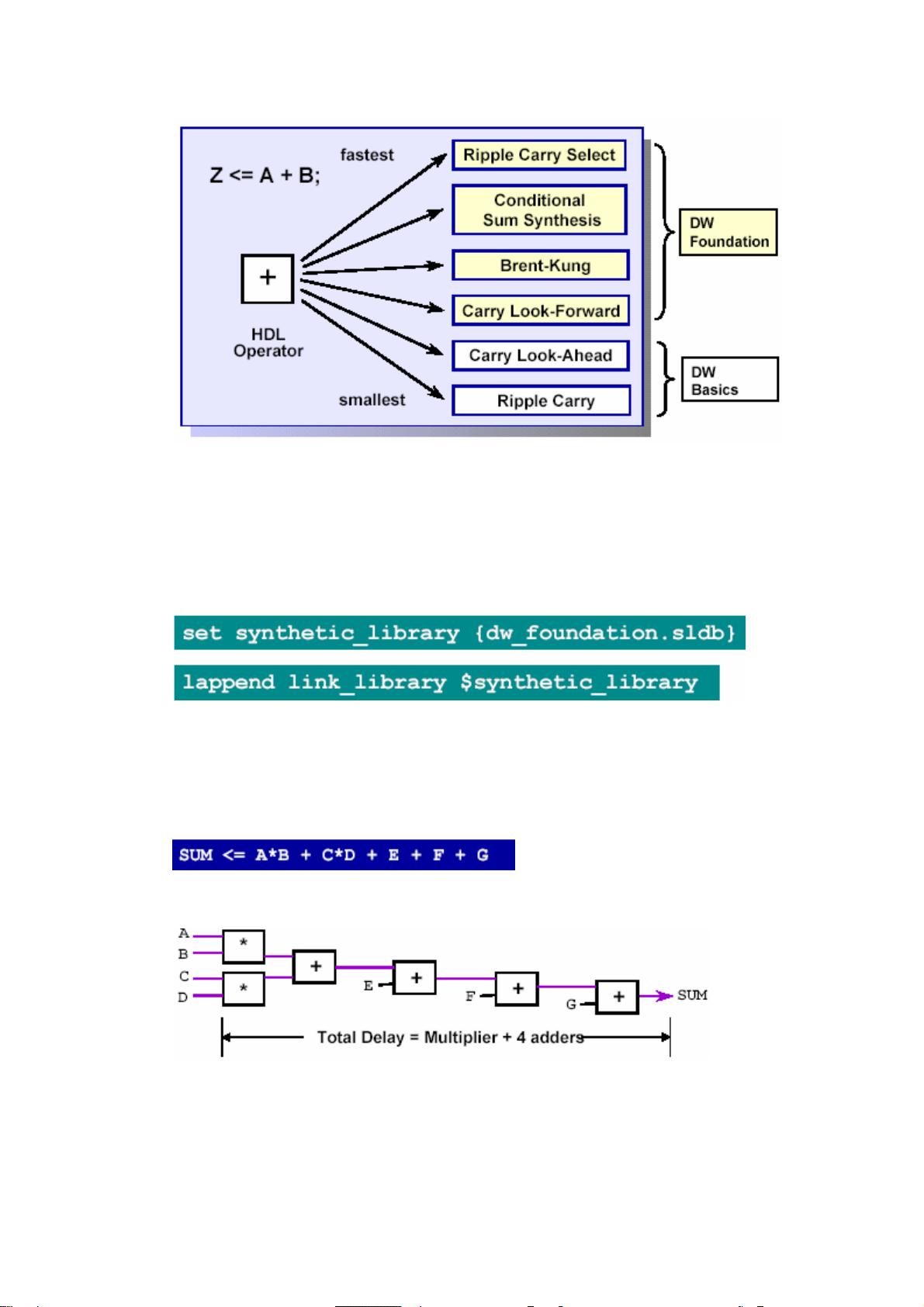

在综合的整个过程中,首先理解什么是综合至关重要。综合是一种设计策略,通过软件方法将行为描述转化为具体的门级电路,同时考虑功能、速度和面积等因素。综合包括三个主要阶段:转换、映射和优化。转换阶段将HDL代码转化为工艺无关的RTL级网表,接着映射阶段根据选定的工艺库将RTL网表具体化为门级电路,最后是优化阶段,根据设计约束调整电路以达到最佳性能。

逻辑级综合是最基础的形式,设计者通过布尔表达式表示电路逻辑,使用元件例化技术定义触发器和锁存器等基本单元。例如,一个加法器可能在这个级别被描述为一系列的逻辑门组合。这种级别的综合虽然直观,但并不直接对应于最终的电路布局,如图3所示的综合后的网表,逻辑级描述已经包含了部分设计细节。

而RTL级综合则更进一步,它利用HDL特有的运算符和语句来表达电路的数学运算和行为功能,这使得设计更加模块化和易于理解和调试。相比于逻辑级,RTL级描述更接近实际的电路实现,综合后的网表更为清晰地反映出电路的结构和连接。

综合的层次随着抽象度的提高而降低,设计者对底层硬件的控制力减弱,从逻辑级到RTL级再到行为级,每个层次都对应不同的综合策略和工具。行为级综合是最顶层,通常用于快速原型设计,通过描述系统的行为和接口,由工具自动生成底层电路。

Design Compiler作为核心工具,能够高效地处理这些综合任务,但它也需要与设计者对电路性能和约束有深入的理解,以便做出最佳的综合决策。综合是将抽象的硬件描述转化为物理实现的关键步骤,而Design Compiler在这个过程中扮演了不可或缺的角色。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-01-09 上传

2023-10-23 上传

2016-04-27 上传

2021-02-23 上传

137 浏览量

2024-03-04 上传

GGGGGG9

- 粉丝: 0

- 资源: 2

最新资源

- 1-formularz-html5

- 电子功用-油浸式电力变压器匝间绝缘试验模型线圈

- phonebook

- ui-landing-bot:用原生Vanilla JavaScript编写的Landbot克隆。 死了简单而没有依赖性,只是纯粹的喜悦!

- calcite-components-svelte-example

- temuulenj.github.io

- hapi-google-oauth2-certs:用于管理 Google oAuth2 证书的 Hapi 插件

- KM-MiniProgram:迷你程序,用于保存内存

- campay-python-sdk:适用于CamPay付款网关的Python SDK

- 19041.789-ok-rdpwrap.zip

- wnarhi.github.io:刺激库

- ember-cli-groundskeeper:地面管理员的 Ember-CLI 插件

- strong-data-uri:数据解析器和编码器

- 雷克斯

- get_shirt_hot_with_splunk:学习Splunk培训模块

- Dochameleon:渐进式静态网站生成器