8086/8088微处理器:结构与系统详解

8086/8088微处理器是Intel公司于1978年推出的一款16位微处理器,它的设计和结构对后续的x86架构有着深远的影响。这款处理器因其简单性和易理解性,成为了计算机系统设计和教学的重要基础。

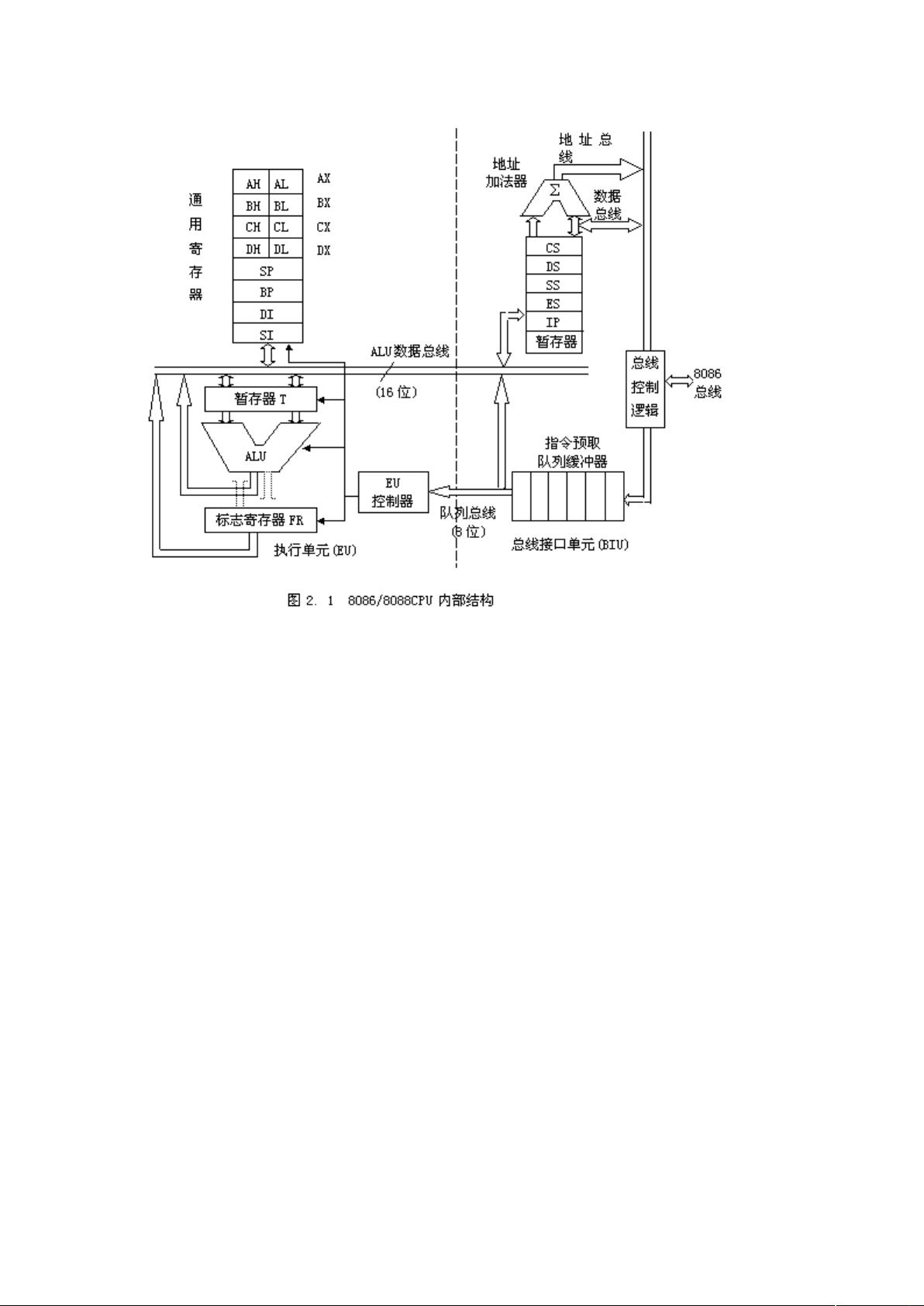

1. 8086微处理器结构:

- CPU内部由两大部分构成:总线接口部件(BIU, Bus Interface Unit)和执行部件(EU, Execution Unit)。BIU负责与外部总线交互,包括地址、数据和控制信号的管理;EU则负责指令的执行和运算。

- CPU寄存器包括通用寄存器(如AX, BX, CX, DX, SI, DI, SP, BP)、段寄存器(CS, DS, ES, SS)、标志寄存器(FLAGS)以及指令指针寄存器(IP)。通用寄存器用于临时存储数据,段寄存器用来定义内存段的起始地址,标志寄存器记录了运算结果的状态,IP则存放了下一条要执行指令的偏移地址。

- CPU引脚包括公用引脚、最小模式控制信号引脚和最大模式控制信号引脚。这些引脚定义了处理器与外部硬件的通信方式,例如,控制信号引脚决定了8086工作在最小模式(直接由CPU控制总线)还是最大模式(需要总线控制器协调总线操作)。

2. 8086微机系统存储器结构:

- 存储器地址空间:8086具有20位地址线,可以寻址1MB的内存,但因为采用分段机制,实际可访问的逻辑地址范围小于1MB。

- 数据存储格式:8086使用16位数据线,支持半字节、字节和双字数据传输。

- 存储器分段:通过四个段寄存器(CS, DS, ES, SS)与16位的段偏移地址组合,形成20位的物理地址。每个段可以看作独立的64KB内存区域。

3. 8086微机系统I/O结构:8086有专门的I/O端口地址空间,通过IN和OUT指令与外部设备交互。

4. 最小/最大模式系统总线的形成:最小模式下,CPU直接控制总线,所有总线信号由CPU生成;最大模式下,总线控制器(如8288)用于协调多个器件对总线的访问。

5. CPU时序:8086的运行基于复杂的时序,包括T状态,每个时钟周期可能包含多个T状态,用于读取指令、执行操作和刷新内存。

6. 最小模式系统中8086CPU的读/写总线周期:读周期中,CPU先发出地址,然后等待数据从存储器或I/O端口传回;写周期则是CPU先给出地址和数据,再进行数据传输。

学习8086/8088微处理器有助于理解现代计算机体系结构的基础,特别是对于那些需要深入研究x86平台的软件开发者和系统设计师来说,它是不可或缺的知识。同时,通过比较不同模式下的系统总线操作,可以更好地理解计算机系统中多组件协同工作的原理。通过掌握8086的引脚功能、存储器读写时序以及最小/最大模式,可以为理解和设计更复杂系统奠定坚实基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

bao532834121

- 粉丝: 0

- 资源: 1

最新资源

- oracle常用经典sql查询

- JSP+oracle数据库编程中文指南

- PCA特征提取K均值聚类matlab代码

- sql语句大全2是1的补充

- 天书夜读(完整版)PDF版

- 本人提供SQL语句大全(转载) 12009年04月28日 星期二 19:35SQL语句大全(转载)

- SWT-JFace-in-Action.pdf

- MyEclipse 6 开发中文手册

- ActionScript_3.0_Cookbook_中文版

- spring开发指南电子书

- cookie的简单操作

- 预处理命令的学习心得.txt

- xml期末考试试题 xml期末考试试题

- struts国际化的使用

- 仓库温湿度的监测系统论文

- Weblogic管理指南