Cadence SIP设计详解:系统级别封装技术与流程

需积分: 49 32 浏览量

更新于2024-07-06

1

收藏 2.7MB PDF 举报

"Cadence17.2-2016-SIP-系统级别封装.pdf"

本文档详细介绍了Cadence软件在系统级封装(SIP)设计中的应用,重点关注了SIP的特点、优势以及设计流程。SIP(System in Package)是一种半导体封装技术,它将多个不同的半导体芯片和无源器件集成在一个封装内,以实现更高效的功能性器件。这种技术具有以下显著特点:

1. 多芯片集成:允许不同类型的IC在同一封装内组合。

2. 工艺兼容性:支持不同工艺的IC协同工作。

3. 活动与无源器件混合:可同时包含有源和无源组件。

4. 自由组合:内部组件可以根据需求灵活配置。

5. 性能提升:通过减少互连距离,提高了器件的性能。

6. 埋入式组件:基板中可嵌入有源或无源器件。

7. SOC集成:可集成一个或多个系统级芯片(SOC)。

SIP设计的优势在于:

1. 成本效益:通过减少封装数量和材料节省成本。

2. 密度高:更高的组件密度降低了封装尺寸。

3. 高性能:更短的信号路径导致更好的信号完整性和更低的延迟。

4. 低功耗:通过减少外部互连,降低功耗。

5. 缩短设计周期:更快的设计和验证过程。

6. 灵活性:易于适应变化的设计需求。

Cadence SIP设计流程涵盖以下几个关键步骤:

1. 系统设计:定义系统需求和功能布局。

2. 原理图设计:创建电路原理图,包括元器件布局和连接。

3. SIP设计:使用约束和规则驱动的方法进行基板设计,包括DIE创建、IC与封装的连接优化、倒装焊工艺应用以及三维设计规则检查。

4. 基板制造:根据设计制造封装基板。

5. 封装:组装芯片和无源器件到基板上。

6. 性能/功能验证:测试封装后的器件性能和功能。

7. 判断:如果验证成功,则进入批量生产;若存在问题,返回原理图设计阶段进行修改。

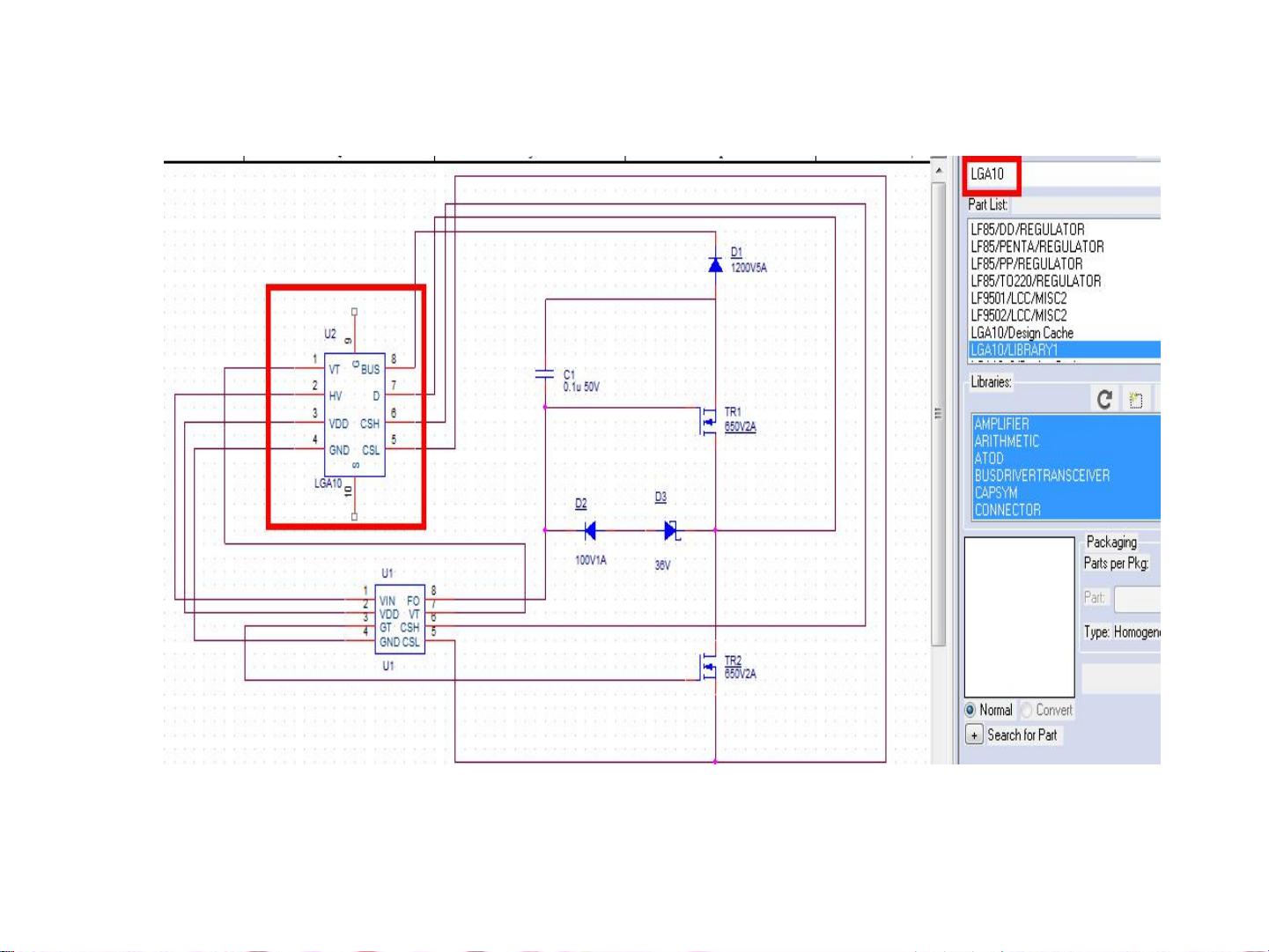

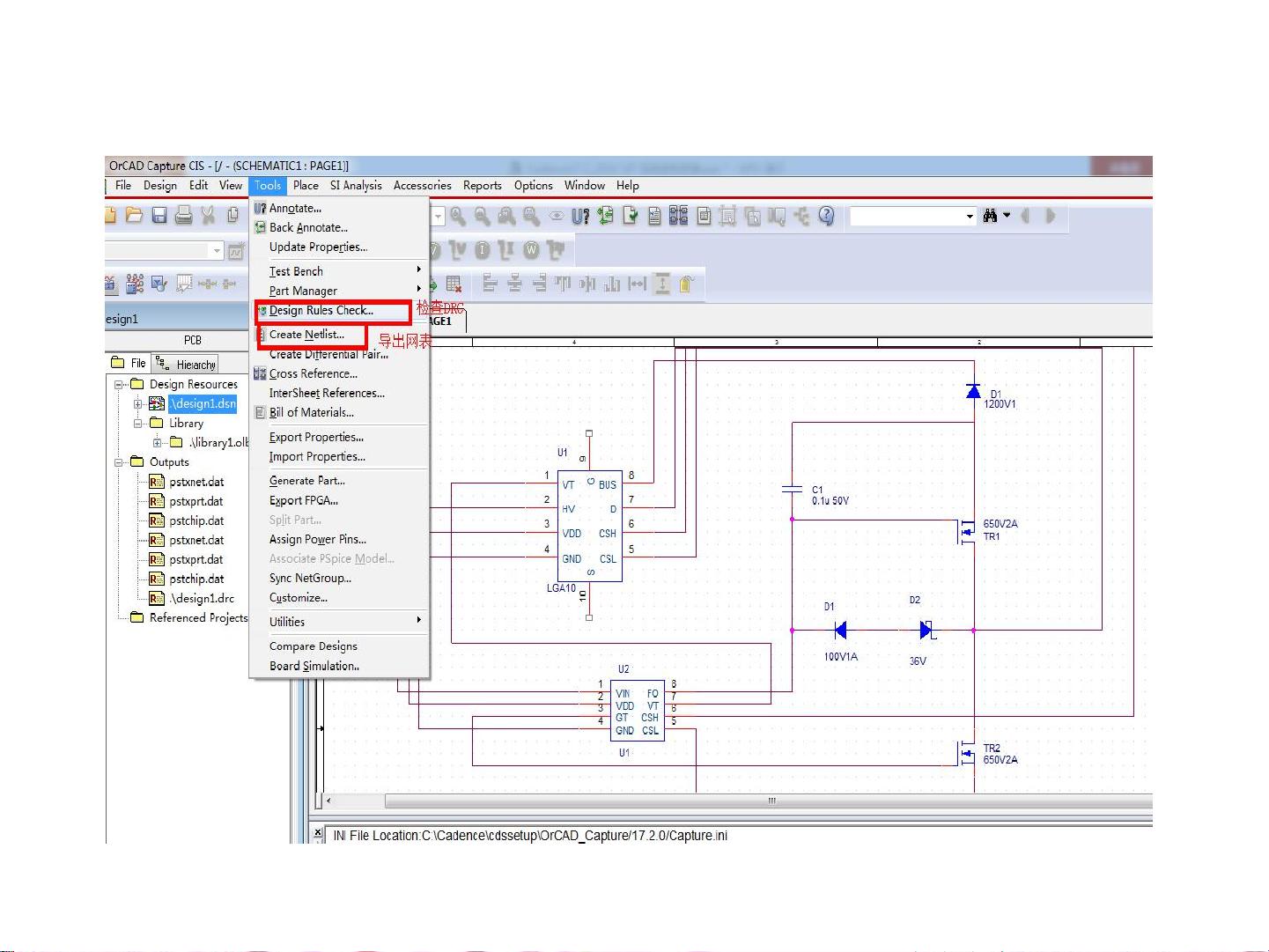

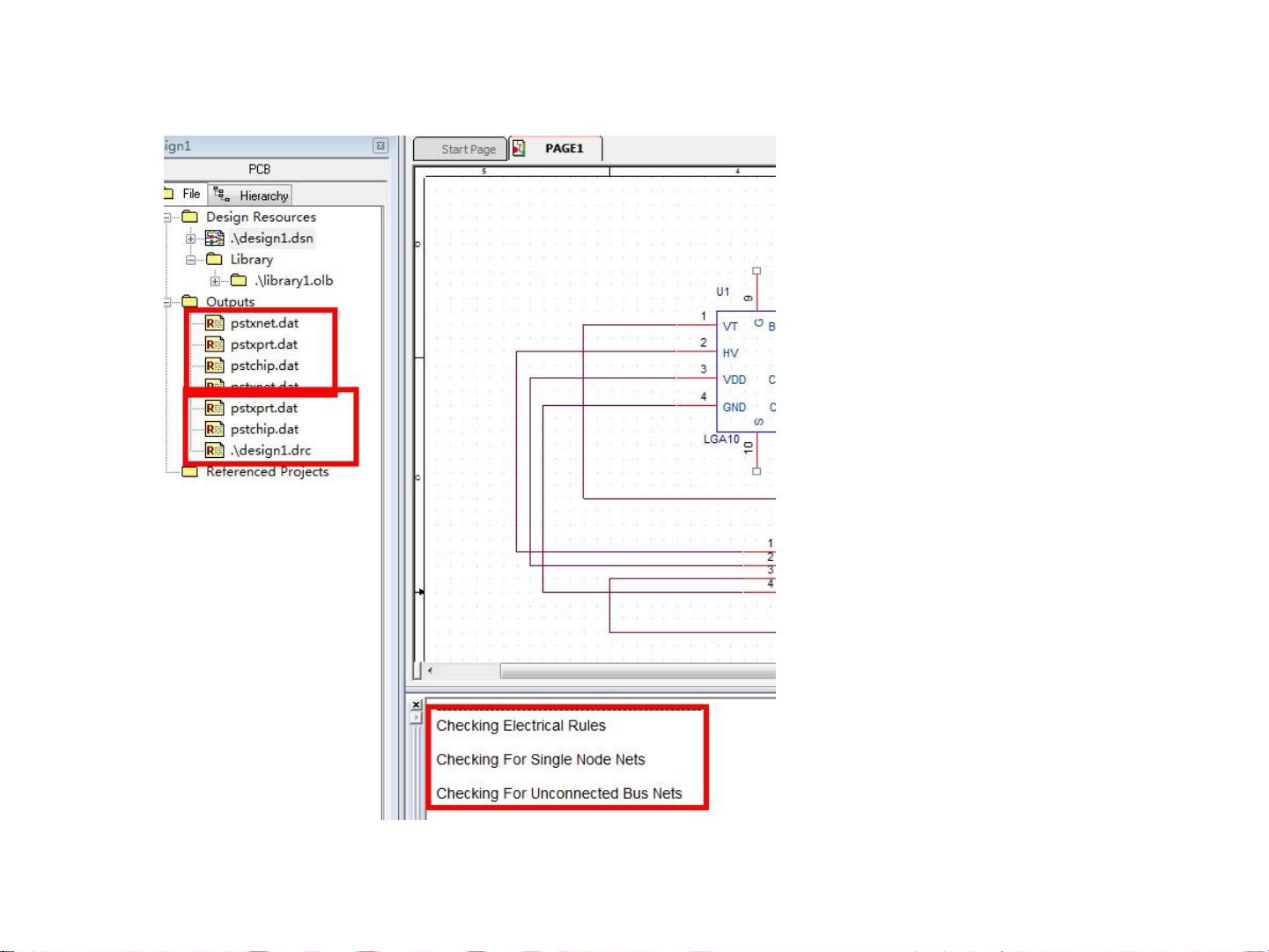

在原理图设计阶段,需创建和编辑PAD(焊盘),包括通孔、SMD焊盘、DIE焊盘和Bondwire焊盘,它们有不同的形状如圆形、方形和长方形。此外,还需建立工程文件、原理图和元器件库,并利用ORCAD工具进行新元器件的制作,添加PIN引脚。设计完成后,进行设计规则检查(DRC)并导出网表。焊盘制作时,需要设置合适的尺寸、形状和层信息,并保存封装设置。最后,在PKGdesign设计模块中进行SIP设计系统的创建和配置。

总结来说,Cadence 17.2-2016-SIP系统级别封装解决方案提供了一套全面的工具集,支持高效、灵活的SIP设计,从而满足现代电子设备对小型化、高性能和低功耗的需求。

2020-10-26 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2016-12-01 上传

131 浏览量

点击了解资源详情

点击了解资源详情

hjf09

- 粉丝: 0

- 资源: 1

最新资源

- Wrox.Professional.VSTO.2005.Visual.Studio.2005.Tools.for.Office.May.2006.pdf

- Ajax简单实例.doc,看题目

- C_的高校图书资料管理系统的设计.pdf

- 应用单片机设计数字电容表

- 常用js判断上一页的来源.txt

- adfasdfasdfasdfa

- ActionScript 3.0 Cookbook 中文版.pdf

- Qtopia 编译过程

- matlab辅导材料

- 用推送技术动态更新页面内容.doc

- SAP高级编程指南--abap351

- 我国机械行业核心竞争力

- C程序设计语言_第2版新版

- logistic映射分岔图的四种实现方法

- 模拟FAT文件系统的设计与实现

- Java2阶段测试,适合初学者做