基于FPGA的宽频带DPLL设计:精度提升与抗噪优化

14 浏览量

更新于2024-08-31

收藏 462KB PDF 举报

宽频带数字锁相环(DPLL)是一种在现代通信和电子技术中广泛应用的精密信号处理系统,特别是在数字通信、无线通信等领域发挥着关键作用。相比于传统的模拟锁相环路,DPLL具有显著的优势,如更高的精度、更好的稳定性(不受温度和电压变化的影响)、灵活的频率和带宽调整能力,以及易于构建多级锁相环结构。

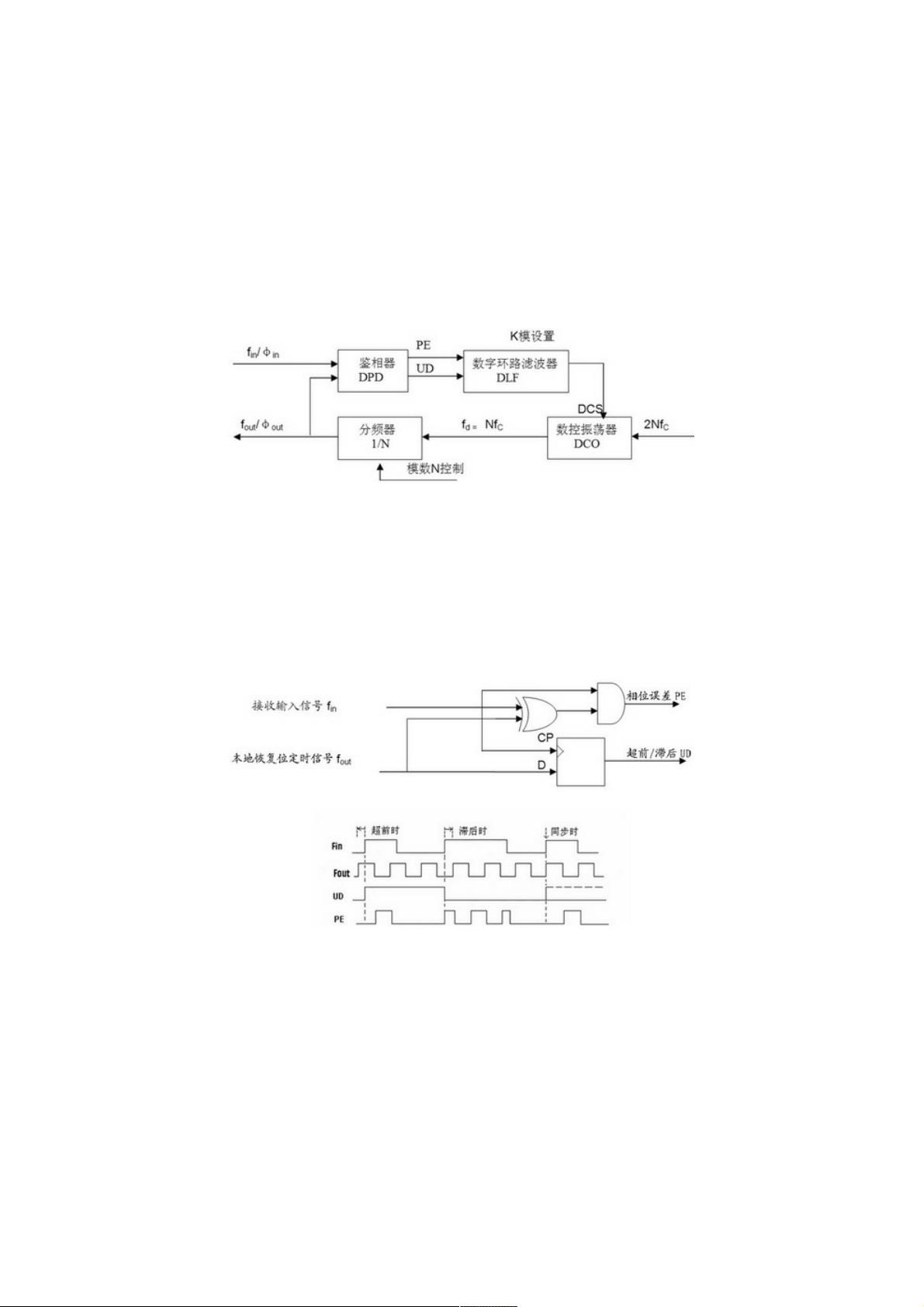

DPLL的核心组成部分包括数字鉴相器和数字环路滤波器。数字鉴相器,如异或门(XOR)鉴相器或改进型异或门ECPD,用于检测本地时钟与输入信号之间的相位偏差。在位同步DPLL中,特殊设计的鉴相器能有效排除连续位保持不变带来的干扰。改进型异或门鉴相器输出的PE脉冲信号反映了相位误差,通过比较本地时钟与输入信号的上升沿位置来确定。

数字环路滤波器,通常采用变模可逆计数器作为实现,其模数K决定了滤波器的特性。该计数器根据鉴相器的输出PE进行加减运算,以减小高频噪声引起的相位抖动。适当选择的模值K可以平衡抗噪性和捕捉性能:增大模值K可以提高抗噪性但增加捕捉时间,减小模值K则缩短捕捉时间但牺牲抗噪能力。本文设计中选择了K=4,以确保在初始状态下,计数器能提供良好的性能。

FPGA(现场可编程门阵列)在DPLL的实现中扮演了重要角色,因为它提供了高度的灵活性和集成度。通过FPGA,可以设计出高性能、高密度的数字锁相环路,将环路的各个部分如鉴相器、滤波器以及相关的控制逻辑整合在同一芯片上,这不仅简化了硬件设计,还提高了系统的可靠性和实时性。

总结来说,宽频带数字锁相环的设计和基于FPGA的实现,是现代电子系统设计中的关键技术,它结合了数字信号处理的优势,通过精密的鉴相和滤波技术,以及FPGA的高度可编程特性,实现了高效、稳定的信号同步和频率跟踪。理解并掌握这一技术对于从事相关领域的工程师来说至关重要。

2021-07-13 上传

2021-09-16 上传

2020-10-16 上传

2009-07-19 上传

2020-10-19 上传

2021-07-13 上传

2021-09-15 上传

点击了解资源详情

点击了解资源详情

weixin_38563552

- 粉丝: 2

- 资源: 877

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案