单片机与单片机与DSP中的非均匀采样硬件设计中的非均匀采样硬件设计

非均匀采样系统的实现可以包括两个方面: (1)对信号进行非均匀采样得到非均匀采样信号; (2)

进行非均匀采样算法处理。 前一个方面主要是硬件实现的问题,即如何在硬件上实现对信号的非均匀采

样,后一个方面主要是选择合适的处理算法,以便对信号进行适当的处理,得到所需的结果。 从一般意义

上来看,信号的每个采样点需要两个量来代表:采样值大小和采样时间。对于均匀采样,由于任何两个采样点

的间隔都是相等的,因此,均匀采样只需要记录采样值和标记采样点的顺序即可。但是,对于非均匀采样,由

于采样点的间隔是不相等的,因此,非均匀采样除了要记录采样值大小以外,还需要记录采样时间。在实际实

现中,非

非均匀采样系统的实现可以包括两个方面:

(1)对信号进行非均匀采样得到非均匀采样信号;

(2)进行非均匀采样算法处理。

前一个方面主要是硬件实现的问题,即如何在硬件上实现对信号的非均匀采样,后一个方面主要是选择合适的处理算法,

以便对信号进行适当的处理,得到所需的结果。

从一般意义上来看,信号的每个采样点需要两个量来代表:采样值大小和采样时间。对于均匀采样,由于任何两个采样点

的间隔都是相等的,因此,均匀采样只需要记录采样值和标记采样点的顺序即可。但是,对于非均匀采样,由于采样点的间隔

是不相等的,因此,非均匀采样除了要记录采样值大小以外,还需要记录采样时间。在实际实现中,非均匀采样必须考虑如何

在特定的时间点上进行采样,这在对采样时间的精度要求很高时,会非常难以实现。比如,要对1GHz的正弦信号进行采样,

则采样时间的精度就必须是几个ps。

对信号进行非均匀采样的关键是如何精确控制ADO进行采样。有两种方法可以采用:(1)产生非均匀的采样时钟送往

ADC;(2)ADO的采样时钟是均匀时钟,但是,通过控制ADO什么时候开始工作来实现非均匀采样。这两种方法都需要非

均匀的控制信号。按照非均匀采样的理论,每个采样点的采样时间应该是完全随机的,但是这在实际实现中是不可能的或者很

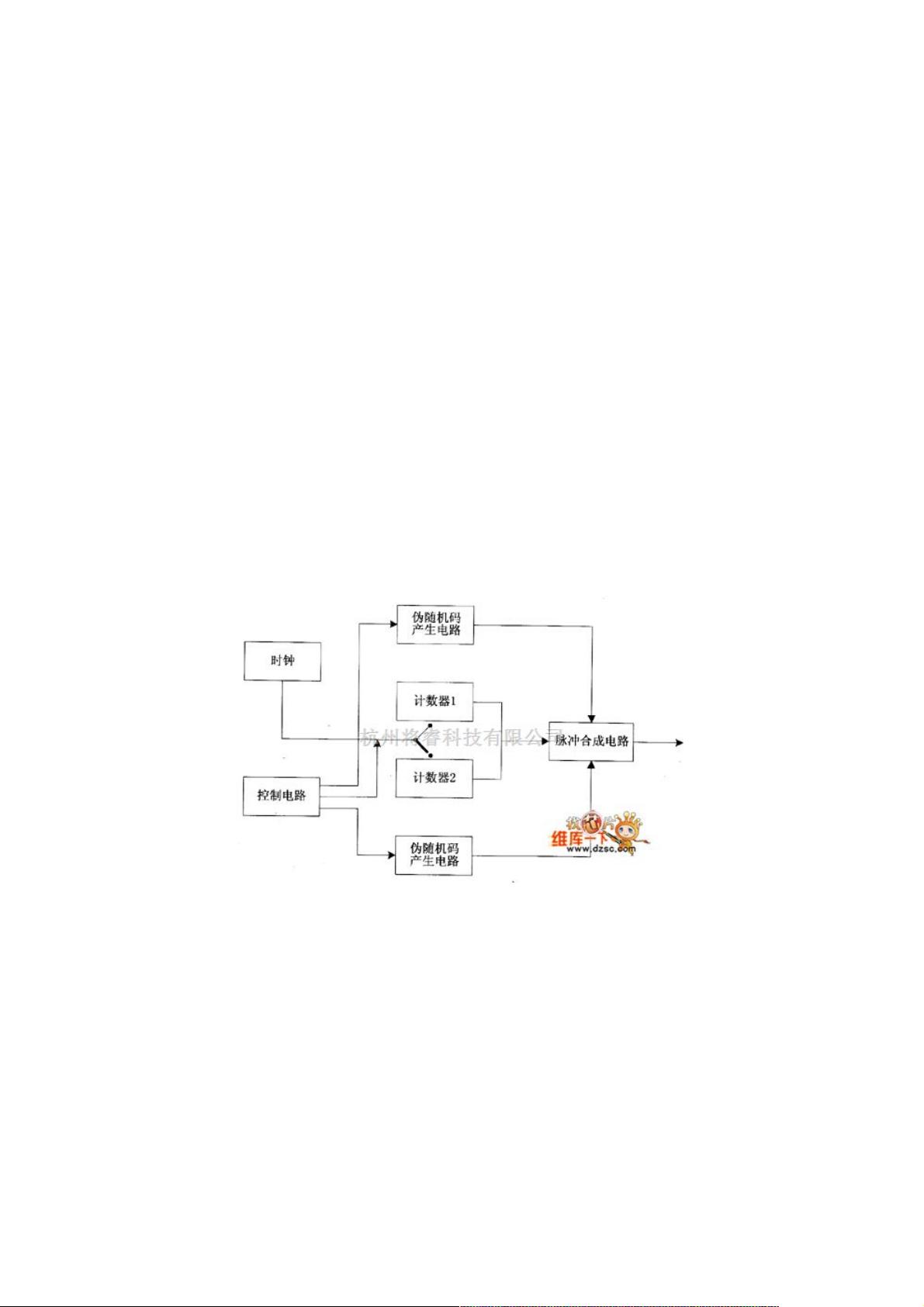

难实现。因此,可以选择伪随机采样脉冲或者伪随机控制信号。伪随机采样脉冲或者伪随机控制信号的实现如图1所示。

图1 伪随机采样脉冲产生电路

图1中,两个伪随机码产生电路产生伪随机码序列,分别送往计数器1和计数器2,作为计数器的预设值;计数器对高频时

钟进行计数,当计数器溢出时,就会产生一个脉冲;控制电路实现控制计数器1和计数器2的切换。由于伪随机码产生电路产

生的数值是伪随机的,因此计数器输出脉冲的宽度也是伪随机的。最后,两个计数器产生的伪随机脉冲经过脉冲合成电路,形

成所需要的伪随机采样脉冲或者伪随机控制信号。

根据上面的论述,非均匀采样系统的实现框图如图2所示。

非均匀采样系统的硬件采用DSP和CPLD(可编程逻辑器件)精确控制AD的采样时间,实现非均匀采样,在DSP中进行

信号分析和处理,得到非均匀采样信号的频谱。硬件系统总框图如图3所示。