FPGA实现的Viterbi译码器:高效通信系统关键组件

80 浏览量

更新于2024-09-01

收藏 207KB PDF 举报

在现代通信系统中,特别是卫星通信和无线通信中,卷积码因其高效的纠错能力和广泛应用而备受关注。Viterbi译码器作为一种基于Viterbi算法的译码器,对于这些系统的性能提升起到了关键作用。Viterbi算法是最大似然译码策略,在码的约束度较低时,它的性能优于其他概率译码算法,体现在更高的解码效率和更快的速度上,且其硬件实现相对简单。

FPGA(Field-Programmable Gate Array),作为可编程逻辑器件,因其高度的灵活性、高密度、低功耗、快速设计周期以及成本效益高等优点,逐渐成为Viterbi译码器设计的理想平台。利用FPGA实现Viterbi译码器的优势在于可以定制化设计,适应不同的应用场景,并且能够在硬件层面实时调整,无需重新制造。

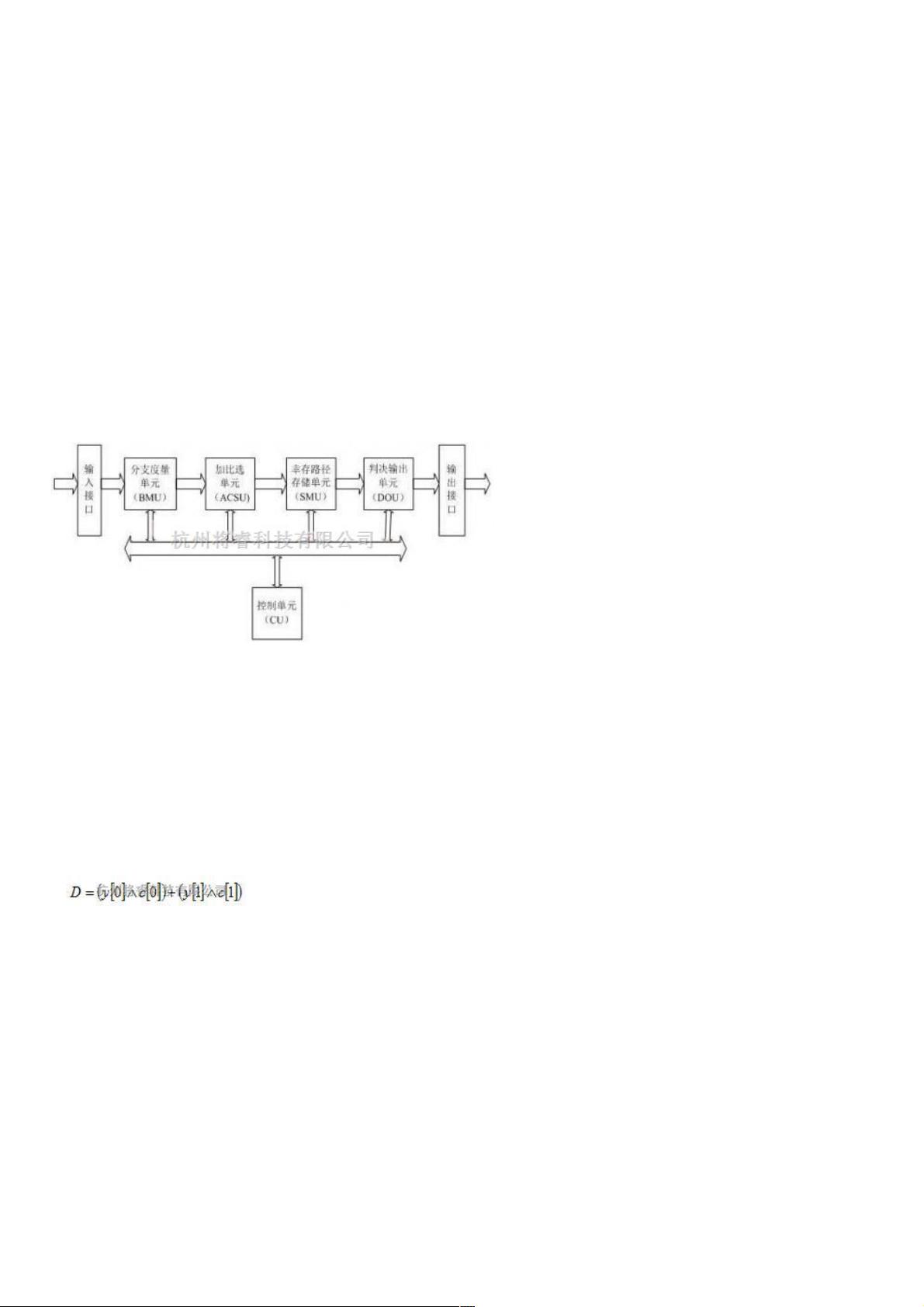

Viterbi译码器的核心功能包括五个关键组件:分支度量单元(Branch Metric Unit)、加比选单元(Add-Compare-Select Unit)、幸存路径管理单元(Survivor Management Unit)、判决输出单元(Decide-Output Unit)和控制单元(Control Unit)。这些单元协同工作,接收输入二进制数据,计算并存储路径信息,进行路径比较和选择,以确定最有可能传输正确的数据序列。

具体来说,输入数据通过分支度量单元计算出各个可能路径的分支距离,加比选单元负责比较这些距离并选择最优路径,幸存路径管理单元负责存储并管理这些路径,避免信息丢失,而判决输出单元则基于加比选的结果输出最终的译码结果。控制单元则协调整个译码过程,确保算法的正确执行。

在实际的FPGA设计中,译码器的实现会涉及到硬件描述语言(HDL)如Verilog或 VHDL 的编写,通过描述这些逻辑功能的流程和交互,然后在FPGA芯片上进行逻辑布局和优化。此外,设计者还需考虑FPGA资源的分配,如查找表(LUTs)、触发器(Flip-Flops)和布线资源,以确保译码器的性能和功耗达到预期。

总结来说,这个项目旨在利用FPGA技术设计和实现Viterbi译码器,结合卷积码的高效性与FPGA的灵活性和高性能,以提升通信系统的可靠性和实时性。这个设计不仅体现了理论知识的实际应用,也为未来的通信系统集成和优化提供了新的思路。

122 浏览量

267 浏览量

205 浏览量

105 浏览量

124 浏览量

127 浏览量

150 浏览量

176 浏览量

200 浏览量

weixin_38707061

- 粉丝: 2

- 资源: 921