VHDL实现正弦波发生器设计

需积分: 9 105 浏览量

更新于2024-09-19

收藏 58KB DOC 举报

"基于VHDL的正弦波发生器设计示例"

正弦波发生器在数字信号处理和通信系统中扮演着重要角色,用于产生模拟正弦波信号的数字版本。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种用于描述数字逻辑系统的硬件描述语言,常用于FPGA(Field Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)的设计。本设计是利用VHDL来实现一个正弦波发生器。

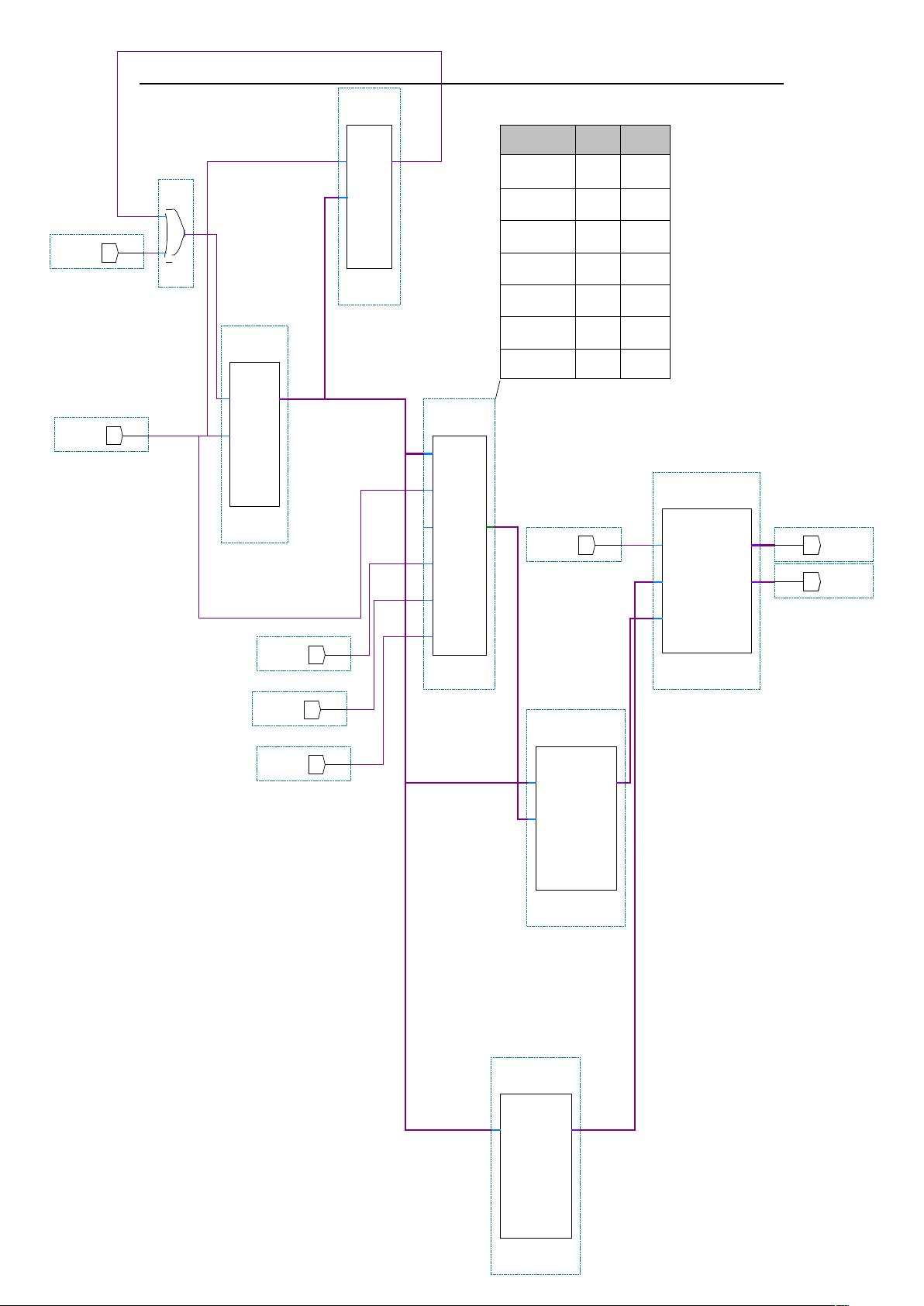

VHDL代码由多个组件组成,包括累加器(acum)、选择器(xuanze)和可能的其他辅助模块。累加器通常用于生成连续的相位增量,而选择器则根据累加器的结果来选择合适的幅度值,从而形成正弦波形。

在给出的代码中,`acum`实体定义了一个累加器,它有三个输入端口:`sum1`(累加结果输出),`clr`(清除信号)和`clk`(时钟信号)。累加器的架构内部使用了一个12位的寄存器`reg12`和一个12位的加法器`adder12`。`reg12`在时钟信号`clk`上升沿时更新其输入`temp1`到输出`temp0`,并在清除信号`clr`为高时清零。加法器`adder12`接收输入信号`temp0`和`temp1`,并将它们相加后的结果输出到`temp0`。

`xuanze`实体则是一个选择器,它有两个输入`dz`和`shuju`,以及一个输出`shuchu`。在`xuanze`的架构中,`rt`信号存储了输入`shuju`的值,当`dz`大于"01000"(二进制数,对应十进制的8)时,`rt`取反,这可能用于生成正弦波的负半周期。最后,`shuchu`输出`rt`的值。

为了生成正弦波,累加器需要不断累加一个固定的步长,步长与频率和采样率有关。累加器的输出通过某种映射关系(例如查表或者使用查找器)转换为对应的幅度值,这些幅度值组合起来就形成了正弦波的离散表示。选择器的作用可能是根据累加器的输出决定当前输出点的正弦值的符号。

在实际应用中,可能还需要对这个基本结构进行优化,比如增加分频器来调整频率,使用更复杂的查表机制以提高精度,或者使用滤波器平滑输出以得到更平滑的正弦波形。VHDL提供的这种模块化设计方法使得正弦波发生器可以灵活地适应各种需求,并且便于在不同硬件平台上实现。

397 浏览量

377 浏览量

575 浏览量

151 浏览量

627 浏览量

925 浏览量

319 浏览量