运用VerilogHDL设计256字节MIPS32单端口RAM存储器实验报告

需积分: 0 57 浏览量

更新于2024-08-04

收藏 656KB DOCX 举报

本实验报告是关于“存储器设计实验”的一部分,由学生於文卓在2019年4月22日完成,他的学号为17061833,属于计算机科学与技术专业,班级为17052317,课程名称为“计算机组成原理课程设计”。实验的任课教师和指导教师均为冯建文。本次实验的主要目标包括:

1. 掌握Verilog HDL技术:学生需学习如何运用Verilog硬件描述语言(Hardware Description Language)进行行为描述和建模,这是现代数字逻辑设计的关键工具。

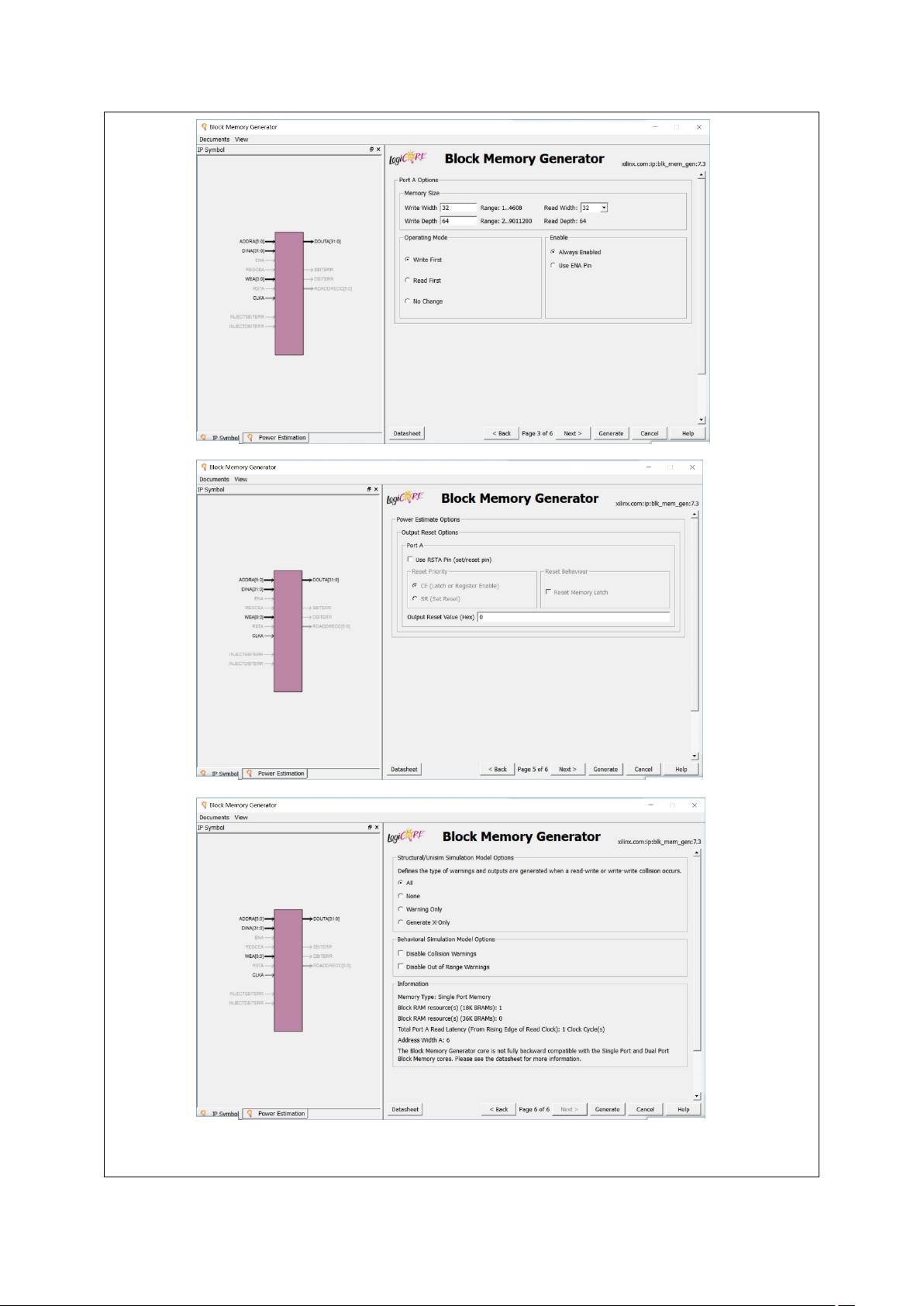

2. 利用Memory IP核:实验要求学生学习如何使用预先设计的存储器IP核心,这有助于快速实现复杂的存储器结构,提升设计效率。

3. 理解存储器结构与原理:通过实验,学生将深入理解单端口RAM(随机存取存储器)的内部工作原理,包括其数据组织方式(按字节编制、按字访问)以及读写操作。

4. 具体设计任务:目标是设计一个256字节容量的单端口RAM,支持MIPS32架构,并进行仿真验证和实际硬件板级验证。这涉及硬件设计的实践应用,包括模块实现、接口设计和功能测试。

5. 验证模块编写:学生需要编写顶层验证模块,通过调用设计好的RAM存储器模块,确保其功能正确无误,这是软件和硬件协同工作的关键环节。

这个实验不仅考验了学生的编程技能,还锻炼了他们对计算机系统内部组件的理解,以及理论知识与实际工程项目的结合能力。通过完成这个实验,学生将能增强自己的硬件描述语言设计和存储器设计技巧,为后续的计算机体系结构或嵌入式系统课程打下坚实基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-14 上传

2021-09-29 上传

2011-07-04 上传

2022-05-07 上传

2022-09-24 上传

Xhinking

- 粉丝: 29

- 资源: 320

最新资源

- 液体点滴速度监控装置(F题)

- 基于单片机的红外遥控自学习系统的设计

- 基于单片机的红外遥控信号自学习及还原方法

- 单片机开发及典型应用液晶显示 多种串口通讯 网络通讯 模糊控制

- 数据结构中关于多项式操作的代码

- Practical Programming in Tcl and Tk

- 单片机的数字时钟设计

- 硬件工程师必读攻略一 、数模混合设计的难点 二、提高数模混合电路性能的关键 三、仿真工具在数模混合设计中的应用 四、小结 五、混合信号PCB设计基础问答

- JavaScript实现日历控件

- 软件设计师历年试题分析与解答

- ASP环境下的安全技术分析

- 巴音郭楞职业技术学院OA办公自动化系统研究

- ISO-17799安全标准中文版.pdf

- asp.net常用函数表.doc

- VSS的安装过程,很详细

- g4lmod0.16