"存储器与CPU连接及交换数据的方法"

需积分: 4 44 浏览量

更新于2024-01-15

收藏 923KB PPT 举报

第7章的内容主要介绍了存储器和CPU之间的连接方式以及存储器的容量表示方法。

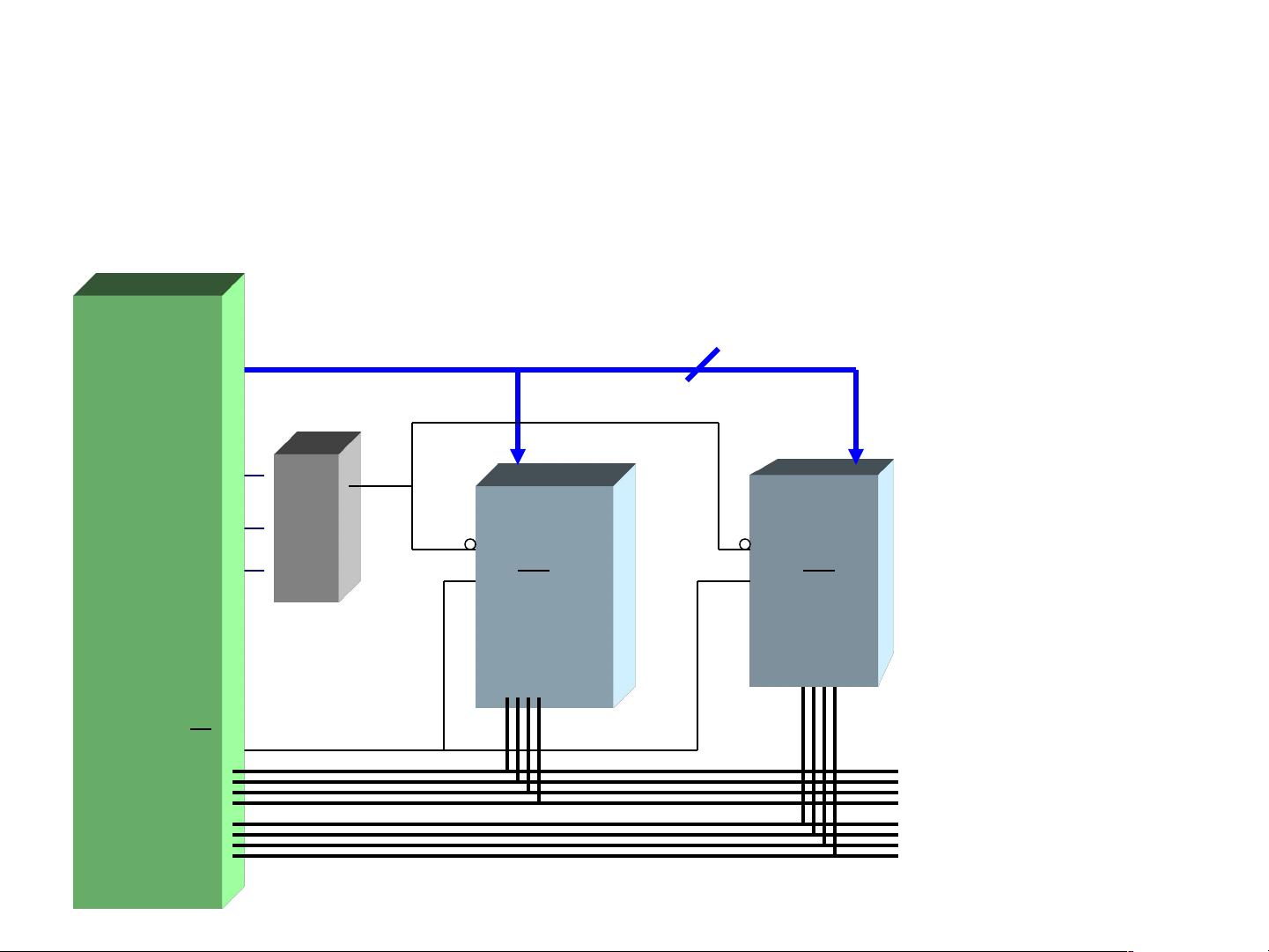

在连接方面,首先是地址线的设计。对于16位CPU而言,地址线需要16根,其中低位地址线A0-A11用于存储器芯片的选择和读写数据,高位地址线A12-A15进入译码器进行地址解码。通过地址解码,确定需要访问的存储器单元。

在存储器方面,静态存储器(SRAM)使用触发器线路来存储和读写数据。与动态存储器相比,静态存储器没有电容漏电的问题,不需要进行刷新操作。因此,静态存储器具有快速的读写速度,但体积较大,价格也较高。例如,对于一个4K*4的存储器芯片,其存储容量为4K,即2的12次方,共有212个存储单元,每个单元存储一个二进制数。

在连接的具体实现中,通过译码器将地址线进行解码,将存储器芯片的A13-A15连接到译码器的输入端,将A0-A12及其他控制信号(如CS、CSR、WR等)连接到存储器芯片的对应输入端。这样,存储器芯片的输出端(例如D0-D3)就可以与CPU进行数据交换。

对于指令的执行过程,以MOV AX,(0023H)为例。首先,CPU通过地址线将要读取数据的存储器单元的地址0023H发送给存储器芯片。存储器芯片根据地址解码,找到对应的存储单元,将其中的数据通过数据线(例如D0-D3)发送给CPU的AX寄存器,完成读取操作。

类似地,对于指令MOV(0023H),AX的执行过程相反。即CPU将AX寄存器中的数据通过数据线发送给存储器芯片的对应存储单元,存储器芯片根据地址解码将数据写入到地址为0023H的存储单元中。

总之,存储器和CPU之间的连接是通过地址线和数据线进行数据交换的。地址线用于选择存储器单元,数据线用于传输数据。存储器的容量可以通过存储芯片的表示方法来确定,其中K表示千(1000),2K表示2048。对于存储器容量较大的情况,可以使用译码器进行地址解码来选择具体的存储单元。

2022-03-05 上传

2011-05-02 上传

2010-05-24 上传

2023-05-28 上传

2023-05-28 上传

2023-06-09 上传

2023-06-09 上传

2023-04-24 上传

2023-05-18 上传

forsuperlovers

- 粉丝: 0

- 资源: 14

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码