8x8乘法器后端全流程详解:从Verilog到ASIC设计

需积分: 10 28 浏览量

更新于2024-07-23

4

收藏 5.58MB DOC 举报

本教程详细介绍了数字集成电路设计的后端流程,以一个8*8的乘法器为例,帮助读者理解从Verilog代码到实际版图的完整过程。首先,作者强调这只是一个基础教程,其目的是为了初学者快速掌握设计的基本流程,并非详尽无遗,可能存在一些错误和不完善之处,但足以作为入门学习的起点。

后端流程主要包括以下几个关键步骤:

1. 逻辑综合:将高级语言如Verilog的源代码转换为低级逻辑门级描述(LGD),这是设计的第一步,也是将抽象概念转化为物理实现的基础。

2. 形式验证:使用工具如Formality进行功能验证,确保代码在不同阶段(RTL代码和综合后的网表)的功能一致性。形式验证由于其高效性,在大规模设计中尤为重要,因为它能在短时间内完成大量的逻辑一致性检查,节省大量时间。

3. 静态时序分析(STA):通过Primetime进行布图前的时序分析,确保设计符合时序规范。如果发现时序问题,需要重新综合,直至满足规范要求。这一步骤对于ASIC设计至关重要,因为严格的时序控制直接影响芯片性能。

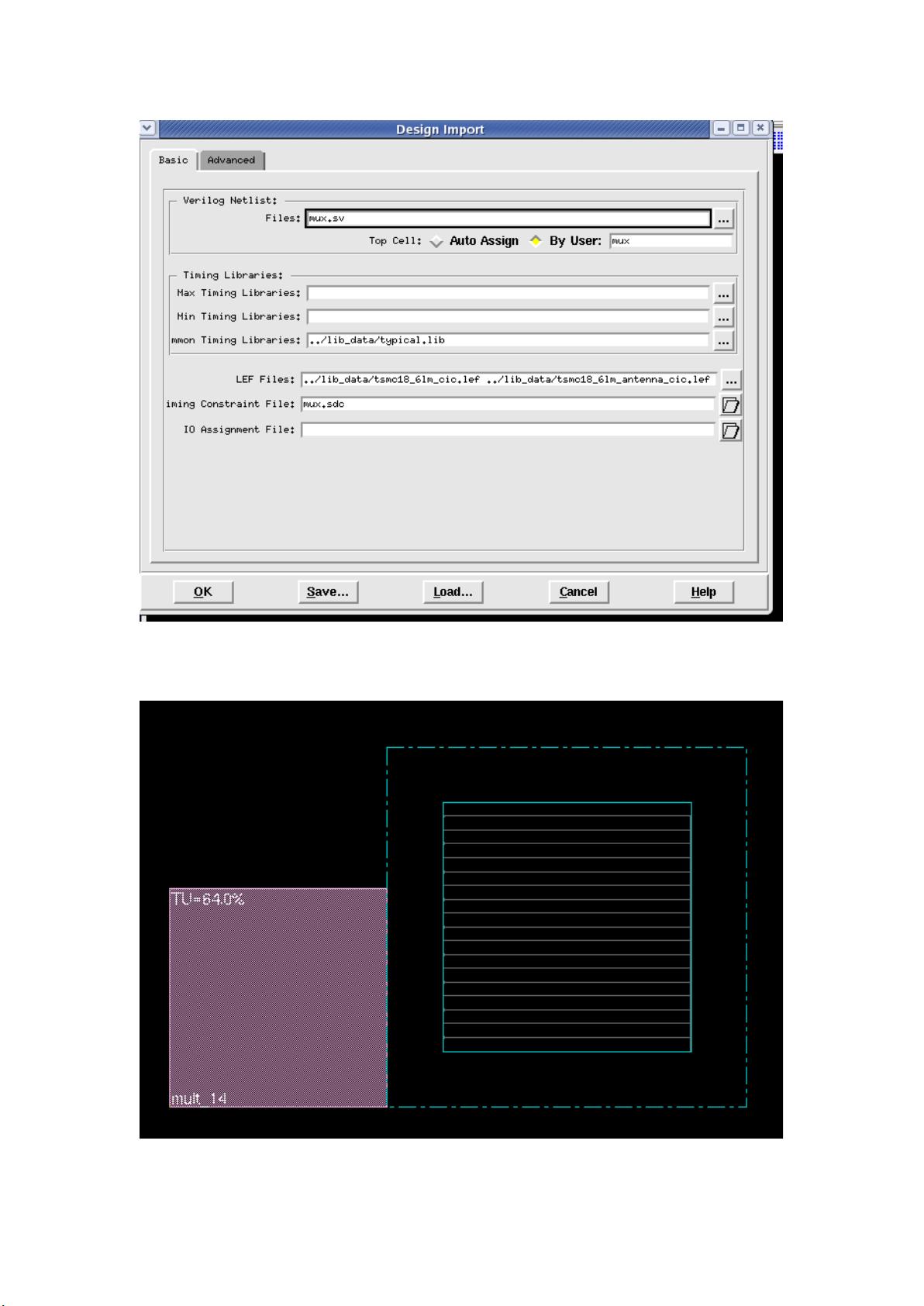

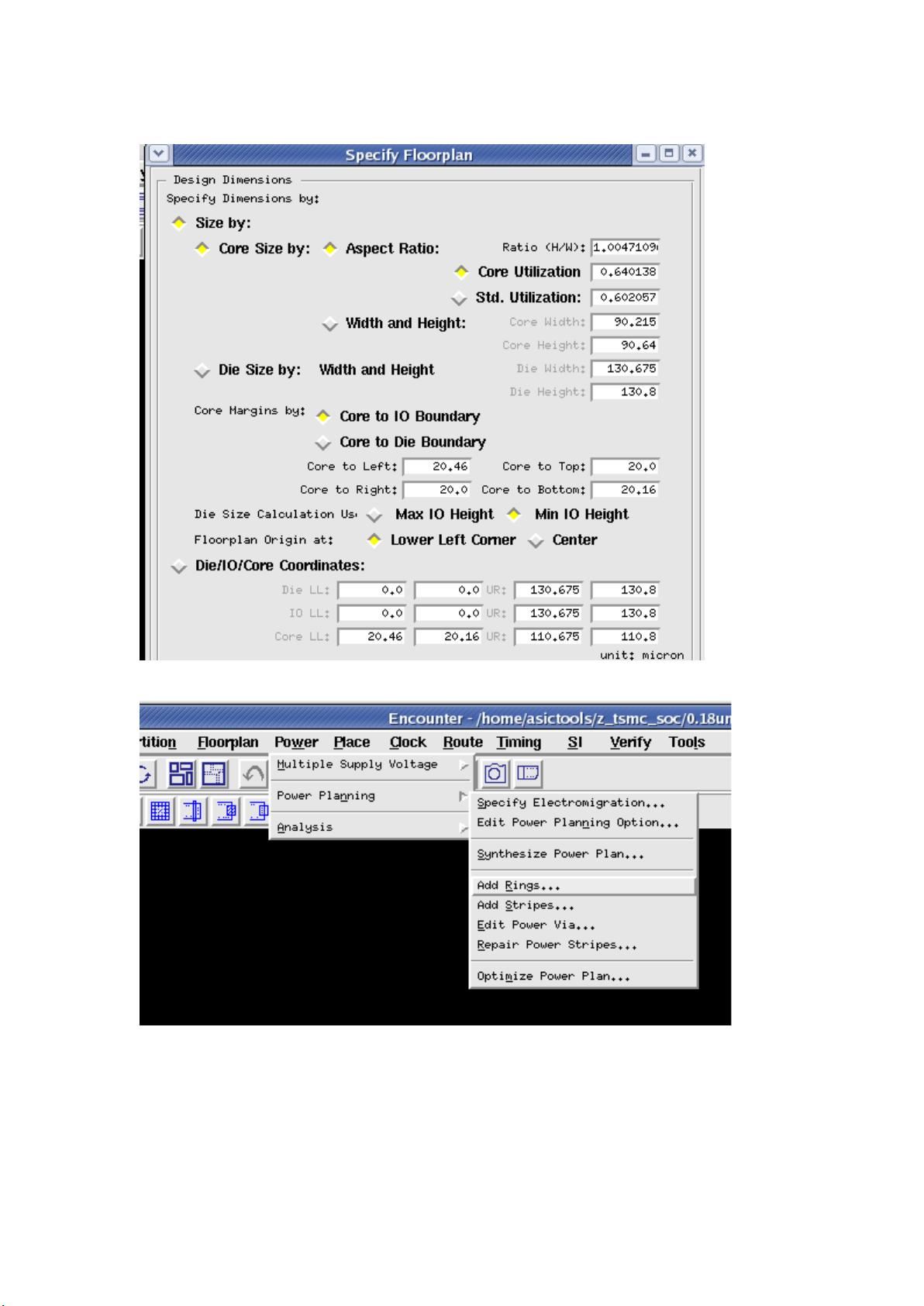

4. 自动布局布线(APR):使用Cadence的SOC Encounter自动化布局布线,优化电路的物理布局,减少寄生效应带来的延迟。

5. 时序迭代:在APR后,通过静态时序分析反复调整,直到达到预设的时序目标。这与芯片的具体布局密切相关,可能需要多次迭代。

6. 门级功能仿真:如果APR后满足功能要求,进行门级仿真以确认整体功能正确性。

7. DRC和LVS检查:实施差错检查,包括设计规则检查(DRC)和逻辑与物理一致性检查(LVS),通过后才能进入下一步。

8. 宏单元抽取:利用抽象技术(Abstract)提取8*8乘法器的硬宏(hardmacro),形成LEF文件,便于在其他设计中作为模块重用。

9. 宏单元集成:在顶层设计(top design)中集成抽取的宏单元,增强复用性和设计的模块化。

10. 芯片完整化:在第二次设计中,增加封装和引脚(PADs),使得设计成为完整的芯片,满足电气接口和封装需求。

11. 重复关键步骤:针对新的设计,再次进行逻辑综合、布局布线和时序分析,直至所有环节都符合要求。

这个教程以一个实际的乘法器设计为例,深入展示了数字后端流程的关键步骤,为后续的IC设计实践打下了坚实的基础。通过实践这些步骤,设计师可以逐步掌握并优化数字集成电路的设计流程。

568 浏览量

2646 浏览量

383 浏览量

267 浏览量

点击了解资源详情

383 浏览量

682 浏览量

hongtengyun

- 粉丝: 0

最新资源

- VB通过Modbus协议控制三菱PLC通讯实操指南

- simfinapi:R语言中简化SimFin数据获取与分析的包

- LabVIEW温度控制上位机程序开发指南

- 西门子工业网络通信实例解析与CP243-1应用

- 清华紫光全能王V9.1软件深度体验与功能解析

- VB实现Access数据库数据同步操作指南

- VB实现MSChart绘制实时监控曲线

- VC6.0通过实例深入访问Excel文件技巧

- 自动机可视化工具:编程语言与正则表达式的图形化解释

- 赛义德·莫比尼:揭秘其开创性技术成果

- 微信小程序开发教程:如何实现模仿ofo共享单车应用

- TrueTable在Windows10 64位及CAD2007中的完美适配

- 图解Win7搭建IIS7+PHP+MySQL+phpMyAdmin教程

- C#与LabVIEW联合采集NI设备的电压电流信号并创建Excel文件

- LP1800-3最小系统官方资料压缩包

- Linksys WUSB54GG无线网卡驱动程序下载指南