FPGA基的等精度频率计设计与Verilog实现

需积分: 10 134 浏览量

更新于2024-07-30

收藏 2.06MB DOC 举报

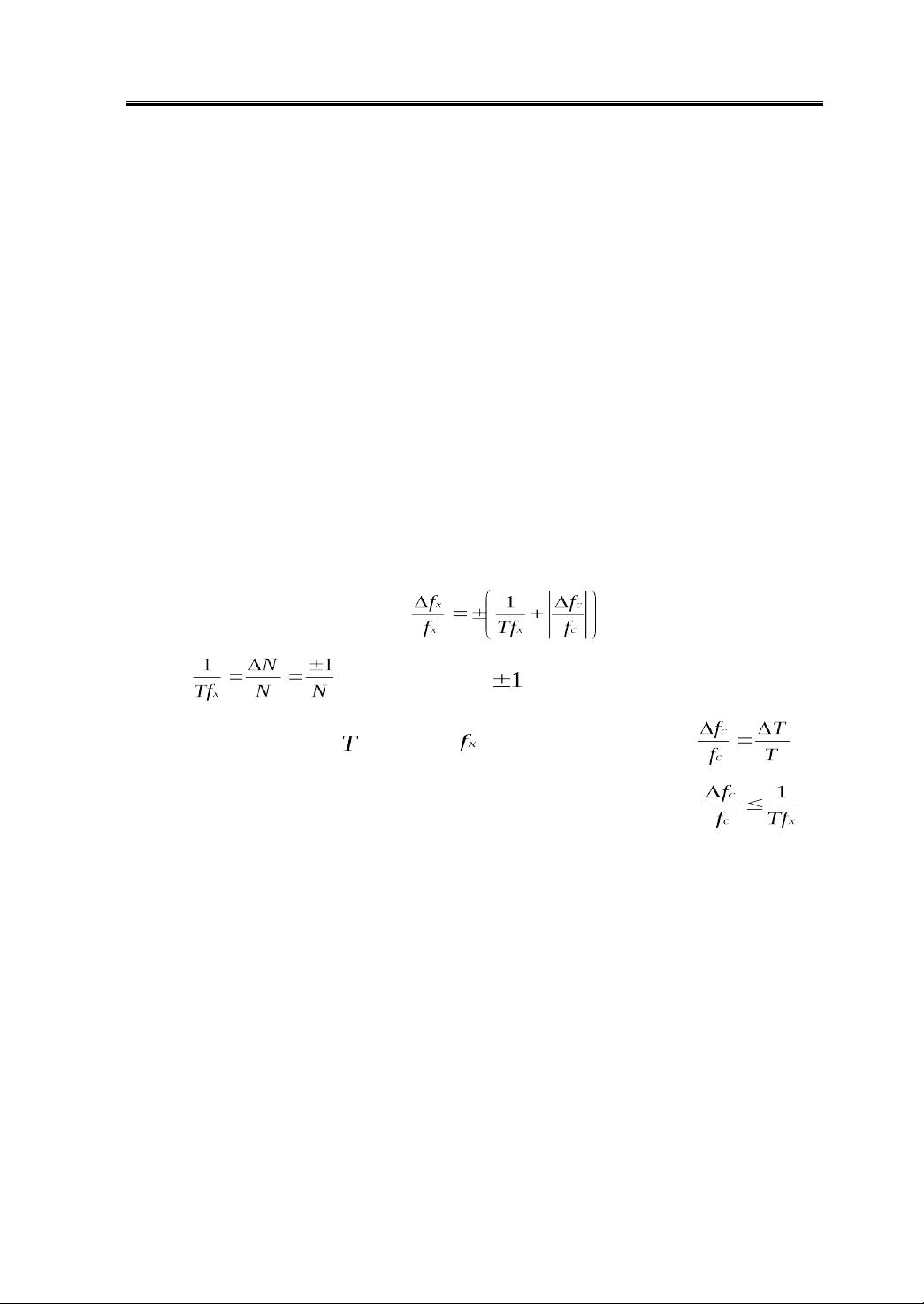

本文主要探讨了一种基于FPGA(Field-Programmable Gate Array)的等精度频率计的设计方案。首先,作者介绍了等精度测量的基本原理,即通过多个周期同步的方式,精确地捕捉输入信号的频率,这种方法相较于传统的测量方法具有更高的精度和周期性优势。等精度测量确保在不同频率下,计数误差保持在一个相对固定的范围内,这对于需要高稳定性的应用场景尤其重要。

设计的核心部分是利用FPGA中的Verilog HDL(Hardware Description Language)进行编程。Verilog被选择作为硬件描述语言,因为其灵活性和高度抽象能力,可以方便地设计和实现复杂的数字逻辑电路,包括计数器模块和除法器模块。这些模块的实现涉及到对时间延迟的精确控制,以保证频率测量的准确性。

文章在周立功公司的EasyFPGA030开发板上进行了实践,使用Libero 8.5集成开发环境进行软件开发和调试。通过Synplify工具进行逻辑综合,ModelSim进行仿真,确保设计的正确性和性能。然后,通过Designer工具进行硬件布局和布线,将设计下载至开发板进行实际测试。

为了实时显示测量结果,设计中还结合了AT89C51单片机,它负责数据处理和驱动共阳极LED数码管显示频率值。通过74LS244三态缓冲器和三极管放大电流,增强了LED的亮度,提高了可见度。此外,74LS14集成的施密特触发器反相器被用于信号整形,进一步优化了信号质量。

经过仿真下载验证,该设计成功实现了1Hz至1MHz范围内的等精度测频功能,充分证明了这种基于FPGA的解决方案在实际应用中的可行性和有效性。关键词包括等精度测量、频率测量、FPGA、Verilog HDL、Libero等,这些都是本文技术的核心要素。整个设计过程不仅展示了硬件设计与软件开发的紧密结合,也突出了现代电子设计中FPGA技术在提高测量精度和效率方面的优势。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-20 上传

2011-05-29 上传

2012-07-16 上传

2023-06-10 上传

2023-06-10 上传

phoenix890815

- 粉丝: 0

- 资源: 5

最新资源

- BeersManagment-AngularJS-Firebase:使用 AngularJS 和 Firebase 进行 CMS 管理 Beers,三种数据绑定方式

- Correlated

- Flat-Aar-Demo:测试Flat-Aar

- learn-rxjs-operators:Learn RxJS 中文版 (通过清晰的示例来学习 RxJS 5 操作符)

- Excel模板财 务 往 来 对 账 单.zip

- 【地产资料】XX地产 巡区工作表.zip

- flexcpp-old:用于C ++的词法扫描仪生成器

- dataSets

- 佑鸣最新暴雨强度公式 Ver2.08.zip

- Fetching-Data-Group-Project

- JoKenPo:操作系统课程1关于线程

- 香蕉:演示python程序

- Excel模板学生成绩统计表.zip

- 毕业设计&课设--毕业设计选题管理系统.zip

- sqlalchemy-challenge

- Express-file-upload-download:文件上传下载