没有合适的资源?快使用搜索试试~ 我知道了~

首页Altera的TimeQuest时序分析器

TimeQuest 时序分析器是 一种 ASIC 功能时序分析器,支持业界标准 Synopsys 设计约束 (SDC) 格式。TimeQuest 分析器支持收集应用程序接口 (API) ,可以直接访问设计中的端口、引脚、单元或者节点。您可以利用 TimeQuest 分析器中指定的任何有效约束或者工具命令语言 (Tcl) 命令来使用收集 API 。

资源详情

资源评论

资源推荐

© March 2009 Altera Corporation Quartus II Handbook Version 9.0 Volume 3: Verification

7. The Quartus II TimeQuest

Timing Analyzer

Introduction

The Quartus

®

II TimeQuest Timing Analyzer is a powerful ASIC-style timing analysis

tool that validates the timing performance of all logic in your design using an

industry-standard constraint, analysis, and reporting methodology. Use the

Quartus II TimeQuest Timing Analyzer’s GUI or command-line interface to constrain,

analyze, and report results for all timing paths in your design.

Before running the Quartus II TimeQuest Timing Analyzer, you must specify initial

timing constraints that describe the clock characteristics, timing exceptions, and signal

transition arrival and required times. You can specify timing constraints in the

Synopsys Design Constraints (.sdc) file format using the GUI or command-line

interface. The Quartus II Fitter optimizes the placement of logic to meet your

constraints.

During timing analysis, the Quartus II TimeQuest Timing Analyzer analyzes the

timing paths in the design, calculates the propagation delay along each path, checks

for timing constraint violations, and reports timing results as slack in the Report pane

and in the Console pane. If the Quartus II TimeQuest Timing Analyzer reports any

timing violations, you can customize the reporting to view precise timing information

about specific paths, and then constrain those paths to correct the violations. When

your design is free of timing violations, you can be confident that the logic will

operate as intended in the target device.

The Quartus II TimeQuest Timing Analyzer is a complete static timing analysis tool

that you can use as a sign-off tool for Altera

®

FPGAs and HardCopy

®

ASICs.

This chapter contains the following sections:

■ “Getting Started with the Quartus II TimeQuest Timing Analyzer” on page 7–2

■ “Compilation Flow with the Quartus II TimeQuest Timing Analyzer Guidelines”

on page 7–2

■ “Timing Analysis Overview” on page 7–6

■ “The Quartus II TimeQuest Timing Analyzer Flow Guidelines” on page 7–19

■ “Collections” on page 7–21

■ “SDC Constraint Files” on page 7–22

■ “Clock Specification” on page 7–24

■ “I/O Specifications” on page 7–39

■ “Timing Exceptions” on page 7–44

■ “Constraint and Exception Removal” on page 7–51

■ “Timing Reports” on page 7–51

■ “Timing Analysis Features” on page 7–74

■ “The TimeQuest Timing Analyzer GUI” on page 7–79

QII53018-9.0.0

7–2 Chapter 7: The Quartus II TimeQuest Timing Analyzer

Getting Started with the Quartus II TimeQuest Timing Analyzer

Quartus II Handbook Version 9.0 Volume 3: Verification © March 2009 Altera Corporation

■ “Conclusion” on page 7–89

f For more information about the TimeQuest Timing Analyzer and the SOPC Builder,

refer to Volume 4: SOPC Builder in the Quartus II Handbook.

Getting Started with the Quartus II TimeQuest Timing Analyzer

The Quartus II TimeQuest Timing Analyzer caters to the needs of the most basic to the

most advanced designs for FPGAs.

This section provides a brief overview of the Quartus II TimeQuest Timing Analyzer,

including the necessary steps to properly constrain a design, perform a full

place-and-route, and perform reporting on the design.

Setting Up the Quartus II TimeQuest Timing Analyzer

The Quartus II software version 7.2 and later supports two native timing analysis

tools: Quartus II TimeQuest Timing Analyzer and Quartus II Classic Timing Analyzer.

When you specify the Quartus II TimeQuest Timing Analyzer as the default timing

analysis tool, the Quartus II TimeQuest Timing Analyzer guides the Fitter and

analyzes timing results after compilation.

To specify the Quartus II TimeQuest Timing Analyzer as the default timing analyzer,

on the Assignments menu, click Settings. In the Settings dialog box, in the Category

list, select Timing Analysis Settings and turn on Use TimeQuest Timing Analyzer

during compilation.

To add the TimeQuest icon to the Quartus II toolbar, on the Tools menu, click

Customize. In the Customize dialog box, click the Toolbars tab, turn on Processing,

and click Close.

Compilation Flow with the Quartus II TimeQuest Timing Analyzer

Guidelines

When you enable the Quartus II TimeQuest Timing Analyzer as the default timing

analyzer, everything from constraint validation to timing verification is performed by

the Quartus II TimeQuest Timing Analyzer. Figure 7–1 shows the recommended

design flow steps to maximize and leverage the benefits the Quartus II TimeQuest

Timing Analyzer. Details about each step are provided after the figure.

Chapter 7: The Quartus II TimeQuest Timing Analyzer 7–3

Compilation Flow with the Quartus II TimeQuest Timing Analyzer Guidelines

© March 2009 Altera Corporation Quartus II Handbook Version 9.0 Volume 3: Verification

■ Create Quartus II Project and Specify Design Files—Creates a project before you

can compile design files. In this step you specify the target FPGA, any EDA tools

used in the design cycle, and all design files.

You can also modify existing design files for design optimization and add

additional design files. For example, you can add HDL files or schematics to the

project.

■ Perform Initial Compilation—Creates an initial design database before you

specify timing constraints for your design. Perform Analysis and Synthesis to

create a post-map database, or perform a full compilation to create a post-fit

database.

Creating a post-map database for the initial compilation is faster than creating a

post-fit database. A post-map database is sufficient for the initial database.

Creating a post-fit database is recommended only if you previously created and

specified an .sdc file for the project. A post-map database is sufficient for the initial

compilation.

■ Specify Timing Requirements—Timing requirements guide the Fitter as it places

and routes your design.

You must enter all timing constraints and exceptions in an .sdc file. This file must

be included as part of the project. To add this file to your project, on the Project

menu, click Add/Remove Files in Project and add the .sdc file in the Files dialog

box.

■ Perform Compilation—Synthesizes, places, and routes your design into the target

FPGA.

When compilation is complete, the TimeQuest Timing Analyzer generates

summary clock setup and clock hold, recovery, and removal reports for all defined

clocks in the design.

Figure 7–1. Design Flow with the Quartus II TimeQuest Timing Analyzer

Create Quartus II Project

and Specify Design Files

Perform Initial Compilation

Specify Timing Requirements

Perform Compilation

Verify Timing

7–4 Chapter 7: The Quartus II TimeQuest Timing Analyzer

Running the Quartus II TimeQuest Timing Analyzer

Quartus II Handbook Version 9.0 Volume 3: Verification © March 2009 Altera Corporation

■ Verify Timing—Verifies timing in your design with the Quartus II TimeQuest

Timing Analyzer. Refer to “The Quartus II TimeQuest Timing Analyzer Flow

Guidelines” on page 7–19.

Running the Quartus II TimeQuest Timing Analyzer

You can run the Quartus II TimeQuest Timing Analyzer in one of the following

modes:

■ Directly from the Quartus II software

■ Stand-alone mode

■ Command-line mode

This section describes each of the modes, and the behavior of the Quartus II

TimeQuest Timing Analyzer.

Directly from the Quartus II Software

To run the Quartus II TimeQuest Timing Analyzer from the Quartus II software, on

the Tools menu, click TimeQuest Timing Analyzer. The Quartus II TimeQuest Timing

Analyzer is available after you have created a database for the current project. The

database can be either a post-map or post-fit database; perform

Analysis and Synthesis to create a post-map database, or a full compilation to create a

post-fit database.

1 After a database is created, you can create a timing netlist based on that database. If

you create a post-map database, you cannot create a post-fit timing netlist in the

Quartus II TimeQuest Timing Analyzer.

When you launch the TimeQuest Timing Analyzer directly from the Quartus II

software, the current project opens by default.

Stand-Alone Mode

To run the Quartus II TimeQuest Timing Analyzer in stand-alone mode, type the

following command at the command prompt:

quartus_staw r

In stand-alone mode, you can perform static analysis on any project that contains

either a post-map or post-fit database. To open a project, double-click Open Project in

the Tasks pane.

Command-Line Mode

Use command-line mode for easy integration with scripted design flows. Using the

command-line mode avoids interaction with the user interface provided by the

Quartus II TimeQuest Timing Analyzer, but allows the automation of each step of the

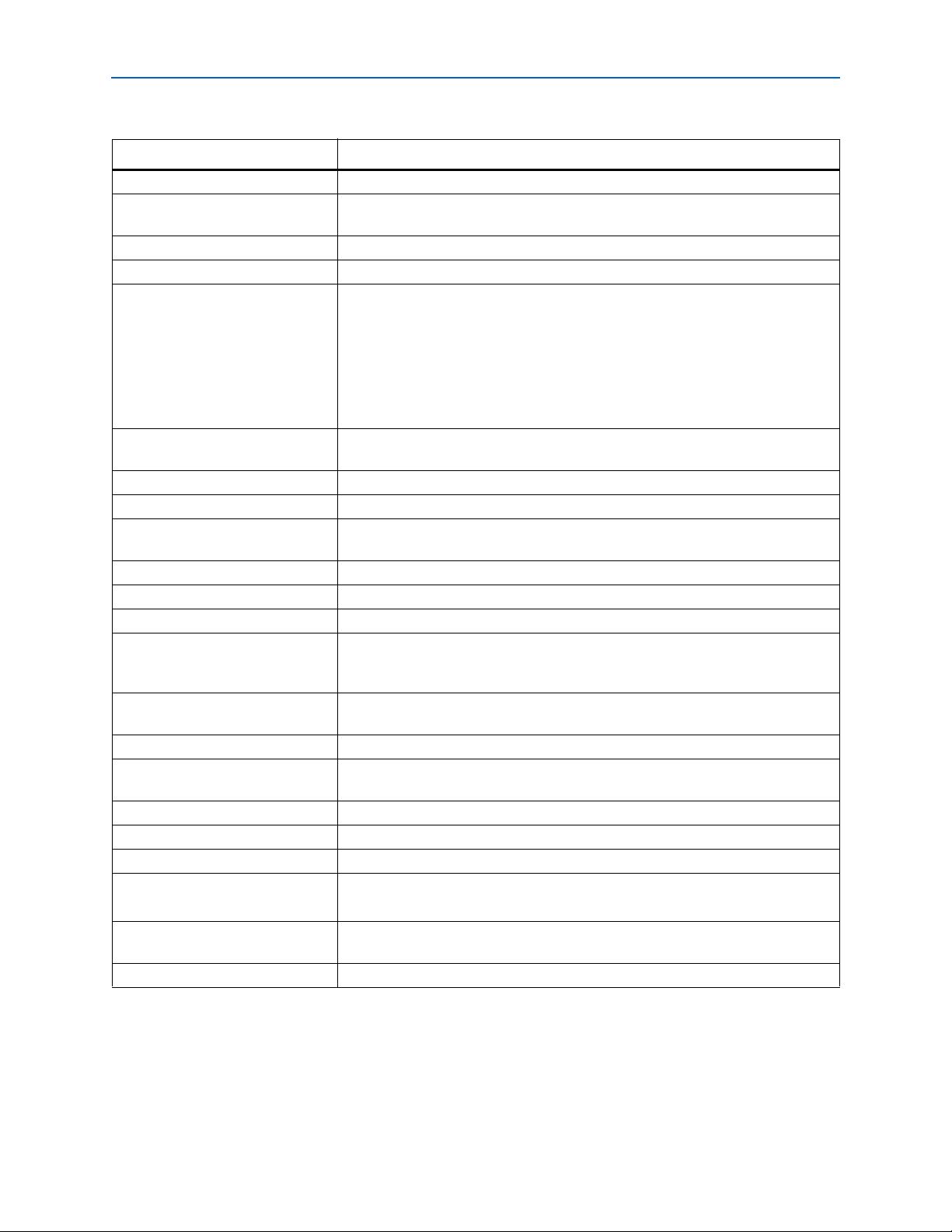

static timing analysis flow. Table 7–1 provides a summary of the options available in

the command-line mode.

Chapter 7: The Quartus II TimeQuest Timing Analyzer 7–5

Running the Quartus II TimeQuest Timing Analyzer

© March 2009 Altera Corporation Quartus II Handbook Version 9.0 Volume 3: Verification

To run the Quartus II TimeQuest Timing Analyzer in command-line mode, type the

following command at the command prompt:

quartus_sta <options> r

Table 7–1. Summary of Command Line Options

Command Line Option Description

-h | --help Provides help information on quartus_sta.

-t <script file> |

--script=<script file>

Sources the <script file>.

-s | --shell Enters shell mode.

--tcl_eval <tcl command> Evaluates the Tcl command <tcl command>.

--do_report_timing For all clocks in the design, run the following commands:

report_timing -npaths 1 -to_clock $clock

report_timing -setup -npaths 1 -to_clock $clock

report_timing -hold -npaths 1 -to_clock $clock

report_timing -recovery -npaths 1 -to_clock $clock

report_timing -removal -npaths 1 -to_clock $clock

--force_dat Forces the Delay Annotator to annotate the new delays from the recently compiled

design to the compiler database.

--lower_priority Lowers the computing priority of the quartus_sta process.

--post_map Uses the post-map database results.

--qsf2sdc Converts assignments from the Quartus II Settings File (.qsf) format to the

Synopsys Design Constraints File format.

--sdc=<SDC file> Specifies the .sdc file to read.

--report_script=<script> Specifies a custom report script to be called.

--speed=<value> Specifies the device speed grade to be used for timing analysis.

--tq2hc Generate temporary files to convert the Quartus II TimeQuest Timing Analyzer .sdc

file(s) to a PrimeTime .sdc file that can be used by the HardCopy Design Center

(HCDC).

--tq2pt Generates temporary files to convert the Quartus II TimeQuest Timing Analyzer .sdc

file(s) to a PrimeTime .sdc file.

-f <argument file> Specifies a file containing additional command-line arguments.

-c <revision name> |

--rev=<revision_name>

Specifies which revision and its associated Quartus II Settings File (.qsf) to use.

--multicorner Specifies that all slack summary reports be generated for both slow and fast corners.

--multicorner[=on|off] Turns off the multicorner analysis by using the off value.

--voltage=<value_in_mV> Specifies the device voltage (mV) to be used in timing analysis.

--temperature=

<value_in_C>

Specifies the device temperature (C) to be used in timing analysis.

--parallel

[=<num_processors>]

Specifies the number of computer processors to use on a multi-processor system.

--64bit E

nables 64-bit version of the executable.

剩余91页未读,继续阅读

whj5878088

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1