FPGA实现PS/2接口键盘识别电路设计

需积分: 10 94 浏览量

更新于2024-07-31

2

收藏 1.28MB DOC 举报

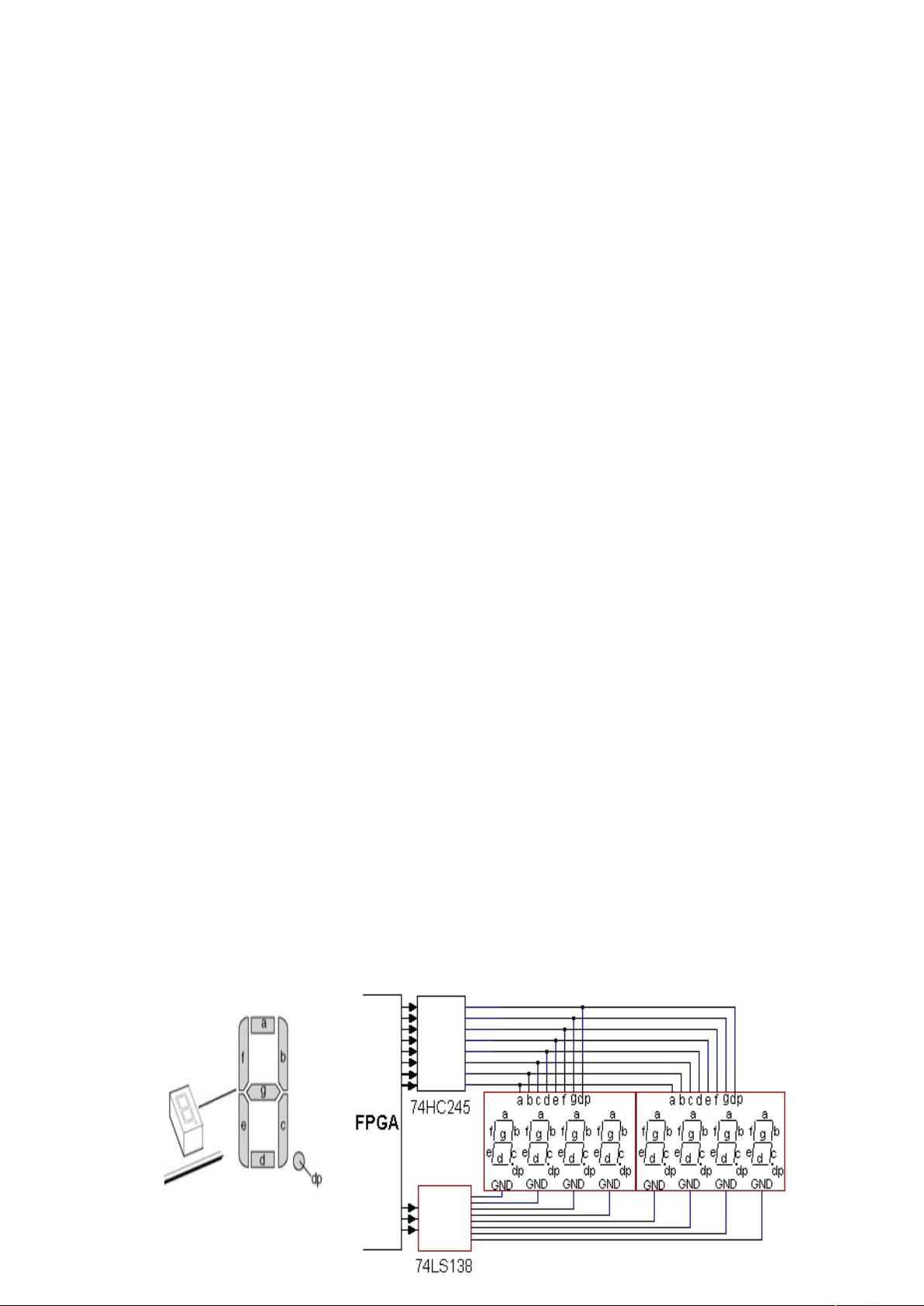

"这篇资源主要涉及的是如何使用FPGA进行PS2接口的Verilog编程,目的是设计一个能识别PS2键盘输入编码并显示在数码管上的电路,特别要求至少能识别0~9的数字键。设计中采用了模块化的思想,以键盘扫描输出端作为数据总线,各模块共享一个系统时钟。"

在基于FPGA的PS2接口编程中,重点在于理解和实现PS2通信协议。PS2接口是一种双向同步串行通信协议,它的通信依赖于CLOCK(时钟信号)和DATA(数据端口)两个传输端口。通信双方通过CLOCK同步,通过DATA交换数据。当CLOCK被拉低时,意味着通信被抑制。

在数据格式方面,PS2通信的数据帧包括1个起始位(始终为0)、8个数据位(低位在前)、1个奇偶校验位(执行奇校验)、1个停止位(始终为1)以及1个应答位(仅用于主机对设备的通讯)。奇偶校验位的设置确保数据位中的1的总数加上校验位的1始终为奇数。

在硬件实现上,PS2设备的clock和data线都是集电极开路,通常处于高电平状态。当设备准备发送数据时,会检查clock是否为高,如果是,就开始按照帧格式发送数据。数据在clock的上升沿准备好,下降沿被主机读取。PS2设备一般负责产生时钟信号,而主机可以通过拉低时钟线来控制通信,例如发送控制指令。

在Verilog编程中,你需要定义相应的模块来模拟这些行为。可能的模块包括PS2接口模块、数据解析模块、数码管显示驱动模块等。PS2接口模块将处理时钟和数据线的状态,接收和发送数据帧;数据解析模块则会解码接收到的数据,判断是否为0~9的数字键;数码管显示驱动模块根据解析的结果控制数码管的显示。

这个项目涵盖了FPGA基础、Verilog语言、串行通信协议、数字逻辑设计等多个方面的知识,对于提升数字系统设计和硬件描述语言编程能力有着显著的实践价值。在设计过程中,需要考虑时序逻辑、同步异步问题、错误检测和处理机制,以及如何将这些模块有效地集成到一个完整的FPGA设计中。

2013-04-21 上传

2023-08-21 上传

2023-06-02 上传

2023-09-01 上传

2023-05-27 上传

2023-08-08 上传

2023-11-16 上传

zhangdanzhengjun

- 粉丝: 0

- 资源: 1

最新资源

- 解决Eclipse配置与导入Java工程常见问题

- 真空发生器:工作原理与抽吸性能分析

- 爱立信RBS6201开站流程详解

- 电脑开机声音解析:故障诊断指南

- JAVA实现贪吃蛇游戏

- 模糊神经网络实现与自学习能力探索

- PID型模糊神经网络控制器设计与学习算法

- 模糊神经网络在自适应PID控制器中的应用

- C++实现的学生成绩管理系统设计

- 802.1D STP 实现与优化:二层交换机中的生成树协议

- 解决Windows无法完成SD卡格式化的九种方法

- 软件测试方法:Beta与Alpha测试详解

- 软件测试周期详解:从需求分析到维护测试

- CMMI模型详解:软件企业能力提升的关键

- 移动Web开发框架选择:jQueryMobile、jQTouch、SenchaTouch对比

- Java程序设计试题与复习指南