Pulsonix高速布线教程:差分对设置与操作

需积分: 10 186 浏览量

更新于2024-09-12

收藏 340KB DOC 举报

"pulsonix高速布线--差分对"

在电子设计自动化(EDA)领域,Pulsonix是一款强大的PCB设计软件,它提供了高级的高速布线功能,其中包括对差分对的精确控制。差分对是高速数字电路设计中的一种重要信号传输方式,能有效减少电磁干扰(EMI),提高信号完整性和传输速度。

在Pulsonix中配置差分对的步骤如下:

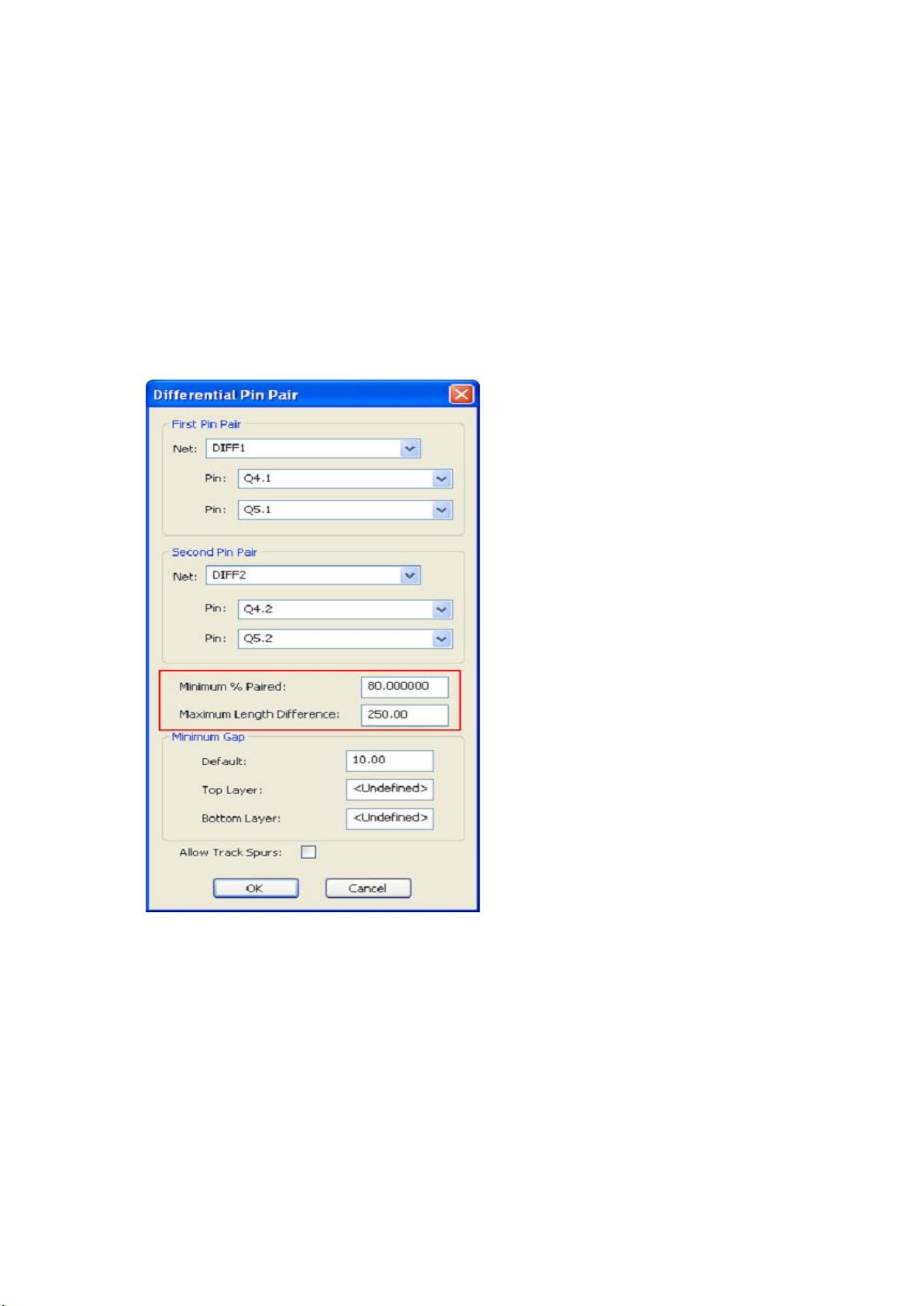

1. 配置差分对规则:首先,你需要通过点击菜单`Setup -> Technology`,打开技术配置对话框。在列表中选择`Rules - DifferentialPairs`来编辑或新建差分对设置。在这里,你可以定义差分线的网络名、起点和终点,例如`DIFF1`、`Q4.1`、`Q5.1`等,并设置最小成对百分比(Minimum%Paired)和最大长度差异(MaximumLengthDifference)等参数,以确保两条差分线的匹配性。

2. 差分对间距设定:默认的差分对最小间距可以在`MinimumGap`中调整。同时,你还可以为顶层(TopLayer)和底层(BottomLayer)设定不同的最小间距,但都需大于默认值。

3. 应用差分对规则:在`Nets-NetClass`列表中,创建并选中你所定义的差分对规则,这样系统就会按照这些规则进行布线。

4. 绘制差分对:从第一条差分线的起点开始绘制,确保与元件的管脚(Pin)相连,而不是过孔(Via)。绘制完成后,通过45度角转折,然后右键选择`StartMirroring Paired Tracks`开始镜像配对轨道,完成差分对的绘制。

5. 过孔配置:如果需要差分对换层,可以通过右键选择`ViaPattern`来配置过孔参数,并按照指示图放置过孔。

6. 移除差分对特性:如果需要取消差分对特性,可以选择对应的差分线,右键点击`RemoveDifferentialPairing`。若要删除走线,直接按`Delete`键。

7. 设计检查:Pulsonix允许用户进行设计规则检查(DRC)。在`Tools -> Design Rule Checking`中启用`Nets`选项,可检查差分对是否满足预设的布线规则。

差分对设计的严谨性对于高速电路的性能至关重要。通过Pulsonix的这些高级功能,设计师能够精确控制差分对的布局和布线,从而实现更高效、更可靠的电路设计。理解并熟练掌握这些操作,将有助于优化电子产品的性能和稳定性。

2013-01-09 上传

2013-01-09 上传

2010-05-21 上传

2020-08-12 上传

2021-03-30 上传

点击了解资源详情

2024-10-30 上传

点点吃得太多了

- 粉丝: 180

- 资源: 683

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章