"Vivado约束脚本使用技巧大全"

需积分: 5 41 浏览量

更新于2024-01-08

6

收藏 1.77MB DOCX 举报

Vivado中约束脚本是在FPGA设计中非常重要的一部分,它用于指定FPGA中各个元件(如管脚、时钟等)的特性和连接方式,从而确保设计在FPGA中正确实现。本文将汇总Vivado中常用的约束脚本及用法,包括管脚约束、IOB约束、时钟约束、延迟约束、布局约束、综合导出导入等,以便对这些功能有一个全面的了解和掌握。

1. 管脚约束约束脚本及用法

在Vivado中,管脚约束主要用于指定FPGA芯片上与外部环境相连的引脚的相关信息,包括引脚位置、引脚电平标准等。通过set_property命令可以对管脚进行设置,例如:

```sh

set_property PACKAGE_PIN V4 [get_ports{clk}] //clk 管脚绑定

set_property IOSTANDARD LVCMOS33 [get_ports{clk}] //clk 管脚电平

```

此外,在Vivado中,一些IP核已经包含了模块的引脚配置,因此在约束文件中就不必重复设置相应约束。但在生成位流时可能会出现错误,解决方法是在.XDC文件中加入相应的约束设置。

2. IOB 约束脚本及用法

IOB(Input Output Buffer)约束是用于对FPGA输入输出缓冲器的设置,通过约束可以指定数据输入输出的时序要求,以及缓冲器的相关属性。

3. 时钟约束脚本及用法

时钟约束脚本是对时钟控制器的设置约束,其中包括时钟频率、时钟启动等。对于FPGA设计来说,时钟约束是至关重要的,对于时序同步和数据稳定性非常重要。

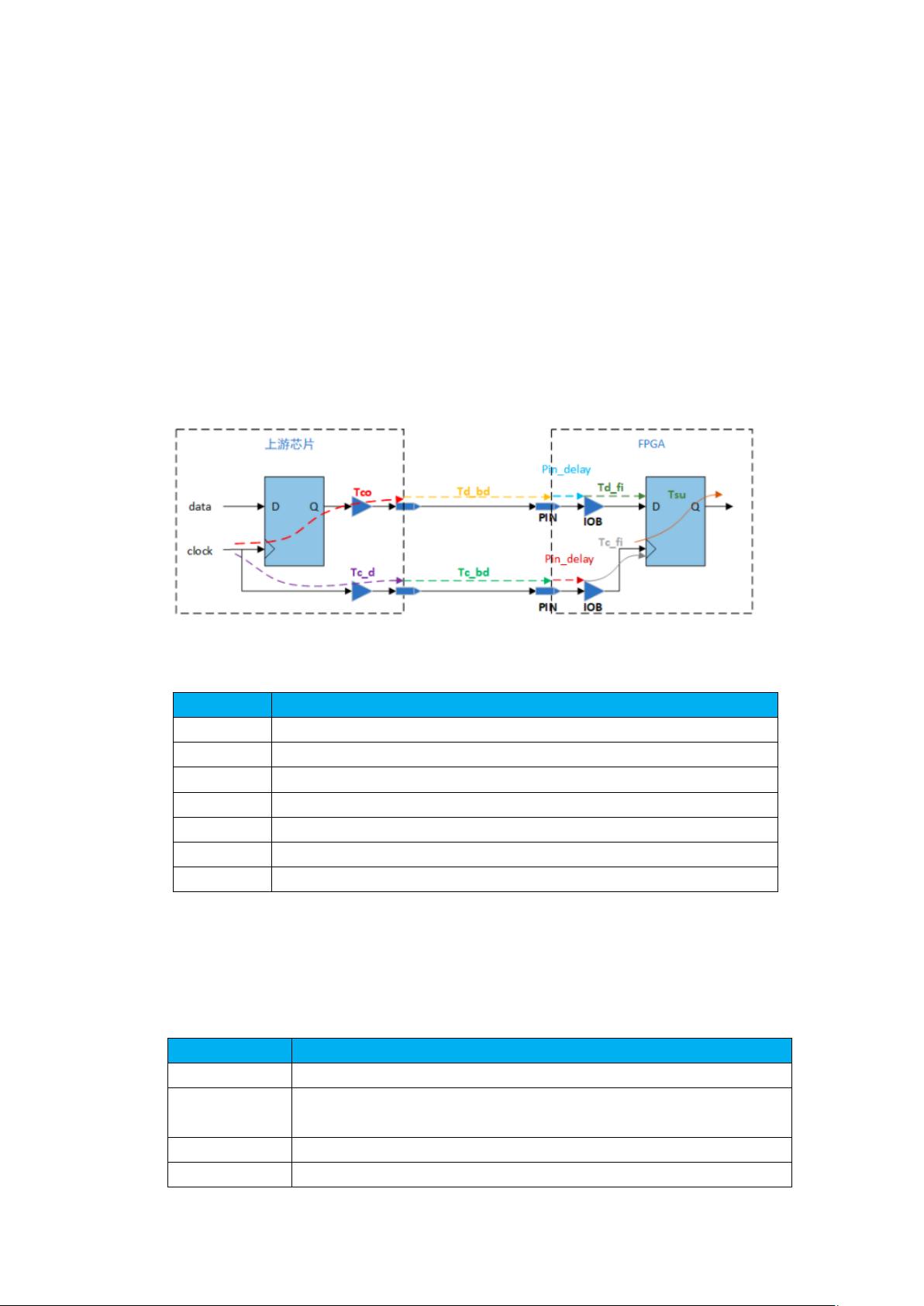

4. set_input_delay 和 set_output_delay 约束脚本及用法

set_input_delay和set_output_delay约束用于指定输入输出的最大延迟要求,确保输入输出数据的时序正确性。

5. set_clock_groups 约束脚本及用法

set_clock_groups约束用于指定时钟之间的关系,例如时钟同步或异步等。

6. set_false_path 脚本及用法

set_false_path约束用于指定某些路径不需要进行时序优化,适用于一些不重要的时序路径。

7. set_multicycle_path 脚本及用法

set_multicycle_path约束用于指示某些路径允许多个时钟周期内完成,适用于一些对时序要求不严格的路径。

8. 布局约束 BEL 脚本及用法

布局约束用于指定FPGA中各个逻辑元件的位置,包括对BEL资源的约束设置。

9. 布线约束脚本及用法

布线约束用于指定FPGA中逻辑元件之间的连接关系和布线优化设置。

10. 布局约束用法

布局约束的设置方法和语法。

11. 配置约束用法

对FPGA配置过程中的相关约束设置方法和用法。

12. set_max_delay、set_min_delay(最大、最小延迟约束)

设置输入输出的最大和最小延迟约束。

13. 综合导出、导入网表文件方法

将设计综合之后的网表文件导出,并在其他设计中导入网表文件的方法。

综上所述,Vivado中约束脚本的设置是FPGA设计中必不可少的一环,通过合理的约束设置可以确保设计在FPGA中正确实现,保证时序等重要性能要求。因此,设计工程师需要对各种约束的设置方法和用法有一个全面的了解和掌握,以确保设计的正确性和性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-06 上传

2023-05-12 上传

2023-06-06 上传

2023-09-13 上传

Vincent_limin

- 粉丝: 1

- 资源: 7

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程