飞思卡尔KL25中文技术手册:详解特性和开发指南

需积分: 15 114 浏览量

更新于2024-07-19

收藏 13.61MB PDF 举报

飞思卡尔KL25中文技术手册是一份全面介绍飞思卡尔公司KL25微控制器的专业文档,旨在为系统架构师和软件应用开发人员提供深入的技术细节。手册首先明确了文档的目的,即阐述KL25的特点、架构以及编程模板,确保用户对其功能和工作原理有清晰理解。

该手册针对的目标读者是那些在设计和开发过程中会使用到KL25的工程师,他们需要了解如何有效地利用这款微控制器的各种特性来构建低功耗且功能丰富的电子系统。手册中强调了数字系统的表示方法,包括二进制、十进制和十六进制的使用,以及印刷记号的定义,如占位符、斜体、代码和特殊寄存器的引用方式。

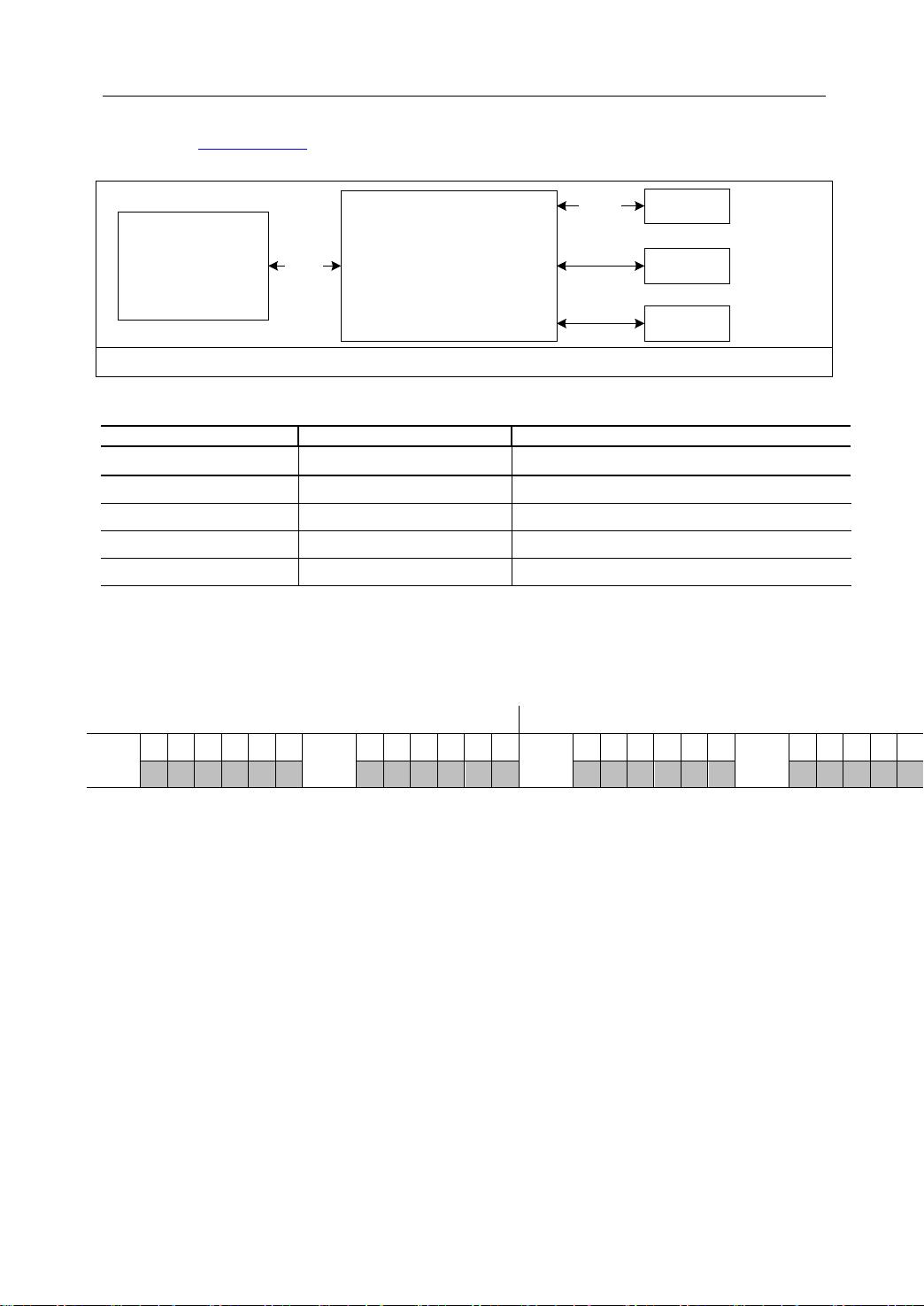

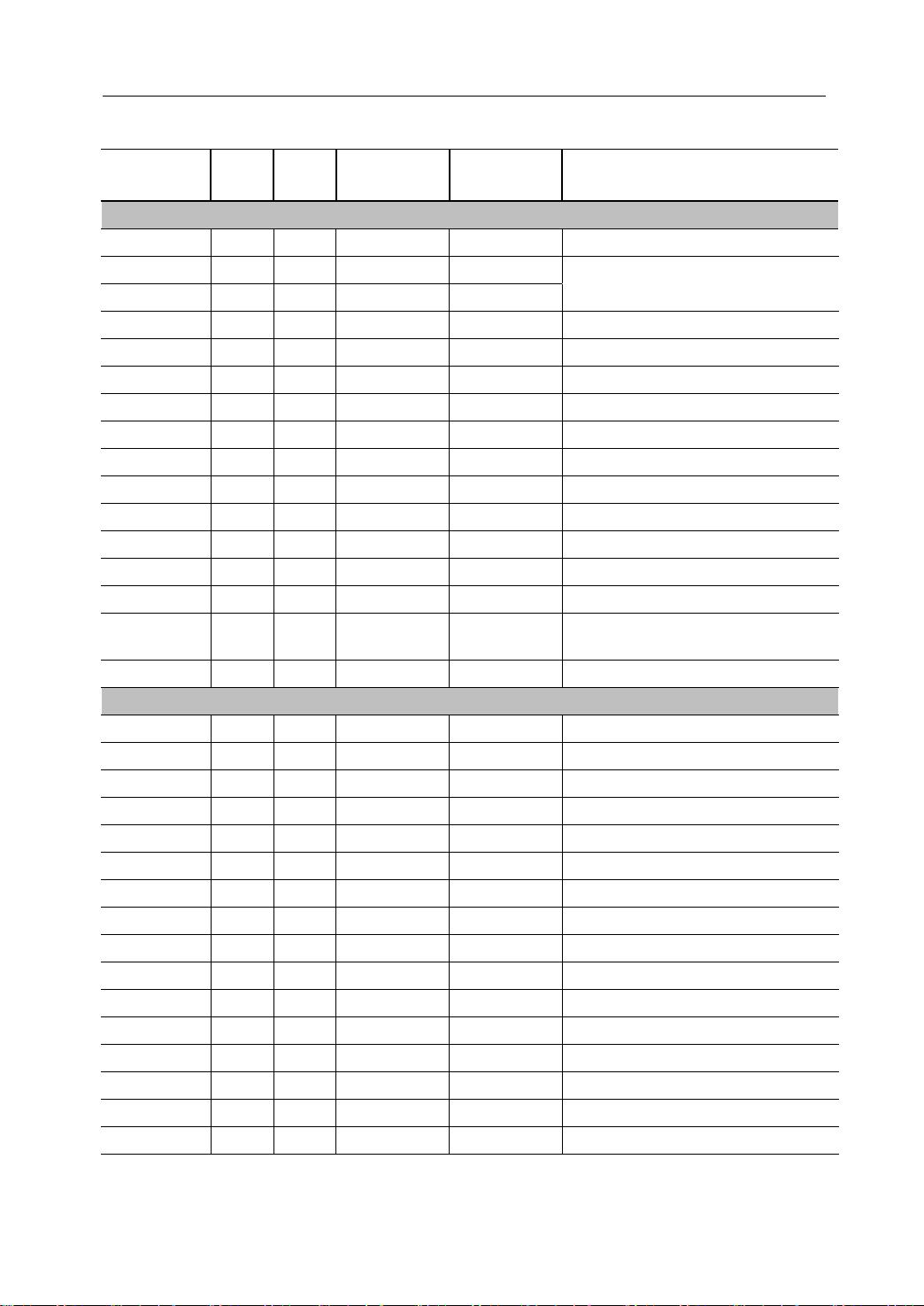

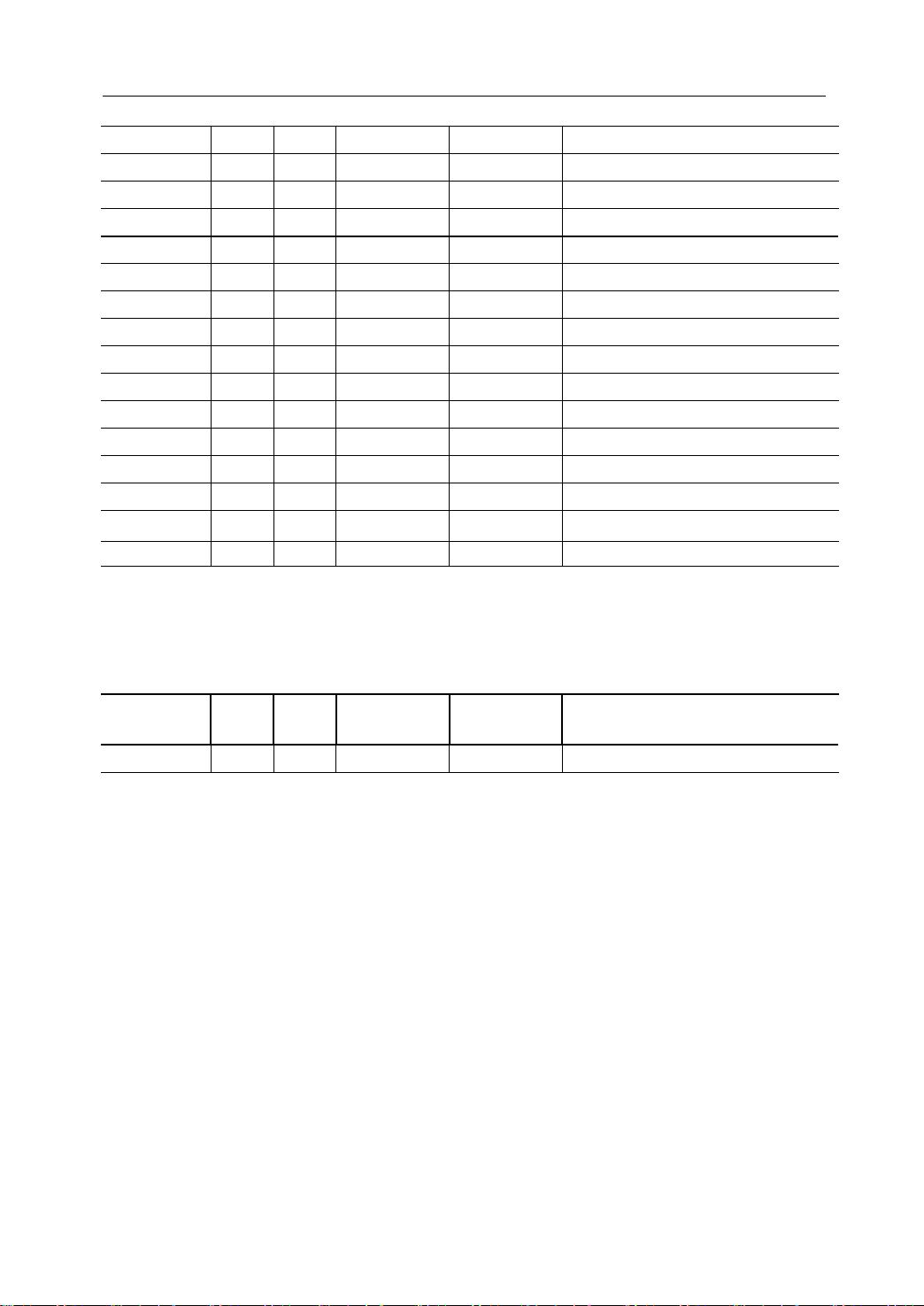

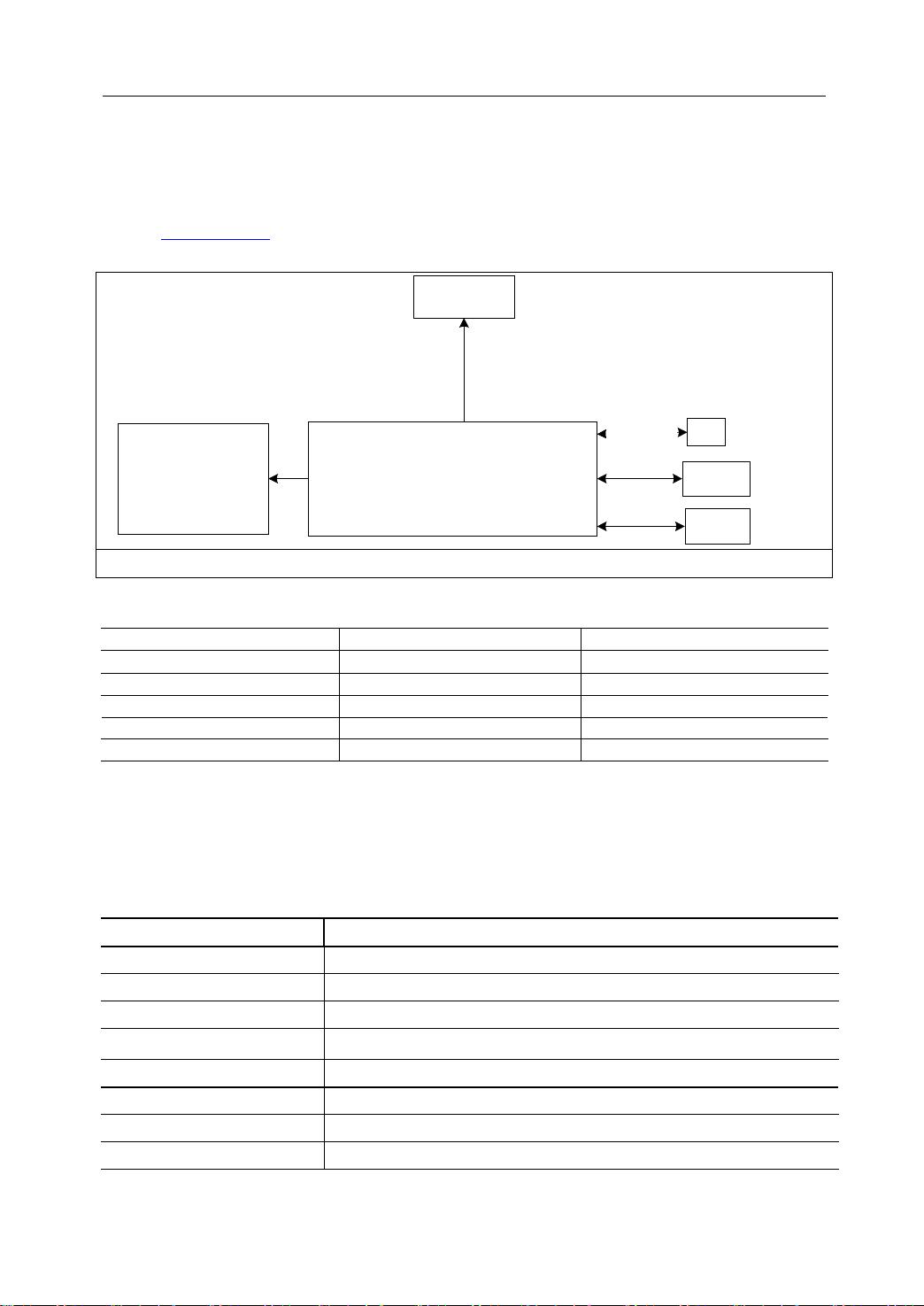

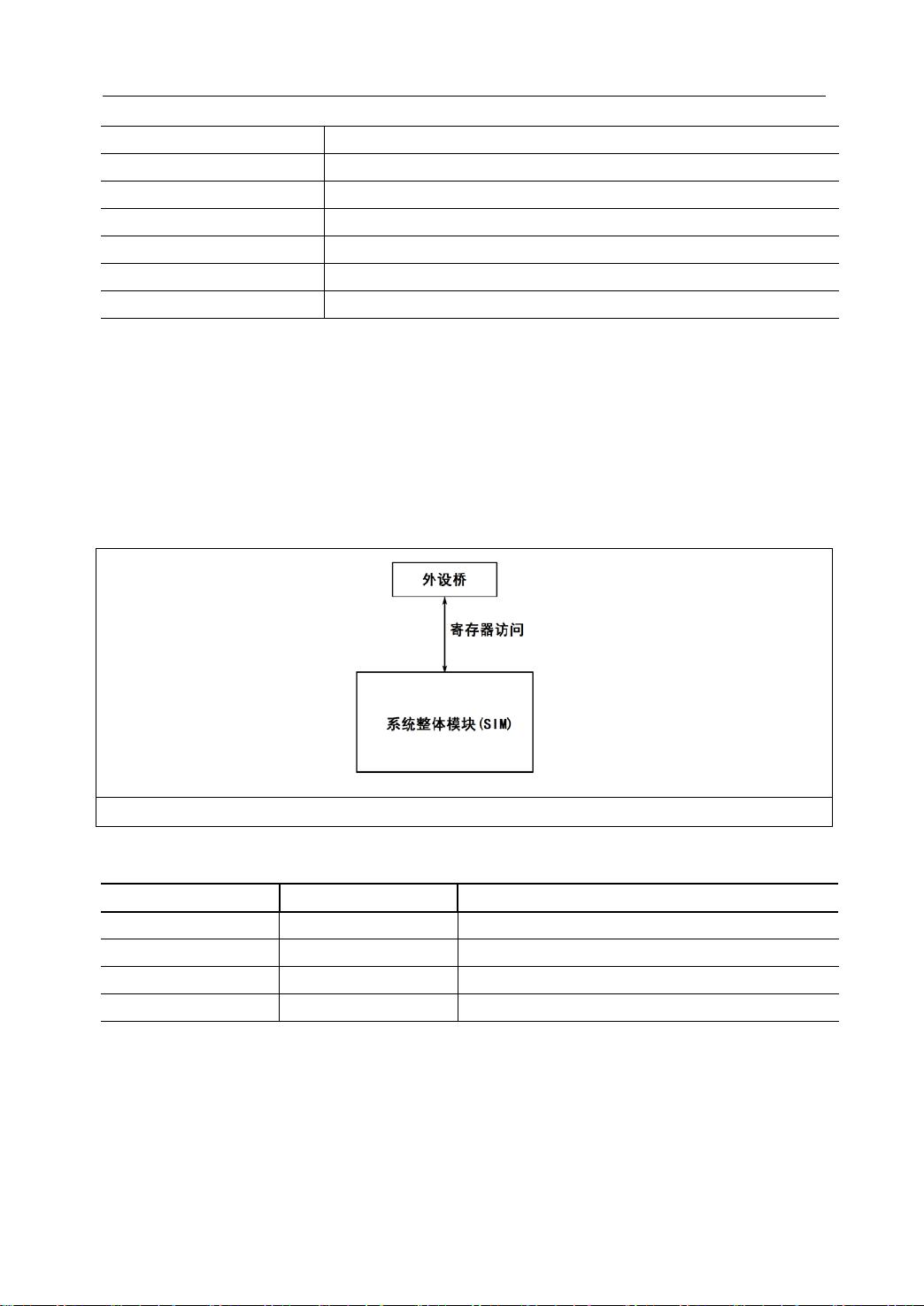

特殊术语部分解释了诸如“有效”和“无效”的概念,以及在电路设计中保留内存空间和寄存器的重要意义。这些概念对于正确理解和操作硬件至关重要。在引言部分,手册深入介绍了ARM Cortex-M0+的KinetisL系列MCU,特别是KL25系列,强调其低功耗和混合信号处理能力,以及系列内不同型号在存储器容量、接口数量和封装形式上的多样性。

第二章对KL25的详细特性和产品系列进行了概述,提供了准确的芯片描述,有助于开发人员根据具体需求选择合适的KL25型号。通过这份技术手册,用户能够掌握KL25的硬件配置、编程接口以及如何进行高效能的软件设计,从而在实际项目中充分发挥其性能优势。

飞思卡尔KL25中文技术手册是一部实用的参考工具,涵盖了从基础概念到具体操作的全方位指导,对于KL25的使用者来说是不可或缺的参考资料。

179 浏览量

184 浏览量

279 浏览量

点击了解资源详情

259 浏览量

174 浏览量

点击了解资源详情

qq_37108937

- 粉丝: 0

- 资源: 3

最新资源

- a-simple-mvc-rest-service:包含带有 TDD 的示例模块的简单 RESTJersey 项目,用 Java 实现

- weather_api

- BudgetTracker:无论有没有连接,用户都可以在其预算中添加费用和存款。 脱机输入交易时,当它们重新联机时应填充总数

- Google_intro:对于Dsl的布局,时间不够。

- dnvod-ad-killer:dnvod.tv的AD卸妆

- 信号与系统 实验作业

- NativeTop.NiceDream.ga4Usk4

- TouTiaoAd:react native头条广告穿山甲广告,腾讯广告优量汇广点通广告集成reactnative RN

- 5_网络字节序_werevj4_

- Angular中的广播消息

- s2c-restful-services:s2c 项目宁静服务 + 存储库

- Gitee上的开源ERP系统源码

- django-countries:一个Django应用程序,提供与表格一起使用的国家/地区选择,标记图标静态文件以及模型的国家/地区字段

- plotly-challenge

- typora笔记工具

- ant_plus_demo:用于测试 ant+ 的 Android 应用