CMOS ESD保护设计深度解读:原理应用与实际案例分析

发布时间: 2024-12-21 13:55:02 阅读量: 9 订阅数: 16

CMOS电路中ESD保护结构的设计原理与要求

# 摘要

本文全面探讨了CMOS技术中ESD保护设计的基础知识、理论、技术应用以及面对的挑战和发展趋势。首先,介绍了ESD保护设计的重要性及其理论基础,包括ESD现象的产生、危害及保护的必要性。其次,分析了ESD保护器件的工作原理,讨论了设计原则,并通过具体案例提供实践指导。第三章详述了ESD保护在CMOS电路中的实际应用和测试验证方法,分析了产业界的设计案例和技术难题。第四章探讨了实践中的设计策略和高性能技术的探索,以及案例分析中创新设计的实际影响。最后一章展望了CMOS ESD保护技术的未来,讨论了新材料和新技术对集成电路ESD保护的影响,行业标准的演变,并强调了持续学习与专业发展的重要性。本文为CMOS ESD保护设计提供了深入的理论支持和实践指导,对相关领域的研究和技术进步具有重要参考价值。

# 关键字

CMOS技术;ESD保护;设计原则;测试与验证;实践策略;技术挑战;发展趋势

参考资源链接:[模拟CMOS集成电路设计(毕查德-拉扎维著)课后答案](https://wenku.csdn.net/doc/6412b467be7fbd1778d3f7bc?spm=1055.2635.3001.10343)

# 1. CMOS ESD保护设计基础

在高速发展的集成电路(IC)设计领域中,CMOS技术占据了举足轻重的地位。然而,随着器件特征尺寸的缩小和工作频率的提升,CMOS集成电路对外部静电放电(ESD)的脆弱性也日益显著。ESD现象不仅对电子设备的可靠性构成威胁,而且可能引起器件功能失效甚至物理损坏。

## 1.1 ESD现象的防护需求

静电放电是一个瞬态事件,通常涉及高电压和大电流,可以在没有适当防护的情况下,对CMOS电路造成严重破坏。因此,从设计阶段开始,就需要将ESD保护措施纳入考虑范围。ESD防护不仅是为了保证电子设备的正常工作,还是为了满足安全和质量标准,保障用户和设备的安全。

## 1.2 ESD保护策略

ESD保护策略通常从两个方面来考虑:预防和缓解。预防策略主要涉及到屏蔽和隔离技术,以减少静电放电事件的发生。而缓解策略则是通过在CMOS电路中集成ESD保护器件,来吸收和分散静电放电事件产生的能量,从而保护核心电路不受损害。下一章节将深入探讨ESD保护的理论与技术。

# 2. ESD保护理论与技术

### 2.1 ESD的基本原理

在电子设备的使用和操作过程中,静电放电(Electrostatic Discharge, ESD)是普遍存在的现象。由于静电放电瞬间会产生极高电流和电压,因此对电子设备尤其是敏感的微电子设备构成潜在危害。

#### 2.1.1 ESD现象的产生与危害

ESD现象通常发生在两个不同电位的物体接触或接近时。一个典型的例子是人体在干燥条件下行走,可能会积累数千伏特的静电,一旦接触电子设备的敏感部位,就会发生放电,导致设备损坏。ESD放电可以分为人体模型(Human Body Model, HBM)、机器模型(Machine Model, MM)和带电器件模型(Charged Device Model, CDM)等几种类型,每种类型都对电子设备有不同的危害影响。

静电放电造成的损害通常分为硬损伤和软损伤。硬损伤比较容易被检测,如电路烧毁等;软损伤则难以诊断,可能会引起设备参数漂移、数据错误等隐性问题。长期的软损伤累积会显著减少电子设备的寿命。

#### 2.1.2 ESD保护的必要性

由于ESD的普遍性和危害性,现代电子产品的设计中都必须考虑ESD保护。保护措施可以减少或避免由ESD带来的损害,保证电子设备的可靠性和使用寿命。ESD保护已经成为电子产品设计和质量检验中的重要一环。

### 2.2 ESD保护器件的工作原理

为了有效防护ESD,各种保护器件被发明并应用在电子设备中。它们根据不同的工作原理进行电流分流或钳位,以保护后续电路不受损坏。

#### 2.2.1 传统保护器件分析

传统ESD保护器件如瞬态抑制二极管、气体放电管等,它们依靠半导体材料的非线性特性来提供ESD保护。例如,瞬态抑制二极管在正常工作电压下不导通,而在ESD事件发生时,器件反向击穿,将高电压和电流引到地线,从而保护其他电路。

尽管传统保护器件简单可靠,但它们在响应时间、钳位电压和寄生电容等方面存在局限性,这在高速电路和精密电路设计中可能构成问题。

#### 2.2.2 新型保护器件介绍

随着微电子技术的发展,越来越多的新型ESD保护器件如场效应晶体管(FET)、硅可控整流器(SCR)、以及基于MEMS技术的保护器等被开发出来。这些新型器件在低钳位电压、高速响应和低电容等方面性能更加优异,为高速、高集成度的电路提供了更优的ESD保护方案。

新型器件通过特殊的结构和材料,能够有效降低器件的导通电阻,实现快速响应和较低的钳位电压,极大地提高了ESD保护的效果。

### 2.3 ESD保护电路设计原则

设计ESD保护电路时,需要考虑多个因素以保证电路的安全性和稳定性。

#### 2.3.1 设计要点与考量因素

ESD保护电路设计时首先需要确保足够的电流分流能力,其次应具有快速的响应时间以应对高速放电事件。同时,钳位电压要尽量低,以减少对后续电路的冲击。此外,保护电路本身不应引入过大的寄生电容,这在高速电路设计中尤为关键。

电路设计还需要考虑整体布局,包括ESD保护器件的放置位置以及信号路径的长度。保护器件应尽量靠近可能的ESD接触点,以缩短ESD电流流动的路径,减少干扰。

#### 2.3.2 典型设计案例分析

例如,一款高精度模拟信号处理器的设计需要考虑ESD保护。设计师会在信号输入端口并联一个瞬态抑制二极管,以确保在ESD事件发生时,保护器能快速导通并将高电压钳制在安全范围内。在更高级的设计中,可能还会结合使用气体放电管等器件,形成多级ESD保护网络。

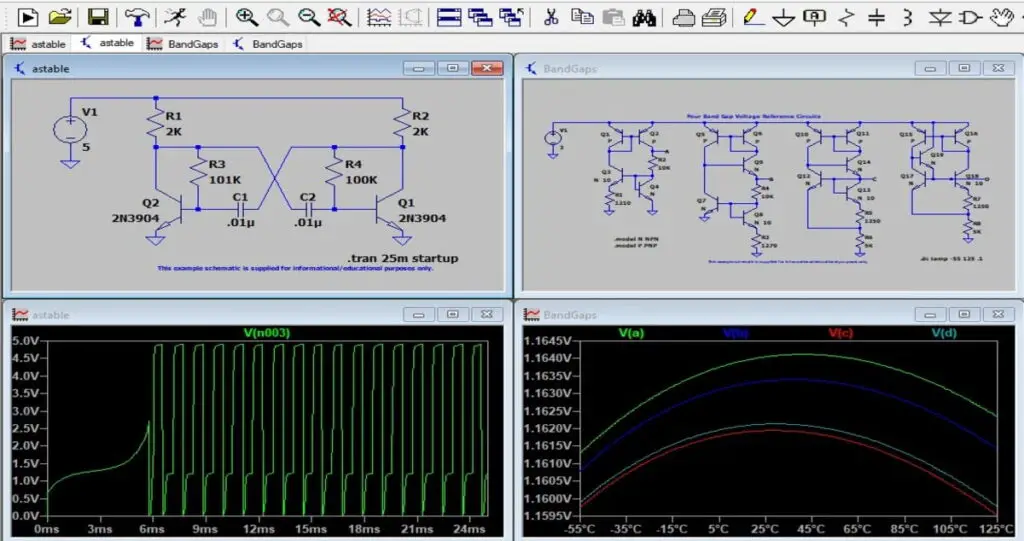

为了验证电路设计的有效性,设计师会进行模拟仿真和实际测试。模拟仿真可以通过电路设计软件进行,而实际测试则需要使用ESD枪等设备来模拟ESD事件,从而验证保护电路的响应速度和钳位效果。

ESD保护电路的设计不仅仅是一种技术手段,更是一种设计理念。在未来的设计中,我们需要不断探索新的保护器件和电路结构,以应对日益增长的电子设备性能需求。

由于篇幅限制,以上为第二章部分章节内容。实际文章应保证每个一级章节、二级章节及以下级别的内容均满足相应的字数要求,并包含规定的元素如代码块、表格、流程图等,以及展开对应的分析与讨论。

# 3. CMOS ESD保护技术的应用

ESD保护技术在CMOS电路中的应用是电子工程领域的一个重要课题。随着CMOS技术的不断进步和微型化,ESD保护变得更加复杂和关键。本章将深入探讨ESD保护在CMOS电路中的实现方法、ESD保护器件的测试与验证,以及实际案例研究。

## 3.1 ESD保护在CMOS电路中的实现

### 3.1.1 CMOS技术与ESD保护的结合点

随着半导体技术的发展,CMOS(互补金属氧化物半导体)工艺已成为现代集成电路设计的主流技术。CMOS工艺的一个显著特点是其低功耗特性,这使得它非常适合便携式电子设备,但同时也对ESD(静电放电)保护提出了更高要求。CMOS技术与ESD保护的结合点主要体现在以下几个方面:

- **集成度提高**:随着CMOS集成度的提高,晶体管

0

0