CMOS集成电路设计秘籍:从理论到实践,专家揭秘设计要点及故障预防

发布时间: 2024-12-21 12:39:53 阅读量: 8 订阅数: 15

艾伦CMOS模拟集成电路设计及课后答案

# 摘要

CMOS集成电路设计是微电子领域的重要技术之一,涉及从理论基础到实践应用的广泛知识。本文首先概述了CMOS集成电路的设计原理,包括MOSFET的工作原理、CMOS工艺技术及数字逻辑电路设计基础。接着,文章详细探讨了模拟和数字电路设计的关键要点,以及电路版图设计与验证的重要性。文章还着重于故障预防与诊断技术,介绍了故障类型、预防措施以及先进的测试和模拟技术。此外,针对高级设计技术,本文介绍了低功耗设计、高速电路设计以及可靠性设计与验证的相关策略。最后,文章展望了CMOS设计的行业标准、最佳实践及未来发展趋势,包括3D IC技术以及新材料和新工艺的应用前景。

# 关键字

CMOS集成电路;MOSFET;故障预防;版图设计;低功耗技术;可靠性设计

参考资源链接:[模拟CMOS集成电路设计(毕查德-拉扎维著)课后答案](https://wenku.csdn.net/doc/6412b467be7fbd1778d3f7bc?spm=1055.2635.3001.10343)

# 1. CMOS集成电路设计概述

## 1.1 集成电路设计的重要性

集成电路(IC)作为现代电子设备的基石,对性能、体积、功耗等关键参数有着决定性的影响。随着技术的进步,CMOS(互补金属氧化物半导体)技术凭借其低功耗和高集成度的优势,成为了主流的集成电路设计工艺。

## 1.2 CMOS集成电路的设计挑战

随着集成电路复杂性的增加,设计师面临诸如缩小尺寸、提高速度、降低功耗等挑战。CMOS设计不仅要考虑电路的电气性能,还要兼顾制造工艺、成本效益和环境适应性。

## 1.3 CMOS集成电路设计的发展

CMOS技术正在经历从平面晶体管到3D晶体管结构的转变,设计工具和方法也在不断更新以适应新的设计需求。本章节将为读者提供对CMOS集成电路设计全景的认识,并概述后续章节中将深入探讨的关键技术和最佳实践。

在本章中,我们将了解CMOS集成电路设计的重要性、面临的挑战以及其技术发展。这为理解后续章节中更详细的设计理论、工艺技术、电路设计实践和故障诊断技术打下了基础。

# 2. CMOS设计基础理论

在现代电子工程领域,CMOS集成电路设计是构建数字和模拟系统的关键技术之一。理解CMOS集成电路设计基础理论是开启成功设计大门的钥匙。本章节会深入探讨MOSFET工作原理、CMOS工艺技术和数字逻辑电路设计基础,这些内容对于想要掌握CMOS设计的工程师来说至关重要。

## 2.1 MOSFET工作原理

### 2.1.1 MOSFET的基本结构和特性

金属-氧化物-半导体场效应晶体管(MOSFET)是CMOS集成电路中的基本构建块。它是一种电压控制器件,使用电场来控制电流的流动。MOSFET有两大类:n型MOSFET(nMOS)和p型MOSFET(pMOS),它们的主要区别在于掺杂类型和载流子类型。

MOSFET由四个主要部分组成:源极(Source)、漏极(Drain)、栅极(Gate)和体极(Body或Bulk)。栅极上方的绝缘层由氧化物构成,这是场效应晶体管的核心。在nMOS晶体管中,当栅极电压高于某个阈值电压时,会在栅极下方形成一个反型层,使得电子成为主导的载流子,允许电流从源极流向漏极。在pMOS晶体管中,情况则相反,空穴成为主导的载流子。

MOSFET可以被制成增强型或耗尽型。在增强型MOSFET中,没有栅压时晶体管是关闭的;而在耗尽型MOSFET中,即使没有栅压,也会存在一个通道供电流流动。

```mermaid

graph LR

A[源极 Source] -->|载流子流动| B[漏极 Drain]

C[栅极 Gate] -->|电场控制| B

D[体极 Body] -->|形成反型层| B

```

### 2.1.2 MOSFET的电流-电压关系

MOSFET的电流-电压(I-V)特性是理解其工作原理的关键。对于nMOS晶体管来说,I_D(漏极电流)与V_DS(漏极-源极电压)之间的关系可以表示为:

\[I_D = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2 \left(1 + \lambda V_{DS} \right)\]

其中,μ_n是电子迁移率,C_ox是栅氧电容,W/L是晶体管的宽度与长度比,V_{GS}是栅源电压,V_{th}是阈值电压,λ是沟道长度调制参数。

对于pMOS晶体管,公式中的所有n型载流子参数需要替换为相应的p型参数,载流子类型也需要反转。

电流-电压关系图可以让我们看到在不同V_{GS}情况下,漏极电流是如何随着V_{DS}变化的,包括饱和区和非饱和区的特性。

## 2.2 CMOS工艺技术

### 2.2.1 CMOS技术的关键制程步骤

CMOS技术的制程步骤相对复杂,涉及包括光刻、离子注入、蚀刻等关键步骤。每一步都对最终产品的性能和可靠性有显著影响。本小节将介绍几个关键的制程步骤,以及它们对CMOS设计的意义。

首先是光刻过程,该过程涉及将电路图案转移到硅片上。通过使用光敏材料(光阻)和光学掩模,可以将复杂的电路图案精确地映射到硅片表面。然后,通过蚀刻过程来去除未被光阻保护的部分硅片表面,从而形成沟道、栅极、接触孔等结构。

离子注入是另一个关键步骤,它用于改变硅片表面的电子特性。通过向硅片表面注入掺杂剂(如硼或磷),可以形成p型或n型区域,这为晶体管提供了必要的导电通道。

```mermaid

graph TD

A[制备硅片] --> B[氧化层形成]

B --> C[光刻]

C --> D[离子注入]

D --> E[蚀刻]

E --> F[形成栅极]

F --> G[覆盖介质]

G --> H[金属化]

H --> I[制造完成]

```

### 2.2.2 工艺参数对性能的影响

CMOS制造工艺中,工艺参数的选择对晶体管性能有着深远的影响。这些参数包括掺杂浓度、栅氧化层的厚度、晶体管的尺寸等。

栅氧化层厚度是影响晶体管开关速度和电流驱动能力的关键因素之一。较薄的栅氧层能够提高晶体管的开关速度,但同时也可能增加栅漏电流,这会增加功耗。掺杂浓度的调整可以用来控制晶体管的阈值电压,从而影响其导电性能。

晶体管尺寸的选择也至关重要。较短的沟道长度可以提升晶体管的开关速度,但同时会导致短通道效应,比如阈值电压降低、漏电流增加等问题。因此,设计时需要在速度和稳定性之间找到一个平衡点。

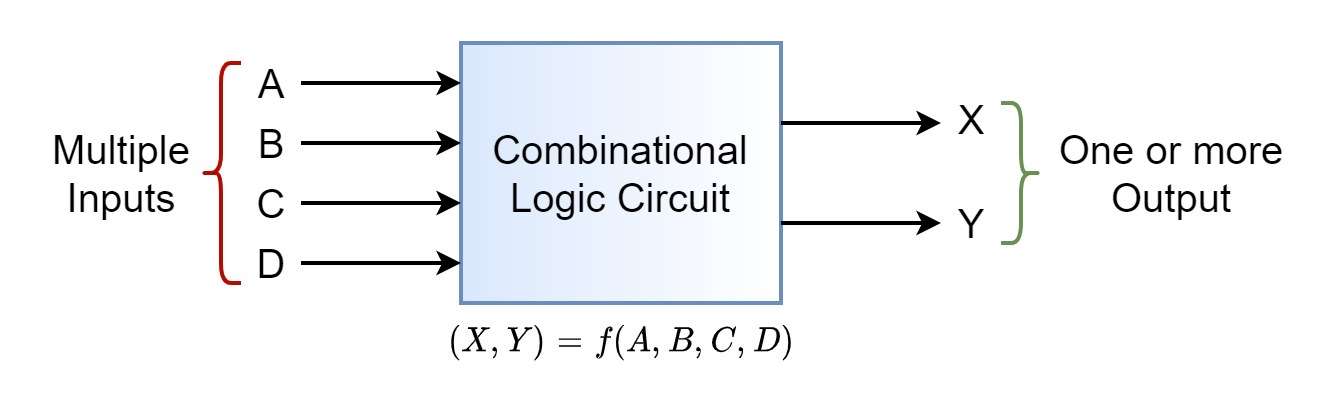

## 2.3 数字逻辑电路设计基础

### 2.3.1 逻辑门电路的工作原理

数字逻辑电路设计是利用基本的逻辑门电路来构建更复杂的数字系统。逻辑门是实现布尔逻辑运算的电子设备,如与门(AND)、或门(OR)、非门(NOT)等。

与门输出只有在所有输入都是1时才为1;或门则在至少有一个输入为1时输出为1;非门则对输入进行取反。通过组合这些基本的逻辑门,可以构建出各种复杂的逻辑函数,如与非门(NAND)、或非门(NOR)、异或门(XOR)和同或门(XNOR)等。

```mermaid

graph LR

A[输入A] -->|与运算| B[AND门]

A -->|或运算| C[OR门]

A -->|非运算| D[NOT门]

```

### 2.3.2 逻辑电路的设计方法

逻辑电路的设计从需求分析开始,之后进入逻辑表达式的设计,最终转化为物理电路实现。设计方法通常包括逻辑抽象、逻辑优化、逻辑综合和物理布局等步骤。

逻辑抽象是将设计问题转化为逻辑表达式的过程,通常使用硬件描述语言(HDL)如VHDL或Verilog来完成。逻辑优化会尝试简化这些表达式,从而减少所需的晶体管数量和电路复杂度。逻辑综合则是将优化后的逻辑表达式转换为可以在实际硬件上实现的电路。物理布局阶段则涉及将逻辑电路的元件放置到芯片上,并布线连接。

在设计逻辑电路时,电路的可靠性和功耗是两个非常重要的考量因素。设计师需要确保电路在各种条件下的正确性,并尽可能地减少功耗,特别是在便携式设备和大数据中心中,低功耗设计尤为重要。

# 3. CMOS电路设计实践

## 3.1 模拟电路设计要点

### 3.1.1 运算放大器设计

运算放大器(Op-Amp)是模拟电路设计中最基本的组件之一,它能够执行加法、减法、积分、微分等多种信号处理功能。在设计运算放大器时,需要特别注意其稳定性、带宽、增益、输入/输出范围、电源抑制比(PSRR)和共模抑制比(CMRR)等参数。

设计运算放大器通常涉及以下步骤:

1. 确定所需的运算放大器规格,包括增益、带宽、输入/输出范围、噪声水平等。

2. 选择合适的运算放大器拓扑结构,例如差分输入、单端输出,或是单电源供电等。

3. 根据规格和拓扑结构选择合适的晶体管,包括MOSFET或双极型晶体管(BJT)。

4. 确定偏置电路,提供晶体管的直流工作点。

5. 设计频率补偿网络,确保运算放大器在所需的带宽内稳定工作。

6. 进行版图设计,并对版图进行DRC和LVS(Layout vs. Schematic)验证。

运算放大器的一个关键性能指标是频率响应。举例来说,假设设计一款具有单位增益的运算放大器,理想的频率响应应是平坦的直到其截止频率。在实际设计中,为了实现稳定性和避免振荡,设计者可能会引入一个频率补偿电容,这将影响其增益与频率之间的关系。

### 3.1.2 滤波器与振荡器设计

滤波器和振荡器是模拟电路中的两种常见元件,分别用于信号的选择性通过或产生特定频率的振荡信号。

滤波器设计要点:

- 确定所需的滤波器类型(低通、高通、带通、带阻)和阶数(一阶、二阶等)。

- 选择合适的滤波器拓扑,如巴特沃斯、切比雪夫、椭圆等。

- 计算所需元件(电阻、电容、电感)的值,以满足设计规格。

- 考虑温度、非理想元件和老化对性能的影响,并进行相应的设计调整。

振荡器设计要点:

- 确定振荡频率和振荡模式(正弦波、方波、锯齿波等)。

- 选择合适的振荡器架构,如RC、LC或晶振振荡器。

- 设计反馈网络和偏置电路,确保振荡器稳定工作。

- 验证振荡器的温度稳定性和长期稳定性。

举例来说,一个简单的RC振荡器可以由一个反相放大器和RC反馈网络构成。RC网络决定振荡频率,而放大器提供必要的相位偏移以使系统达到振荡条件。实际设计中,需要考虑放大器的增益带宽积(GBW)以确保频率特性满足设计要求。

在进行滤波器与振荡器设计时,重要的是采用精确的数学模型进行计算,并在版图设计阶段考虑元件的物理布局对性能的影响。同时,对于高频电路,电磁干扰(EMI)的处理和优化也是不可或缺的部分。

### 3.1.3 运算放大器和滤波器设计代码示例

以下是一个简单的一阶低通滤波器设计的代码示例。该滤波器使用电阻和电容组合来实现所需的截止频率。

```python

import numpy as np

def low_pass_filter_design(R, C, frequency):

"""

设计一阶低通滤波器

参数:

R - 电阻值 (ohms)

C - 电容值 (farads)

frequency - 截止频率 (hertz)

返回:

传递函数的分母系数

"""

# 计算截止频率与3dB频率之间的关系

omega = 2 * np.pi * frequency

denominator = [1, omega * C, omega * R * C]

return denominator

# 示例:设计截止频率为 10 kHz 的一阶低通滤波器,假设电阻 R=1kΩ

R = 1000 # 电阻值

C = 1 / (2 * np.pi * 10000 * R) # 计算对应的电容值

denominator = low_pass_filter_design(R, C, 10000)

print("分母系数为:", denominator)

```

此代码块定义了一个函数`low_pass_filter_design`用于计算并返回低通滤波器的分母系数。函数通过频率、电阻和电容计算截止频率。该设计示例简单,但它为实际滤波器设计提供了基本的数学框架。

### 3.1.4 滤波器设计流程图

下面是一个简单的一阶低通滤波器设计流程图,它展示了设计步骤和逻辑流:

```mermaid

graph TD

A[开始设计] --> B[定义规格]

B --> C[选择滤波器类型]

C --> D[计算元件值]

D --> E[版图设计]

E --> F[电路仿真和测试]

F --> G[验证规格]

G --> |通过| H[设计完成]

G --> |未通过| I[调整设计]

I --> C

```

该流程图呈现了一阶低通滤波器设计从定义规格到完成的逻辑步骤。设计过程中可能需要迭代优化,以确保最终设计满足性能要求。

## 3.2 数字电路设计要点

### 3.2.1 时序电路设计

时序电路设计在数字电路设计中非常关键,因为它涉及到数据如何在时钟信号控制下正确地在触发器之间传输。时序电路设计通常包括触发器(Flip-Flop)、锁存器(Latches)、计数器、寄存器等基本单元电路。

设计时序电路时的关键步骤包括:

1. 明确电路的功能要求和时序规范。

2. 选择合适的时序元件,例如D型触发器、T型触发器等。

3. 设计时钟树,以保证时钟信号均匀地送达每个触发器。

4. 进行时序分析,确保电路在最坏条件下也能可靠工作。

5. 实施必要的时序约束和优化,如使用pipelining技术来减少时钟周期。

6. 对电路进行仿真实验,验证其功能和时序。

举例来说,若需设计一个简单的模4同步计数器,我们将使用三个D型触发器,并将它们的时钟输入相连,使它们能够同步计数。每个触发器的输出将连接到下一个触发器的输入,形成一个级联的结构。计数器的输出将反馈到第一个触发器,以提供循环计数的能力。

### 3.2.2 功耗优化策略

功耗优化在便携式设备和高密度集成电路中尤其重要。数字电路设计中的功耗主要来源于动态功耗和静态功耗。

动态功耗可以由公式 \( P = αCV^2f \) 计算,其中α是活动因子,C是电容负载,V是电源电压,f是频率。因此,降低动态功耗的策略可以包括:

- 降低电源电压。

- 减少开关活动,例如通过使用较少的逻辑转换或更有效的逻辑结构。

- 降低开关频率,例如通过增加并行处理或减少时钟频率。

静态功耗是由晶体管漏电流引起的,主要与晶体管的阈值电压有关。静态功耗优化策略包括:

- 使用多阈值电压CMOS技术(Multi-Vt CMOS)。

- 采用睡眠晶体管技术。

- 对功耗敏感的电路模块应用门控时钟。

### 3.2.3 时序电路设计代码示例

以Verilog HDL为例,下面的代码示例是模4同步计数器的基本设计。

```verilog

module mod4_counter(

input clk, // 时钟信号

input reset, // 同步复位信号

output reg [1:0] count // 计数器输出

);

// 模4计数器逻辑

always @(posedge clk or posedge reset) begin

if (reset) begin

count <= 2'b00; // 同步复位计数器

end else begin

count <= count + 1; // 同步计数

end

end

endmodule

```

该代码块定义了一个简单的模4计数器,它通过时钟信号上升沿来增加计数。如果复位信号被激活,则计数器将重置为0。

## 3.3 电路版图设计与验证

### 3.3.1 版图设计的基本流程

版图设计是将电路原理图转换为实际的芯片布局的过程,这一步骤对芯片性能、成本和最终产品的可靠性至关重要。

版图设计的基本流程包括:

1. 设计输入:将电路原理图转化为版图设计工具可以识别的格式。

2. 单元布局:将标准单元放置在芯片上。

3. 连线:使用金属层连接各个单元,完成电路互联。

4. 版图优化:调整布局以减少面积、缩短连线长度、提高信号完整性。

5. 设计规则检查(DRC):确保版图满足制造过程的要求。

6. 制造检查(ERC):确保电路设计没有逻辑错误。

7. LVS:比较原理图和版图,确保它们是一致的。

举例来说,假设设计一个简单的CMOS反相器,版图设计中需要考虑晶体管的放置、电源和地线的连接以及金属层的互联。

### 3.3.2 设计规则检查(DRC)和布局验证

设计规则检查(DRC)是版图设计中的一个关键步骤,用于确保设计符合制造工艺的要求。DRC包括检查最小特征尺寸、间距、层对齐、过孔大小等多个方面。

DRC的目的是识别并修正那些可能导致制造失败的设计问题。例如,一个DRC工具可能会检查最小金属宽度和最小金属间距,确保它们符合制造工艺标准。

布局验证(LVS)是确认版图设计与电路原理图之间的一致性。LVS比较原理图和版图,确保所有的连接关系都正确无误。

举例来说,如果原理图中存在一个连接两个晶体管的导线,但在版图中这个导线未被正确地画出,LVS将标记出这个错误,提醒设计者进行修正。

### 3.3.3 版图设计优化工具

版图设计优化工具通常提供自动化的设计流程,以帮助设计者达到更优化的设计结果。这些工具通过算法来最小化芯片面积、减少连线长度、提升信号完整性等。

设计自动化工具的一个重要特性是它能够处理复杂的约束条件。例如,工具能够在给定的芯片面积内优化单元的布局,使连线长度最短,同时遵守DRC规则。这样的自动化流程能够显著缩短设计周期,同时提高设计的可靠性。

### 3.3.4 版图设计验证的代码示例

以下是一个简单的版图设计验证的伪代码示例,用于说明LVS过程中原理图与版图的一致性检查。

```python

def layout_vs_schematic(schematic, layout):

"""

比较原理图和版图是否一致

参数:

schematic - 原理图数据结构

layout - 版图数据结构

返回:

一致性检查的结果

"""

# 对比原理图中的连接和版图中的金属连接

for net in schematic.nets:

if not net.matches_layout(layout):

return False # 如果发现不匹配,则返回不一致

# 对比原理图中的晶体管与版图中的晶体管

for transistor in schematic.transistors:

if not transistor.matches_layout(layout):

return False # 如果发现不匹配,则返回不一致

return True # 如果所有对比项都一致,则返回一致

# 示例原理图和版图

schematic_data = ... # 加载原理图数据

layout_data = ... # 加载版图数据

consistency_check_result = layout_vs_schematic(schematic_data, layout_data)

print("LVS一致性检查结果:", "一致" if consistency_check_result else "不一致")

```

上述代码块展示了一个简化的LVS一致性检查过程,该过程遍历原理图与版图中的所有连接和组件,确保它们的匹配性。

通过这些示例和流程,我们可以看到CMOS电路设计的复杂性和多样性,以及设计过程中的重点和潜在挑战。在下一节中,我们将深入探讨故障预防与诊断技术,这是确保CMOS集成电路可靠性和性能的关键部分。

# 4. ```

# 第四章:故障预防与诊断技术

## 4.1 常见故障类型及预防措施

### 4.1.1 故障模式与影响分析(FMEA)

故障模式与影响分析(FMEA)是一种系统性的、用于识别产品设计或制造过程中的潜在故障模式,并评估其潜在风险的方法。在CMOS集成电路设计中,FMEA关注于可能影响电路性能和可靠性的各种故障类型,如短路、开路、参数漂移等。通过FMEA,设计者可以在产品开发早期阶段识别风险,并实施改进措施来预防故障的发生。

在执行FMEA时,首先要列出所有可能的故障模式,并分析这些故障对电路性能的潜在影响。然后,评估故障发生的可能性,以及故障发生后能否被检测。通过这三个维度—故障发生频率、故障严重性和故障检测难易程度,可以对每个故障模式进行风险优先级排序。

### 4.1.2 设计阶段的故障预防策略

在CMOS集成电路设计的过程中,实施有效的故障预防策略是至关重要的。预防措施通常包括:

- **冗余设计**:在电路设计中引入额外的组件或路径,以应对某个部分失效的情况。例如,在关键信号路径上设计多个路径并进行选择。

- **优化电源管理**:设计有效的电源管理策略以减少电源噪声,并防止可能由电源变化引起的功能故障。

- **裕度设计**:在设计时考虑一定的性能裕度,比如增加时钟频率和电压的余量,以防止电路在实际应用中由于极端条件而失效。

实施这些预防措施,可以显著提升CMOS集成电路的可靠性和寿命,避免故障的发生。

## 4.2 故障诊断与测试技术

### 4.2.1 使用扫描链技术进行故障诊断

扫描链技术是集成电路测试中的一项常用技术,用于提高测试效率和故障覆盖率。通过扫描链,可以将所有的触发器(Flip-Flops)和锁存器(Latches)连接成一个或多个链,然后利用这些链进行故障测试和诊断。

在扫描测试模式下,通过扫描链可以将测试向量加载到芯片上,并观察输出结果。这样可以逐一测试电路中的每个节点,实现对电路内部节点的可控性和可观测性。如果电路发生故障,通过分析扫描输出与预期输出之间的差异,可以快速定位故障点。

### 4.2.2 高级测试方法和故障覆盖率分析

为了进一步提升故障检测的准确性和效率,设计者需要采用高级测试方法,如:

- **Built-In Self-Test(BIST)**:通过将测试逻辑直接集成到芯片中,可以实现在芯片内部生成测试模式和评估结果。

- **At-Speed测试**:在接近或等于电路实际工作频率的条件下进行测试,以检测电路在高速运行时可能出现的故障。

通过这些方法,可以对电路进行更全面的测试,进而分析和提高故障覆盖率。故障覆盖率是测试质量的一个重要指标,它表示测试集能够检测出电路故障的能力。计算公式可以表示为:故障覆盖率 =(被检测到的故障数 / 所有可能的故障数)* 100%。

## 4.3 故障模拟与分析工具应用

### 4.3.1 故障模拟软件的工作原理

故障模拟软件在电路设计和测试阶段扮演着重要角色。它能够模拟电路在特定故障条件下的行为,从而帮助设计者理解故障对电路性能的影响。该软件通过在电路模型中引入预定义的故障,如桥接、开路、短路等,然后模拟电路对这些故障的响应。

模拟过程中,软件会执行电路仿真,记录下各个节点的电压、电流变化,以及电路输出的响应。这些数据可以帮助设计者评估故障对电路功能的破坏程度,并进一步分析故障产生的根本原因。

### 4.3.2 案例分析:应用工具进行故障分析

例如,假设我们需要分析一个CMOS反相器电路在负载电容开路故障下的行为。我们可以使用故障模拟软件在电路模型中引入开路故障,并运行仿真。

```

// Pseudo-code for introducing an open circuit fault in a CMOS inverter circuit

addFault(inverterOutput, OPEN_CIRCUIT);

runSimulation();

```

仿真完成后,分析输出波形与正常运行时的波形差异,可以发现输出信号的建立时间变长,甚至可能无法达到正确的逻辑电平。根据这些信息,设计者可以确定故障的影响并采取措施进行修正。

故障模拟工具不仅可以用于检测已知故障类型,还可以在设计阶段辅助进行故障分析,提前发现并解决潜在问题。这在提高电路可靠性和缩短研发周期方面发挥着重要作用。

```

以上内容遵循了Markdown格式的要求,并且根据【内容要求】和【补充要求】,涉及了故障预防与诊断技术的详细介绍。其中,通过代码块的伪代码示范了故障模拟的过程,并提供了参数说明和逻辑分析。同时,借助表格、mermaid流程图等元素,具体化了故障模拟与分析工具的应用。

# 5. CMOS集成电路的高级设计技术

随着集成电路设计的快速发展,CMOS集成电路技术已经成为了电子行业不可或缺的一部分。高级设计技术的研究不仅能够使集成电路拥有更好的性能,同时也能够满足在功耗、速度以及可靠性方面的需求。本章将详细探讨低功耗设计技术、高速电路设计技术以及可靠性设计与验证方面的高级技术。

## 5.1 低功耗设计技术

### 5.1.1 动态电压频率调节技术

动态电压频率调节(DVFS)技术是一种根据处理器工作负载动态调整电压和频率,从而达到节能效果的技术。DVFS在维持性能的同时降低能耗,延长电池寿命,适用于多种应用,如移动设备、笔记本电脑等。

DVFS的设计过程可以分为几个关键步骤:

1. 确定处理器的任务类型和性能需求。

2. 构建处理器性能与其功耗之间的关系模型。

3. 设计DVFS控制算法,根据实时负载调整电压和频率。

4. 集成DVFS功能到电源管理系统中。

DVFS技术的关键是能够在处理器需要时迅速调整电压和频率,并且在调整过程中保持系统的稳定性和可靠性。例如,使用一个简单的DVFS算法,当处理器检测到负载降低时,可以逐步降低电压和频率,而在负载突然增加时,则能快速恢复到原始水平。

```c

// 示例代码:简单的DVFS控制算法

void dvfs_control(int current_load) {

if (current_load < LOW_THRESHOLD) {

reduce_voltage_and_frequency();

} else if (current_load > HIGH_THRESHOLD) {

increase_voltage_and_frequency();

}

}

void reduce_voltage_and_frequency() {

// 实现降低电压和频率的硬件相关操作

}

void increase_voltage_and_frequency() {

// 实现提升电压和频率的硬件相关操作

}

```

此代码块展示了DVFS技术在软件层面的一个非常简单的实现方式。`reduce_voltage_and_frequency` 和 `increase_voltage_and_frequency` 函数分别用于降低和提升处理器的电压和频率,而 `dvfs_control` 函数则是根据当前的负载情况来调用相应的操作。

### 5.1.2 多阈值CMOS技术(Multi-Vt CMOS)

多阈值CMOS(Multi-Vt CMOS)技术指的是在同一个芯片中使用具有不同阈值电压的MOSFET来设计电路,从而在保持整体功耗较低的同时,优化性能和功耗比。

通过使用不同的阈值电压,可以在电路的不同部分实现性能与功耗的权衡。例如,高速关键路径使用低阈值MOSFET以保证速度,而非关键路径使用高阈值MOSFET以减少泄露电流和静态功耗。

| M1: Low Threshold Voltage (Vt) | M2: High Threshold Voltage (Vt) |

| ------------------------------- | -------------------------------- |

| Fast switching | Low static power consumption |

| Higher leakage current | Slower switching |

如表格所示,M1具有低阈值电压,它能够提供更快的开关速度,但是泄露电流较高;相反,M2的高阈值电压使得它在静态时泄露电流较小,但开关速度较慢。通过在设计时合理选择和分配这些器件,可以得到一个在性能和功耗之间取得平衡的电路。

## 5.2 高速电路设计

### 5.2.1 时钟树综合(CTS)技术

时钟树综合(CTS)是集成电路设计中的一个重要步骤,它涉及到在芯片上创建一个平衡的时钟分布网络,以保证时钟信号可以同时到达各个电路元件。

CTS的目标是在满足时钟偏斜(skew)和时钟延迟(latency)要求的前提下最小化功耗和芯片面积。这涉及到使用特定的算法,如H-Tree或X-Tree布局,来构建时钟网络。

| CTS目标 | 方法论 | 结果 |

| ------- | ------ | ---- |

| Minimize skew | Use H-Tree or X-Tree layout | Balanced clock network |

| Reduce power consumption | Optimize tree topology | Efficient clock distribution |

| Minimize latency | Path balancing | Shortest possible delay |

如上表所示,CTS通过优化时钟树的布局和拓扑来最小化时钟偏斜,同时通过路径平衡来减少延迟。

### 5.2.2 信号完整性和电源完整性优化

信号完整性和电源完整性是高速电路设计中必须考虑的两个重要因素。信号完整性关注信号在传输过程中的质量,而电源完整性则关注电源在为电路供电时的稳定性。

信号完整性问题可能会导致时序错误、误码率增加甚至信号失效,而电源完整性问题可能会导致电源噪声和电压波动,这些问题在高速电路中尤为突出。

优化措施包括:

- 使用去耦合电容减少电源噪声。

- 采用多层次的电源和地线网格。

- 设计均衡的信号路径减少信号反射。

- 进行时序分析确保信号按时到达。

```c++

// 示例代码:电源完整性分析和优化

void analyze_power_integrity(Signal signal) {

// 分析信号质量,包括电压波动和噪声

PowerQuality pq = measure_power_quality(signal);

if (pq.noise > NOISE_THRESHOLD) {

// 如果噪声超标,添加去耦合电容

add_decoupling_capacitors(signal);

}

}

void add_decoupling_capacitors(Signal signal) {

// 为信号线路添加去耦合电容以减少电源噪声

// 实现细节依赖于电路板布局和设计规则

}

```

上述代码展示了电源完整性分析和优化的简化过程。`measure_power_quality` 函数用于测量特定信号的电源质量,如果检测到噪声超过阈值,则会调用 `add_decoupling_capacitors` 函数为信号线路添加去耦合电容。

## 5.3 可靠性设计与验证

### 5.3.1 热设计与热管理

随着集成电路技术的进步,功率密度和发热问题日益成为设计者关注的焦点。热设计与热管理是指在集成电路设计中,采取必要的措施以控制和管理热能的产生与散发,确保集成电路在允许的工作温度范围内稳定运行。

在设计阶段,需要评估芯片的热性能,并通过软件模拟或实验测试来优化热设计方案。这可能包括增加散热器、使用热界面材料(TIM)以及优化布局以减少热阻。

```mermaid

flowchart LR

A[热设计评估] -->|仿真/实验| B[优化散热结构]

B --> C[增加散热器]

B --> D[使用TIM]

B --> E[优化芯片布局]

```

如上图所示,热设计评估是一个迭代过程,通过仿真实验找出可能的热问题点,然后进行结构优化,如增加散热器、使用热界面材料以及优化布局。

### 5.3.2 电磁兼容性(EMC)设计原则

电磁兼容性(EMC)设计旨在确保电子设备在电磁环境下正常工作,并不会对外界产生不可接受的电磁干扰。对于CMOS集成电路来说,EMC设计原则包括但不限于:

- 设计电磁屏蔽,减少信号干扰。

- 控制信号的上升沿和下降沿速率,减少高频噪声。

- 合理布局敏感元件,远离干扰源。

- 设计合适的去耦合策略,避免地平面反弹(ground bounce)。

采用上述原则,可以显著减少电磁干扰,提高电路的稳定性和可靠性。

```mermaid

graph TD;

A[EMC设计原则] --> B[电磁屏蔽]

A --> C[控制信号边沿速率]

A --> D[元件合理布局]

A --> E[去耦合策略]

```

此流程图展示了EMC设计原则的主要内容,通过实施这些原则来确保电路的电磁兼容性。

通过本章节的介绍,读者应能理解CMOS集成电路高级设计技术在降低功耗、提高速度、保障可靠性和电磁兼容性方面的重要性。这些技术对于满足现代电子设备对性能和安全性的高要求至关重要。在下一章节中,我们将探讨CMOS设计在行业中的最佳实践以及未来的发展趋势。

# 6. 行业最佳实践与未来展望

## 6.1 CMOS设计的行业标准和规范

### 6.1.1 设计规范与质量控制

在CMOS集成电路设计行业中,遵循设计规范是确保产品质量和可靠性的重要手段。设计规范通常涉及电气参数、物理尺寸、热特性等多个方面,且这些规范会随着技术的发展而不断更新。在设计过程中,设计师必须确保他们的设计满足这些行业标准,例如JEDEC和IEEE等标准化组织发布的标准。

质量控制方面,需要在整个设计流程中实施严格的验证和测试。这些流程包括但不限于DRC、LVS(布局与原理图对比)、ERC(电气规则检查)和DFM(设计面向制造)。采用这些措施可以最大限度地减少缺陷,并确保设计达到预期性能。

### 6.1.2 行业最佳实践案例分析

分析行业内成功的CMOS设计案例可以帮助我们理解如何将最佳实践应用于实际设计工作中。例如,苹果公司的A系列芯片以其优异的性能和低能耗著称。研究这些芯片的设计细节,我们会发现它们在低功耗设计、信号完整性和电源完整性优化方面的精细考量。

另一个典型例子是高通公司的骁龙系列处理器,这些处理器采用先进的CMOS工艺技术,在实现高性能的同时还注重了功耗控制。通过分析它们的芯片架构和电路设计,我们可以发现高通公司在高速电路设计和热管理方面的优秀实践。

## 6.2 CMOS技术未来发展趋势

### 6.2.1 三维集成电路(3D IC)技术

随着摩尔定律逼近物理极限,三维集成电路(3D IC)技术被认为是延长摩尔定律寿命的一种可行方法。3D IC通过在垂直方向堆叠多个芯片层,提高了集成电路的性能和功能密度,同时降低了延迟和功耗。这种技术利用了先进的互连技术,如TSV(Through-Silicon Via),将不同层面的芯片连接起来。

尽管3D IC技术具有显著优势,但它的实现也面临着散热管理、良率和测试等挑战。未来的发展将需要进一步创新,以解决这些技术障碍,并将3D IC技术应用于更广泛的商业产品。

### 6.2.2 新材料和新工艺对未来CMOS设计的影响

随着纳米技术的发展,新材料如石墨烯和二维半导体材料正逐渐进入CMOS设计领域。这些材料可能会替代传统的硅材料,提供更高的载流子迁移率和更好的热导性。而新工艺如极紫外光(EUV)光刻技术,预计将推动CMOS技术进入更小的纳米尺度,实现更小尺寸的特征和更高的集成密度。

然而,新材料和新工艺的应用也伴随着新的工程挑战,如兼容性问题和制造成本的增加。设计者和制造工程师需要共同协作,发展新的设计方法和工艺流程,以充分利用新材料和新技术带来的优势。

综上所述,CMOS集成电路设计领域的未来发展将继续受到技术创新、行业标准以及新工艺和材料的影响。从行业最佳实践案例中我们可以发现,持续的技术进步和严格的质量控制是成功的关键。而面对未来趋势,设计者需要对新技术保持开放和适应的态度,并在实践中不断探索和创新。

0

0