UVM环境组件构建与优化:实现极致性能的五大方法

发布时间: 2025-01-02 17:58:03 阅读量: 7 订阅数: 12

uvm_example:SystemVerilog UVM环境示例

# 摘要

本文全面介绍UVM(Universal Verification Methodology)环境的组件构建与优化策略。首先概述了UVM环境组件的构建与优化概念,然后详细阐述了UVM组件的理论基础、事务与驱动组件、监视器与记分板的构建方法。接下来,文章探讨了性能优化策略,包括事务生成、资源管理和测试时序控制。此外,本文还分享了UVM环境组件构建的实践经验,包括可重用组件的创建、集成测试和环境调试与维护。最后,本文通过高级应用案例分析和性能优化效果评估,展示了UVM在复杂系统验证中的高效性和实用性。本文旨在为验证工程师提供系统性的UVM应用知识,以提高设计验证效率和质量。

# 关键字

UVM环境;组件构建;性能优化;事务管理;资源调度;验证效率

参考资源链接:[UVM基础学习.ppt](https://wenku.csdn.net/doc/646052ec543f8444888df3da?spm=1055.2635.3001.10343)

# 1. UVM环境组件构建与优化概述

随着集成电路设计复杂性的不断增加,UVM(Universal Verification Methodology)已经成为业界公认的验证环境构建和管理的标准方法学。构建一个高效且可复用的UVM验证环境,对于缩短产品上市时间和降低研发成本至关重要。在这一章中,我们将从宏观角度介绍UVM环境组件构建的基础理念以及优化策略,并展望其在现代集成电路设计中的应用和未来发展趋势。

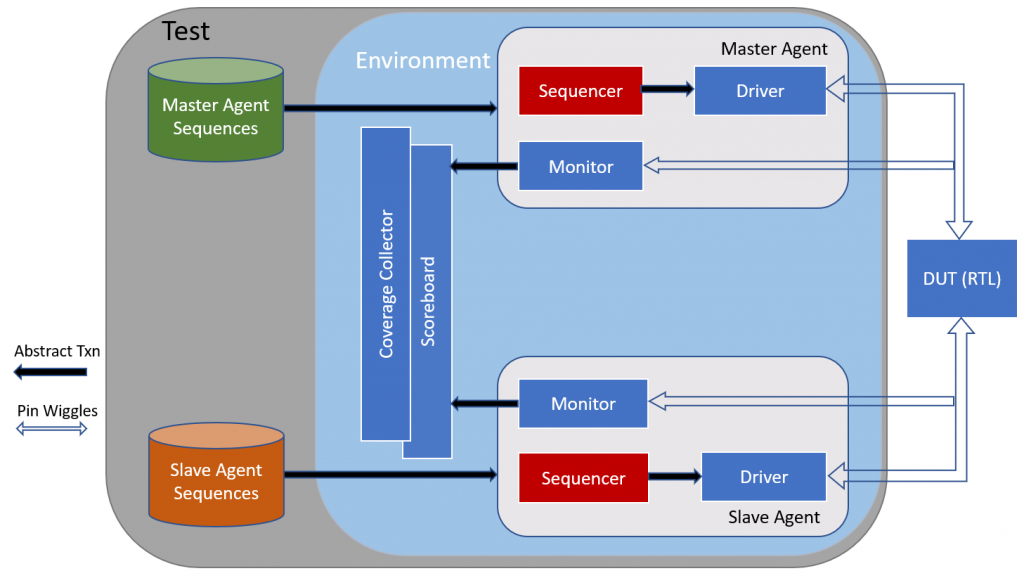

## 1.1 UVM验证环境的组成元素

UVM验证环境由多个组件组成,包括但不限于驱动器(driver)、监视器(monitor)、记分板(scoreboard)、代理(agent)和环境(environment)本身。每个组件都具有特定的功能,并以一种高度模块化的方式协同工作,以实现复杂场景下的设计验证。

## 1.2 环境构建与优化的重要性

构建和优化UVM验证环境是确保项目成功的关键步骤。一个精心构建的环境不仅可以提高测试效率,还能保证可复用性和可扩展性,这对于后期可能的维护和升级尤为重要。优化策略包括组件间的高效通信、事务生成的优化、资源管理,以及时序控制等关键方面。

通过后续章节,我们将深入探讨UVM环境组件的构建方法和性能优化策略,帮助读者全面掌握UVM环境组件构建与优化的实践技能。

# 2. ```

# 第二章:UVM组件的理论基础与构建方法

UVM (Universal Verification Methodology) 作为基于SystemVerilog的验证方法学,已经成为硬件设计验证领域的事实标准。理解UVM组件的理论基础和构建方法是深入学习UVM并应用于复杂项目的关键。本章节将详细介绍UVM组件的基本概念、生命周期、事务与驱动组件的构建,以及监视器与记分板的构建。

## 2.1 UVM组件的基本概念

### 2.1.1 UVM组件的定义与分类

UVM组件是基于SystemVerilog的面向对象编程(OOP)构建模块,其用于创建、管理和组织验证环境中的各个部分。UVM组件可以分为三个主要类别:序列器(Sequencer)、驱动器(Driver)和监视器(Monitor)。序列器负责生成事务(Transaction),驱动器接收序列器发出的事务并将其转换为DUT(设计单元)可理解的信号,而监视器则负责从DUT获取信号,并将其转换为事务以供进一步分析。此外,UVM还提供了记分板(Scoreboard)用于比较预期结果和DUT的实际输出。

### 2.1.2 UVM组件的生命周期

UVM组件的生命周期由一系列预定义的阶段组成,这些阶段包括`build_phase`、`connect_phase`、`end_of_elaboration_phase`、`start_of_simulation_phase`、`run_phase`和`extract_phase`等。每个阶段都提供了在组件创建和执行过程中进行操作的时机。`build_phase`阶段是用于构建组件层次结构,`connect_phase`阶段用于连接组件,而`run_phase`阶段则实际上执行事务。这些阶段确保了组件能够在正确的时刻执行必要操作,从而实现验证环境的正确配置和运行。

## 2.2 UVM事务与驱动组件的构建

### 2.2.1 事务类的创建与定制

事务是驱动DUT行为的基础。在UVM中,事务通常由自定义的类来表示,这些类继承自`uvm_transaction`基类。创建事务类时,需要定义适合特定验证需求的属性和方法。例如,对于一个简单的总线协议,事务类可能需要包含地址、数据和控制信号等字段。在自定义事务类时,还需提供复制(copy)、比较(compare)和打印(print)等方法,以便在监视器和记分板中使用。

```systemverilog

class my_transaction extends uvm_transaction;

rand bit [31:0] address;

rand bit [31:0] data;

rand bit write_enable;

// Constraints for address and data

constraint valid_address { address inside {[0:1023]}; }

constraint valid_data { data inside {[0:65535]}; }

// Mandatory methods

function new(string name = "my_transaction");

super.new(name);

endfunction

// Additional methods

function void do_copy(uvm_transaction rhs);

if ($cast(this, rhs)) begin

// Perform deep copy

end

endfunction

function bit do_compare(uvm_transaction rhs, output string diff);

// Perform comparison and report differences

endfunction

function void do_print(uvm_port printer);

// Print transaction information

endfunction

endclass

```

### 2.2.2 驱动组件的设计原则

驱动组件(Driver)的设计原则是将事务转换为DUT的信号和行为。UVM驱动是一个继承自`uvm_driver`的类,它需要实现`main_phase`,在该方法中驱动器接收来自序列器的事务,并将其应用于DUT。为了支持不同的事务类型,驱动器通常实现`uvm_sequence_item`接口,该接口允许驱动器与多个事务类协同工作。此外,驱动器还可能需要实现`build_phase`、`connect_phase`等其他生命周期阶段的方法。

```systemverilog

class my_driver extends uvm_driver #(my_transaction);

virtual my_if vif; // Virtual interface to DUT

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

// Get the virtual interface from the UVM resource database

endfunction

virtual task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(req);

// Drive the transaction onto the DUT using vif

seq_item_port.item_done();

end

endtask

endclass

```

## 2.3 UVM监视器与记分板的构建

### 2.3.1 监视器组件的作用与实现

监视器(Monitor)的作用是观察DUT的输出信号,并将其转换为事务对象以供后续处理。监视器通常包含一个或多个监听器(Listener)组件,它们负责检测接口上的信号变化并捕获相应的事务。监视器继承自`uvm_monitor`类,并实现`main_phase`和`report_phase`等生命周期阶段。监视器还需要处理信号与事务对象之间的转换,并将转换后的事务推送到一个通道(`uvm_analysis_port`),供其他组件如记分板使用。

```systemverilog

class my_

0

0