UVM性能测试与验证:全方位提升测试深度与广度

发布时间: 2025-01-02 18:53:17 阅读量: 4 订阅数: 12

数字IC验证+UVM验证+异步FIFO验证+笔试分享

# 摘要

UVM(Universal Verification Methodology)作为现代数字电路验证的主流方法,其性能测试与验证部分至关重要。本文首先介绍了UVM性能测试的基础知识和理论框架,包括验证方法学的重要性、UVM框架组件结构、性能测试指标以及测试规划与设计的关键步骤。随后,本文深入探讨了UVM性能测试实践操作中的序列与驱动优化、监视器与分析器的性能数据处理,以及性能瓶颈的识别与解决。接着,文章进一步介绍了高级技术,例如UVM中的多线程应用、事务级建模(TLM)和测试的自动化与持续集成。最后,通过案例分析,总结了UVM性能测试的工具和插件应用,并对UVM性能测试的未来趋势进行了展望,强调了适应不断变化的技术挑战和发展方向的重要性。

# 关键字

UVM;性能测试;验证方法学;事务级建模;自动化测试;持续集成

参考资源链接:[UVM基础学习.ppt](https://wenku.csdn.net/doc/646052ec543f8444888df3da?spm=1055.2635.3001.10343)

# 1. UVM性能测试与验证基础

UVM(Universal Verification Methodology)是电子设计自动化(EDA)领域广泛使用的一种验证方法学,它在芯片设计和系统级芯片(SoC)设计的性能测试和验证中扮演着至关重要的角色。本章将深入介绍UVM的基本概念、性能测试的重要性,以及在验证过程中需要遵循的基础原则和实践策略。

## 1.1 UVM验证方法学概述

### 1.1.1 验证方法学的重要性

验证是确保硬件设计符合其规格要求的关键过程。良好的验证方法学可以显著提高设计的可靠性和性能,降低项目的风险。UVM是目前业界公认的先进验证方法学,其模块化和可重用性设计能够应对日益复杂的验证挑战。

### 1.1.2 UVM框架组件和结构

UVM框架主要由以下几个核心组件构成:

- 测试环境(Testbench):定义了验证环境的结构,包括所有的组件和它们之间的交互。

- 事务(Transaction):表示在测试环境中交换的数据包,是测试的基础单元。

- 序列(Sequence):负责生成事务,通过驱动(Driver)发送到被测设备(DUT)。

- 驱动(Driver)、监视器(Monitor)、和分析器(Scoreboard):各自承担着数据发送、监视以及结果校验的职责。

- 配置(Configuration):用于自定义和调整UVM环境的行为。

通过这些组件,UVM能够创建出可扩展、可重用的测试环境,极大提高了验证效率和测试覆盖率。在下一章节中,我们将深入探讨UVM性能测试的相关理论和方法论,以及性能测试指标的详细解析。

# 2. UVM性能测试理论与方法论

## 2.1 UVM验证方法学概述

### 2.1.1 验证方法学的重要性

验证方法学作为系统级验证的基石,它对确保设计的功能正确性和性能符合预期起着至关重要的作用。在现代复杂集成电路(IC)设计中,验证工作往往占据了整个项目开发周期的大部分时间。UVM(Universal Verification Methodology)是一种基于SystemVerilog语言的验证方法学,它提供了一个全面的、可重用的验证环境,能够大大提升验证效率,降低项目成本。它的重要性体现在以下几个方面:

- **标准化和可重用性**:UVM定义了一套标准的验证组件和流程,使得验证工程师能够构建起可复用的测试平台,并且能够在不同的项目之间共享这些组件。

- **并行化和加速验证**:通过使用UVM的并发测试机制,可以同时运行多个测试序列,加速验证进度,并且并行化处理可以缩短产品上市时间。

- **提高验证质量**:UVM提供了丰富的监控和检查机制,帮助确保设计在各种边界条件下都能按照预期工作,从而提高整个系统的验证质量。

### 2.1.2 UVM框架组件和结构

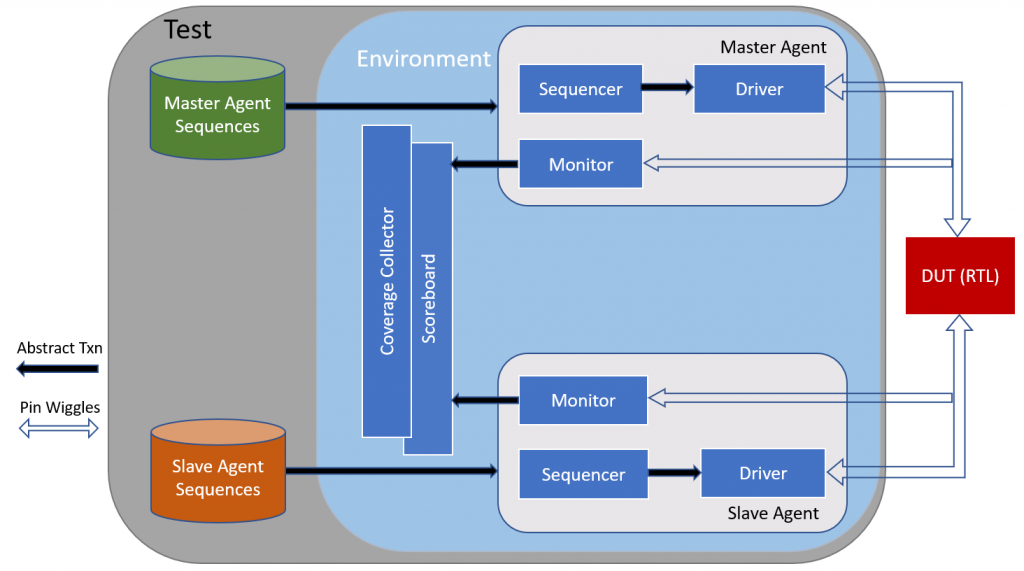

UVM验证框架的核心组件包括:驱动(Driver)、监视器(Monitor)、代理(Agent)、序列(Sequences)、记分板(Scoreboard)、测试(Test)和环境(Environment)。各组件在UVM验证框架中的结构和作用如下:

- **驱动(Driver)**:驱动的任务是接收待发送的事务,并将其转换为DUT(Device Under Test)能够理解的信号,模拟实际的硬件环境。

- **监视器(Monitor)**:监视器负责监视DUT的接口,并将观察到的事务数据传递给分析器和记分板。

- **代理(Agent)**:代理封装了驱动和监视器,它作为整体与DUT交互,并可以被配置为特定的模式(例如主动模式或被动模式)。

- **序列(Sequences)**:序列定义了一系列的事务,用于测试DUT的各种操作。

- **记分板(Scoreboard)**:记分板用于比较预期结果与实际输出结果,检测功能是否正确实现。

- **测试(Test)**:测试定义了整个验证过程中的步骤和流程,包括创建环境,启动序列等。

- **环境(Environment)**:环境包含了一组代理,并提供一个统一的接口来运行所有的测试案例。

## 2.2 UVM性能测试指标

### 2.2.1 基本性能指标解析

在UVM性能测试中,基本性能指标包括吞吐量(Throughput)、延迟(Latency)、资源利用率(Resource Utilization)等。这些指标是衡量系统性能的关键因素,因此必须被精确测量和评估:

- **吞吐量**:定义为单位时间内完成的事务数量,是衡量系统处理能力的重要指标。

- **延迟**:是指一个事务从生成到完成所需的时间,它是评估系统响应速度的关键指标。

- **资源利用率**:包括CPU、内存等资源的使用情况,高资源利用率可能会成为系统性能的瓶颈。

### 2.2.2 性能指标的度量和评估

为了准确评估UVM的性能指标,我们可以采用以下方法:

- **使用UVM的监视器和分析器**:监视器可以捕获所有事务并记录事件,分析器可以处理这些事务,并计算性能指标。

- **时间戳和计数器**:在UVM中,利用时间戳记录事务开始和结束的时间,使用计数器来记录事务数量,可以方便地计算吞吐量和延迟。

- **性能监控工具**:使用专业的性能监控工具,如SystemVerilog中的$realtime、$time等内建函数,可以获取更精确的时间度量值。

## 2.3 UVM性能测试的规划与设计

### 2.3.1 测试计划的重要性

测试计划是整个性能测试活动的指导性文件,它详细描述了测试的目标、测试策略、测试资源分配等关键信息。制定一个良好的测试计划能够确保性能测试的顺利进行,重点包括:

- **明确性能测试的目标和范围**:在测试计划中明确列出需要验证的性能指标,以及测试的范围和边界条件。

- **选择合适的测试场景**:针对不同的性能指标选择或设计合适的测试场景,以达到测试目的。

- **确定资源分配和进度安排**:对人员、硬件、软件等资源进行合理分配,并规划出测试的进度和时间表。

### 2.3.2 测试环境的搭建

测试环境的搭建包括硬件环境和软件环境的配置,这对于保证性能测试的准确性和有效性至关重要。在UVM测试环境中,通常需要搭建如下:

- **仿真环境**:建立相应的仿真环境,包括DUT的实例化、接口的配置等。

- **测试平台**:构建UVM测试平台,包括环境搭建、测试序列的编写等。

- **监控和分析工具**:配置用于收集性能数据的监控工具和分析工具。

### 2.3.3 测试案例的设计

测试案例的设计需要根据测试目标来制定,测试案例应该能够全面覆盖所有的功能和边界条件,测试案例的设计流程大致如下:

- **分析DUT的性能要求**:针对DUT的性能指标和应用场景,确定测试案例应该覆盖的功能点。

- **编写测试序列**:根据分析结果编写测试序列,测试序列需要能够产生高负载、边界条件等。

- **制定测试步骤和方法**:明确每个测试案例的步骤,以及如何运行和分析测试结果。

在本章节中,我们由浅入深地介绍了UVM性能测试的基础理论和方法论,从UVM验证方法学的核心组件和结构,到性能测试指标的解析与评估,再到测试规划、环境搭建和测试案例设计的深入解析。下一章节,我们将进入UVM性能测试实践操作,深入探讨序列与驱动的性能测试、监视器和分析器的性能测试,以及性能瓶颈的分析与优化。

# 3. UVM性能测试实践操作

## 3.1 UVM序列和驱动的性能测试

### 3.1.1 序列的生成和控制

在UVM验证环境中,序列(Sequences)是用来生成一系列事务(Transactions)的对象,这些事务最终会被驱动(Drivers)发送到被测试的设备上。序列生成器是性能测试的一个关键点,因为它决定了测试的范围和强度。为了进行性能测试,序列必须能够高效地生成和控制事务,以达到模拟高负载的目的。

实现高效序列生成的关键在于良好的设计和算法的选择。例如,使用随机序列生成器可以模拟真实场景中的随机性和不可预测性。此外,控制序列生成的速度和顺序,可以帮助验证在特定条件下的性能瓶颈。

```systemverilog

class performance_seq extends uvm_s

```

0

0