74LS169与FPGA的完美搭档:如何结合应用实现设计创新

发布时间: 2024-12-13 21:36:57 阅读量: 8 订阅数: 11

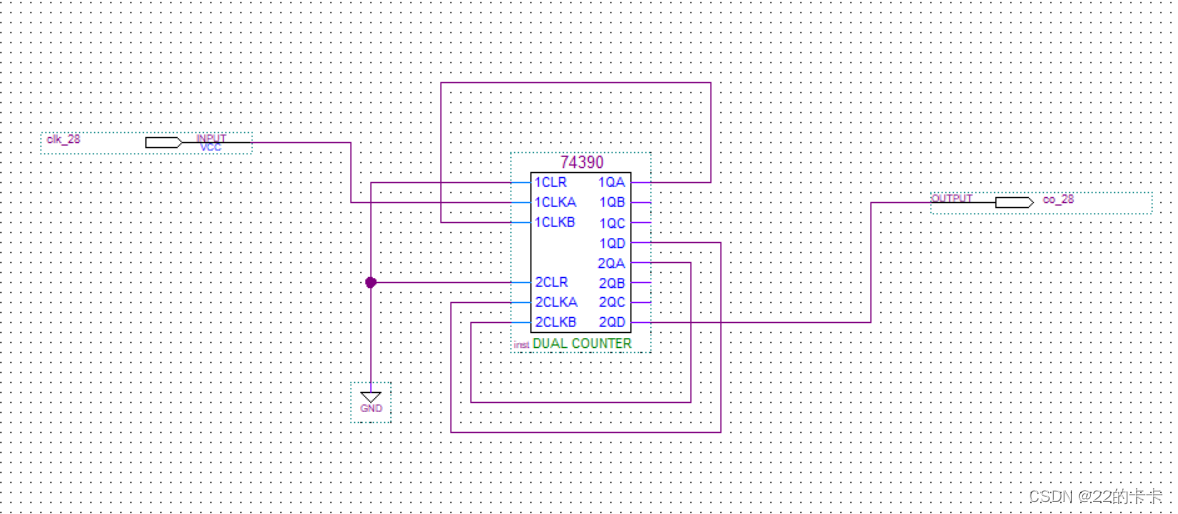

应用74LS160实现28进制计数器

参考资源链接:[54/74LS169:4位同步计数器详解与特性](https://wenku.csdn.net/doc/649643329aecc961cb3e1775?spm=1055.2635.3001.10343)

# 1. 74LS169与FPGA概述

在当今的电子设计领域,74LS169和FPGA都是不可或缺的组成部分,它们各具特点和应用范畴。74LS169,作为一种经典的4位二进制同步计数器,以其简单的接口和稳定的性能,在早期数字电路中扮演着重要的角色。而FPGA(现场可编程门阵列)则是一种可以通过编程来配置硬件逻辑的集成电路,其灵活性和高性能在现代电子设计中有着广泛的应用。

本章将概述74LS169计数器和FPGA的基本概念,以及它们在集成设计中的相互作用。我们将探讨74LS169的基本特性和在数字电路设计中的应用,同时介绍FPGA的基本工作原理和架构。这些知识为进一步深入理解它们的集成设计和实际应用案例打下坚实的基础。

# 2. 理解74LS169的原理和特性

### 2.1 74LS169的内部结构与工作原理

#### 2.1.1 74LS169的引脚功能与配置

74LS169是一种8位的同步二进制计数器,它支持向上计数和向下计数的操作模式。它的引脚功能丰富,可以满足不同的应用场景需求。

- **Vcc(Pin 16)和 GND(Pin 8)**:分别连接到正电源和地,为芯片提供电源和接地。

- **P0 - P3(Pin 1 - Pin 4)和 P4 - P7(Pin 13 - Pin 10)**:为8位并行输入端口,用于置数操作。

- **PE(Pin 5)**:是并行输入使能端,高电平时允许从P0到P7的输入。

- **PL(Pin 6)和 PH(Pin 7)**:分别是加载(Parallel Load)和清零(Preset High)控制端口,用于初始化计数器的值。

- **UP/DOWN(Pin 9)**:用于控制计数方向,高电平时为向上计数模式,低电平时为向下计数模式。

- **CLK(Pin 12)**:是时钟输入端,用于同步计数操作。

- **Q0 - Q3(Pin 14 - Pin 15, Pin 11 - Pin 10)**:是8位输出端口,用于显示当前计数值。

在配置74LS169时,设计师需要根据实际应用选择合适的引脚连接,例如将PE接高电平实现并行加载,或通过PL和PH实现即时的计数器初始化。

#### 2.1.2 计数模式与控制逻辑分析

74LS169可以配置为四种基本计数模式:

- **二进制向上计数**:当UP/DOWN接高电平,每个时钟上升沿计数器的计数值增加1。

- **二进制向下计数**:当UP/DOWN接低电平,每个时钟上升沿计数器的计数值减少1。

- **同步加载**:PE接高电平时,可通过P0-P7端口并行输入数据到计数器。

- **清零和置数**:PL接低电平时,计数器的计数值立即被置为P0-P7端口的数据;PH接低电平时,计数器的计数值被置为高电平。

控制逻辑方面,74LS169的控制逻辑非常直接:计数使能信号(如CLK的上升沿)被识别时,计数器才会进行计数或加载动作。此外,UP/DOWN引脚允许设计师在设计时根据需要选择计数的方向,这是实现各种计数需求的关键。

### 2.2 74LS169的功能特性与应用领域

#### 2.2.1 并行与串行输入输出特性

74LS169不仅仅支持并行输入输出,它也提供了串行数据处理的能力。并行特性允许快速加载初始值或者读取当前计数值,这是非常有用的功能,特别是在需要快速初始化计数器或者读取计数值的情况下。

串行特性则是通过两个串行输入/输出引脚实现,允许数据在多个计数器之间串行传输。设计师可以利用这一点,将多个74LS169计数器级联起来,形成更大的计数范围。对于串行输入,数据在时钟的上升沿从SI(串行输入)端口进入;对于串行输出,则可以从SO(串行输出)端口读取。

#### 2.2.2 在数字电路设计中的应用案例

74LS169在数字电路设计中应用广泛,它能用于构建频率分频器、计数器、定时器、状态机等数字系统组件。例如,在一个简单的频率分频器设计中,74LS169可用来生成方波或脉冲,实现频率的降低。设计者可以使用其计数功能来测量时间间隔,或者使用其计数功能来实现多路复用显示。

另一个应用案例是构建一个简单的数字计时器。通过74LS169的向上计数模式,可以轻松记录外部事件发生的次数。通过将多个计数器级联,可以扩展计数范围,以记录更多次数的事件。

### 表格

| 功能特性 | 描述 |

| -------------- | ------------------------------------------------------------ |

| 计数模式 | 支持二进制向上/向下计数 |

| 并行输入输出 | 通过P0-P7端口实现快速的并行加载和读取计数值 |

| 串行输入输出 | 支持数据在多个计数器之间的串行传输 |

| 清零和置数功能 | PL和PH引脚控制,实现计数器立即清零或置数到指定值 |

| 计数使能 | 通过UP/DOWN引脚控制计数方向,通过CLK实现计数器的同步操作 |

### Mermaid 流程图

```mermaid

graph LR

A[开始] --> B[配置引脚]

B --> C{设置计数模式}

C -->|向上计数| D[时钟上升沿计数值+1]

C -->|向下计数| E[时钟上升沿计数值-1]

C -->|并行加载| F[PE端置高电平,P0-P7设置值]

C -->|清零/置数| G[PL/PH端置低电平,加载值]

D --> H[当前计数值输出]

E --> H

F --> H

G --> H[计数器使用完成]

```

通过以上描述和图表,可以清晰地看到74LS169计数器的工作原理和应用案例。在实际应用中,设计者可以针对不同的需求,灵活运用其引脚配置和计数模式,实现各种数字电路的设计和创新。

# 3. FPGA技术的介绍与应用

## 3.1 FPGA的工作原理及架构概述

### 3.1.1 FPGA的可编程逻辑单元

FPGA(Field-Programmable Gate Array)是一种可以通过用户编程来配置的集成电路。它由大量可编程逻辑单元组成,这些单元通过可编程互连来连接。与传统集成电路不同的是,FPGA可以在制造之后进行配置,赋予其不同的逻辑功能。

可编程逻辑单元(CLB,Configurable Logic Block)是FPGA的基本构建块,通常包含查找表(LUTs)、触发器和专用逻辑。查找表可用于实现任意的布尔函数,触发器用于数据存储,而专用逻辑则可以执行如快速加法等特定功能。

```verilog

// 示例:简单的FPGA逻辑单元描述(伪代码)

// 假设每个LUT可以实现一个4输入1输出的布尔函数

module LUT_4to1(input a, b, c, d, output f);

// 这里会定义一个查找表实现具体的逻辑功能

assign f = /* 基于 a, b, c, d 的逻辑组合

```

0

0