数字电路设计自动化:74LS169的仿真技术与参数化建模指南

发布时间: 2024-12-13 21:50:45 阅读量: 5 订阅数: 11

北京理工大学自动化类计算机控制系统大作业

参考资源链接:[54/74LS169:4位同步计数器详解与特性](https://wenku.csdn.net/doc/649643329aecc961cb3e1775?spm=1055.2635.3001.10343)

# 1. 数字电路设计自动化的基础

## 1.1 自动化设计的重要性

随着技术的不断进步,数字电路的设计复杂度呈指数级增长。自动化设计成为了设计高效、准确、可维护电路的必要手段。通过软件工具来辅助电路设计,不仅可以大幅缩短设计周期,还可以减少人为错误,提高设计质量。

## 1.2 设计流程的演变

从最初的原理图绘制到使用硬件描述语言(HDL)进行模块化设计,再到如今的综合工具和仿真软件的广泛应用,数字电路设计的流程经历了巨大的变革。自动化工具使得从设计验证到最终生成可编程逻辑设备的代码变得越来越便捷。

## 1.3 自动化设计工具的类型

数字电路设计自动化工具主要包括仿真工具、综合工具、布局布线工具等。这些工具通过辅助设计、优化电路性能、验证电路功能,极大地提升了设计的准确性和效率。例如,仿真工具允许设计师在实际制作电路板前,先在软件环境中测试电路设计的正确性。

## 1.4 自动化设计的未来趋势

随着人工智能和机器学习技术的发展,未来的自动化设计工具将进一步智能化。例如,自适应算法可以帮助设计师优化电路设计,减少资源消耗,并提高电路运行的可靠性。自动化工具的集成和互操作性也将进一步增强,从而为数字电路设计带来一场革命。

# 2. 74LS169计数器概述

## 74LS169基础信息

### 引言

74LS169是一种由74系列逻辑门电路构成的4位同步二进制计数器。它在数字系统设计中扮演着重要的角色,尤其在需要执行计数功能的场合中。其具备同步加载、可逆计数和清零功能,以及使能控制信号,为多种应用场景提供灵活性。在深入分析74LS169计数器的应用之前,先了解它的基本原理和结构是至关重要的。

### 功能特性

74LS169计数器的主要功能特性如下:

- **4位二进制计数**:最多可计数至十六进制的“F”,即十进制的15。

- **计数模式**:可配置为向上或向下计数。

- **同步加载**:允许并行加载一个初始值进入计数器。

- **异步清零**:可以将计数器的所有位同时置零。

- **使能端控制**:带有两个使能端,以便于控制计数器的工作状态。

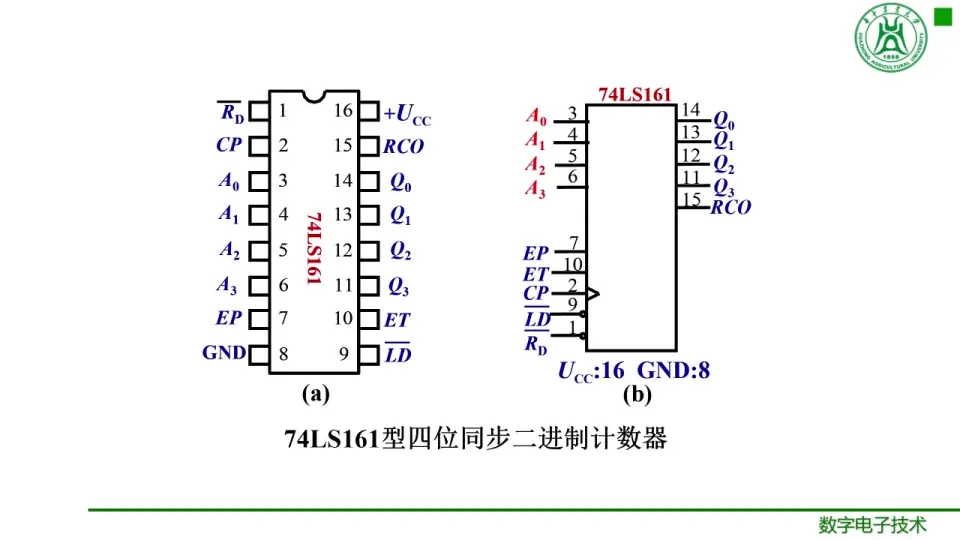

### 引脚布局

74LS169的引脚布局对应用至关重要,它定义了计数器如何与外部电路连接。计数器的引脚功能如下:

1. **A0 - A3**:四个数据输入引脚,用于并行加载初始值。

2. **LOAD**:当此引脚被置为高电平,A0-A3的数据将会被加载进计数器。

3. **UP/DOWN**:控制计数方向的输入,高电平时向上计数,低电平时向下计数。

4. **CLR**:异步清零引脚,置为低电平时会清除计数器的所有位,即计数器输出为零。

5. **CET** 和 **CEP**:这两个引脚是使能端,分别控制计数器的计数使能和并行数据加载使能。

6. **Q0 - Q3**:输出引脚,提供计数器当前的状态。

## 74LS169的工作原理

### 计数模式

在计数模式下,每来一个上升沿,计数器的输出就会按照设定的计数方向改变。如果设置了向上计数(UP/DOWN引脚为高电平),那么每个时钟脉冲到来时,计数器会从当前值加1;如果设置了向下计数(UP/DOWN引脚为低电平),则每个时钟脉冲会使计数器的值减1。

### 同步加载功能

当LOAD引脚为高电平,并且使能端同时满足条件时,计数器可以将A0-A3端口的数据同步加载到输出端。这一功能用于快速设置计数器的初始状态。

### 异步清零

CLR引脚能够进行异步清零,这意味着不论计数器当前的状态如何,一旦CLR被置为低电平,计数器的所有输出立即被清零。

### 使能控制

CET(计数使能传输)和CEP(并行数据加载使能)是使能控制端口,它们需要被激活(置为低电平)以便使计数器开始计数或者并行加载数据。

## 应用场景

74LS169在多种数字逻辑设计中都有广泛应用,例如:

- **计数器设计**:用于需要计数功能的数字系统。

- **定时器设计**:通过与时钟信号配合,实现定时功能。

- **地址生成**:在内存系统中作为地址计数器,用于指向下一条将要读取或写入的数据地址。

- **分频器**:通过计数功能实现对时钟信号的分频处理。

## 设计考虑因素

在设计含有74LS169计数器的电路时,需要注意以下几点:

- **同步设计**:确保所有控制信号都是同步的,避免因异步操作产生不可预期的计数误差。

- **使能端的逻辑设计**:正确设计使能逻辑,确保计数器按照预期工作。

- **负载电阻选择**:为了保证输出信号的质量,应选择适当的上拉或下拉电阻。

## 总结

通过本章节的介绍,我们初步了解了74LS169计数器的基础知识,包括其功能特性、工作原理和应用场景。为了更好地利用这一计数器,下一章将探讨其在仿真技术中的应用,进一步提升我们对其性能的理解和运用。

```mermaid

graph LR

A[开始] --> B[介绍74LS169]

B --> C[功能特性]

C --> D[引脚布局]

D --> E[工作原理]

E --> F[应用场景]

F --> G[设计考虑]

G --> H[总结]

```

下面的表格提供了74LS169计数器引脚功能的快速参考:

| 引脚 | 名称 | 描述 |

|------|------|------|

| 1 | CLR | 异步清零端 |

| 2 | Q0 | 计数器位0输出 |

| 3 | Q1 | 计数器位1输出 |

| 4 | Q2 | 计数器位2输出 |

| 5 | Q3 | 计数器位3输出 |

| 6 | GND | 接地端 |

| 7 | CEP | 计数使能端 |

| 8 | CET | 并行数据加载使能端 |

| 9 | LOAD | 同步加载端 |

| 10 | UP/DOWN | 计数方向控制端 |

| 11 | CP | 时钟输入端 |

| 12 | A0 | 并行数据输入端 |

| 13 | A1 | 并行数据输入端 |

| 14 | A2 | 并行数据输入端 |

| 15 | A3 | 并行数据输入端 |

| 16 | Vcc | 电源端 |

在下一章节中,我们将深入了解如何在数字电路设计中运用仿真技术来模拟74LS169计数器的行为。

# 3. 仿真技术在74LS169中的应用

## 3.1 理解74LS169计数器工作原理

74LS169 是一款4位同步二进制计数器,常用于数字电路设计中实现计数功能。它包含一个4位的二进制计数器和一个同步清零输入。该计数器在时钟脉冲的上升沿进行计数,从0000开始,一直计数到1111。当计数器达到最大值后,下一个上升沿会使计数器回到0000,实现循环计数。

### 3.1.1 计数器的时序分析

在进行仿真之前,我们需要了解74LS169的时序特性。同步计数器的特点是所有位同时在时钟信号的触发下改变状态。在74LS169中,还提供了使能端(Enable)和负载端(Load),可以通过逻辑电平来控制计数器的计数行为。

### 3.1.2 计数器的功能测试

在仿真过程中,将通过设置不同的输入组合来测试计数器的各种功能。例如,将使能端保持高电平,负载端保持低电平,观察时钟信号对计数器计数的影响。另外,模拟使能端或负载端的高电平信号,观察计数器是否按预期停止计数或加载预设值。

## 3.2 仿真环境的搭建

仿真技术可以帮助设计者在实际制作电路板之前,验证电路设计的正确性。搭建仿真环境需要选

0

0