SW3518S芯片硬件设计要点:专业建议助您优化PCB布局

发布时间: 2025-01-07 18:22:17 阅读量: 30 订阅数: 12

SW3518 & SW3518S 方案(包含PCB,原理图,BOM等全套资料).rar

# 摘要

本文深入探讨了SW3518S芯片在电子设计中的关键角色,从其硬件设计基础到高级应用和挑战。文章首先概述了SW3518S芯片的基本特性及其在设计中的重要地位,紧接着详细阐述了PCB设计的基础理论,包括信号完整性、电源分布网络、以及高频电路布局对性能的影响。此外,本文还介绍了SW3518S芯片PCB布局的实践技巧,特别是在关键信号布局、EMI防护和热管理方面的策略。通过对设计案例的分析和常见错误的剖析,文章提供了针对信号与电源完整性的诊断和解决方法,并提出了设计优化的建议和最佳实践。最后,文章展望了SW3518S芯片在多芯片系统和高性能计算中的应用前景及其未来的技术发展趋势,旨在为芯片设计提供全面的指导和展望。

# 关键字

SW3518S芯片;硬件设计;PCB布局;信号完整性;电源分布网络;热管理;电磁干扰(EMI)

参考资源链接:[SW3518:高集成度PD多快充协议双口充电芯片](https://wenku.csdn.net/doc/2mgcsbz7mh?spm=1055.2635.3001.10343)

# 1. SW3518S芯片概述及其在设计中的地位

SW3518S芯片作为现代电子设计中不可或缺的核心元件,它在系统设计中的重要性不言而喻。作为一款集成了多种功能和接口的高性能系统芯片,SW3518S在硬件设计、信号处理以及与外部设备的交互方面发挥着关键作用。本章节将对SW3518S芯片进行概述,简要介绍其在电子产品设计中的地位及其背后的工程考量。

## 1.1 SW3518S芯片的市场定位与应用范围

SW3518S芯片针对的市场定位主要是工业级和商业级应用,适用于多种电子系统,如通信设备、车载信息娱乐系统、网络设备及智能家居控制等。凭借其高性能的处理能力和丰富的接口选择,SW3518S能够满足在不同领域中对复杂数据处理和高效控制的需求。

## 1.2 SW3518S芯片的设计理念与创新点

在设计理念上,SW3518S着重于集成化与功能多样性的平衡,通过创新的微架构设计和先进的制程技术,实现了低功耗与高性能的双重目标。它的创新点主要体现在多核处理器核心、高速内存接口以及对最新通信协议的支持上,使其在现代电子设计中具有广阔的应用前景。

本章节内容为SW3518S芯片的概览,下文将继续深入探讨其在硬件设计中的基础细节。

# 2. SW3518S芯片的硬件设计基础

## 2.1 SW3518S芯片的基本特性

### 2.1.1 芯片架构与功能简述

SW3518S芯片采用了先进的微处理器架构,结合了高性能的CPU核心与丰富的外设接口,提供了极高的集成度和强大的处理能力。其架构设计旨在满足现代电子设备对高速数据处理和复杂算法实现的需求。芯片内包含的专用硬件加速器和高带宽的内存接口,能够支撑多任务并行处理,保证系统在运行大量应用程序时的稳定性和流畅性。

### 2.1.2 电源和信号接口的特性

SW3518S芯片的电源设计要求严格,提供多路电源输入以支持不同的功耗模式。每个电源引脚都有明确的电流限制和上电时序要求,保证芯片在各种工作状态下的稳定运行。同时,芯片的信号接口包括高速串行接口、并行接口、模拟输入/输出等,每种接口都有其特定的电气特性,设计时需要考虑信号的质量、完整性以及兼容性问题。

## 2.2 PCB设计的基本理论

### 2.2.1 信号完整性基础

信号完整性(SI)是高速电路设计中的核心问题之一,主要关注信号在传输过程中的质量,包括信号的上升/下降时间、反射、串扰、时钟抖动等。设计中必须确保信号的完整性,避免因为信号失真导致的系统不稳定或性能下降。PCB布线时应尽量减少信号路径长度,增加信号线与参考平面的距离,以减少串扰和电磁干扰(EMI)。

### 2.2.2 电源完整性与电源分布网络(PDN)

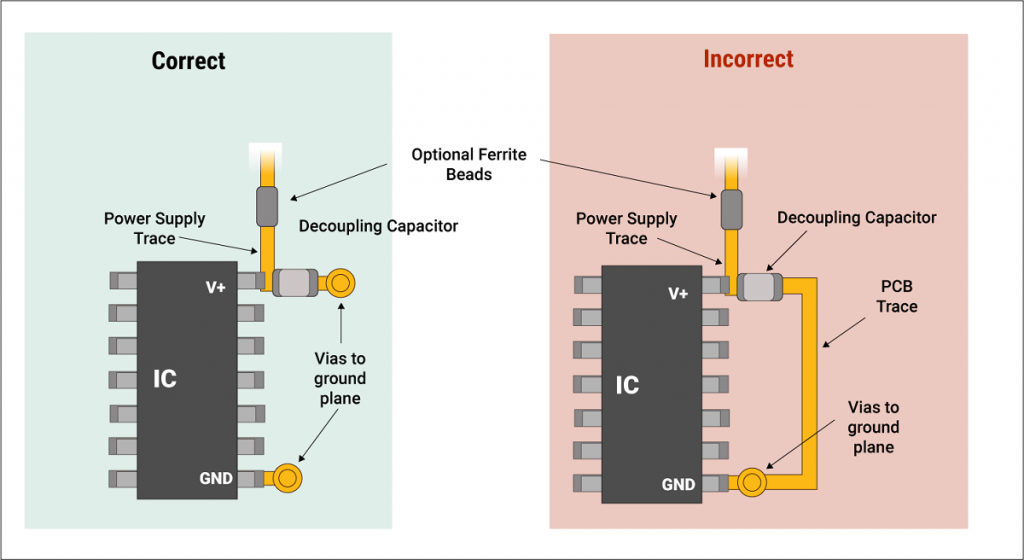

电源完整性(PI)关注的是电源在提供给芯片使用时的稳定性。良好的电源分布网络(Power Delivery Network, PDN)设计可以降低电源噪声和电压波动,从而确保芯片获得稳定的电源供应。为了设计有效的PDN,需要对整个电源平面进行细致的规划,包括电源层的布局、去耦电容的配置,以及必要的电源管理策略。

### 2.2.3 高频电路布局对性能的影响

高频电路布局要求十分严格,因为高频信号容易受到布局不当的影响而产生不必要的辐射和耦合。为了保证高频电路的性能,设计者应尽量缩短信号走线,减少回路面积,合理安排高速信号与敏感信号的相对位置,避免信号线的平行长度过长,使用地平面层作为信号回流路径等。这些措施有助于维持信号的完整性和降低电磁干扰。

## 2.3 SW3518S芯片的引脚配置及要求

### 2.3.1 引脚分布与关键信号描述

SW3518S芯片的引脚配置较为复杂,设计者需要根据芯片手册提供的引脚图和描述,仔细规划每个引脚的功能和位置。关键信号,如时钟信号、复位信号、电源和地线,需要靠近芯片的核心区域布局,以降低噪声干扰和确保信号传输的及时性。同时,高速信号的引脚应避免与模拟信号引脚相邻,以防止交叉干扰。

### 2.3.2 引脚保护与布局指导原则

引脚保护是指在布局阶段考虑如何避免静电放电(ESD)和电磁脉冲(EMP)等外界因素对芯片造成的潜在损害。为此,布局时应在关键信号引脚上设置适当的防护元件,并合理布置去耦电容,以过滤高频噪声并提供稳定的电源。此外,应遵循布局指导原则,如尽量减少过孔使用、避免长距离走线、保持信号线与参考平面的耦合等,确保布局的可靠性与稳定性。

# 3. SW3518S芯片PCB布局的实践技巧

## 3.1 关键信号的布局策略

### 3.1.1 时钟信号的布局

在设计SW3518S芯片的PCB布局时,时钟信号(Clock Signal)的布局对系统性能有着决定性的影响。时钟信号的品质直接关系到数据传输的准确性和系统的稳定性。在布线过程中,以下几个要点需要特别关注:

- **短而直**:为了减少时钟信号的传输损耗和信号反射,时钟线路应尽量短和直,避免长距离的线路和不必要的过孔。

- **阻抗匹配**:设计时钟线路时,阻抗匹配是关键。确保源端和负载端的阻抗一致,可以有效避免信号反射问题。

- **远离干扰源**:时钟信号极易受到干扰,因此要远离高速开关信号、功率线路以及可能产生噪声的区域。

**代码块与逻辑分析:**

```pcb

[CLK_TRACE_LENGT

```

0

0