【扩展I_O能力】:Quartus II与外部设备接口的完美对接

发布时间: 2025-01-04 03:18:24 阅读量: 7 订阅数: 9

fifo.zip_FPGA verilog_quartus_quartus II _site:en.pudn.com_south

# 摘要

本文详细介绍了Quartus II软件在FPGA开发中的I/O设计和外部通信协议的应用。首先概述了Quartus II的基本功能及其I/O基础知识,然后深入探讨了与外部设备通信所涉及的串行和并行协议,包括RS-232/RS-485、USB、PCIe和HDMI等现代接口标准。第三章侧重于实际的I/O设计实践,包括引脚分配、接口代码编写和驱动集成。第四章讲述了高级交互,包括自定义协议栈实现、接口性能优化和硬件加速技术。第五章专注于Quartus II在物联网领域中的应用,特别关注I/O接口需求和通信解决方案的创建,以及如何提升系统的安全性和可靠性。最后一章通过案例研究和未来展望,揭示了Quartus II在现有项目中的运用以及未来技术趋势。本文对FPGA设计人员提供了全面的指导,旨在提升他们利用Quartus II进行高效、安全和可靠设计的能力。

# 关键字

Quartus II;I/O设计;通信协议;硬件加速;物联网;接口标准

参考资源链接:[Quartus Ⅱ软件在16位CPU FPGA/CPLD设计中的应用](https://wenku.csdn.net/doc/6461ef91543f84448895b258?spm=1055.2635.3001.10343)

# 1. Quartus II概述与I/O基础知识

## 1.1 Quartus II概述

Quartus II是由Altera公司开发的集成设计环境,广泛应用于复杂可编程逻辑设备(CPLD)和现场可编程门阵列(FPGA)的编程和配置。Quartus II支持从设计输入到硬件配置的整个工程流程,提供图形化界面和脚本自动化,是业界主流的FPGA开发工具之一。

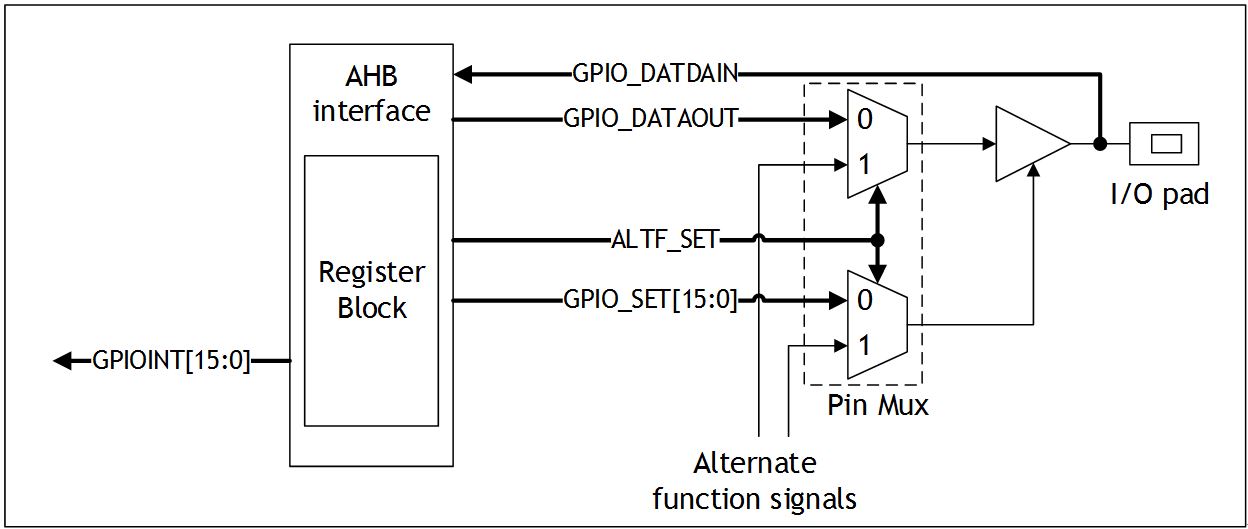

## 1.2 I/O基础知识

在FPGA设计中,I/O接口是外部设备与芯片之间数据交换的通道。了解I/O接口的设计对于确保数据的正确读取和输出至关重要。I/O引脚可以配置为输入、输出或双向模式,并且可以设置特定的电平标准和驱动能力,以满足不同电路的要求。在Quartus II中,I/O设计需遵循芯片的电气特性和封装限制,并利用其提供的各种工具来进行精确控制。

# 2. Quartus II与外部设备的通信协议

在第二章中,我们将深入了解Quartus II与外部设备之间的通信协议。这一章节将涵盖从基础的串行通信到复杂的自定义协议栈,以及Quartus II如何通过高级交互来优化I/O接口性能。本章将分为三个主要的二级章节,每个章节都将深入探讨其主题,提供丰富的技术细节和应用案例。

## 2.1 串行通信协议基础

串行通信是信息在设备间以逐位传输的方式。由于其简单性和适用性广泛,在嵌入式系统和FPGA设计中得到了广泛应用。本节将探讨串行通信协议的类型和标准,并对RS-232和RS-485进行详细分析。

### 2.1.1 串行通信的类型和标准

串行通信可以分为同步和异步两大类。同步通信需要一个外部或内部的时钟信号来同步数据传输,而异步通信则通过在数据流中嵌入起始和停止位来实现同步。常见的串行通信标准包括RS-232、RS-485、I2C和SPI。

RS-232是一种较早的串行通信标准,它支持点对点的连接,传输速率通常不超过20kbps。RS-485则是RS-232的多点版本,它支持一主多从的通信模式,并且能够提供更远距离的数据传输。这使得RS-485在工业控制系统中广泛使用。

### 2.1.2 RS-232/RS-485协议详解

RS-232是早期的串行通信标准,它规定了电气特性、传输速率、数据位、停止位和校验位等。RS-232的电平使用正负电压表示逻辑1和0,这与现代的TTL电平相反,因此在使用时可能需要电平转换器。

RS-485,也称为TIA-485或EIA-485,它支持高速的多点数据传输。RS-485采用差分信号传输,提高了信号的抗干扰能力,能够有效支持长达1200米的传输距离。RS-485还支持全双工通信,并且在数据通信时允许多个驱动器和接收器共存于同一条总线上。

在Quartus II中,可以通过配置FPGA的GPIO引脚来实现对RS-232和RS-485协议的支持。以下是一个简单的Verilog代码示例,用于配置UART(通用异步收发传输器),这可以用来实现RS-232标准的串行通信:

```verilog

module uart(

input clk, // 时钟信号

input rst, // 复位信号

input [7:0] data_in, // 8位数据输入

input tx_start, // 开始发送信号

output reg tx, // UART发送线

// 其他信号线...

);

// 参数定义、状态机逻辑、波特率生成器等代码逻辑

endmodule

```

在该代码中,我们定义了一个简单的UART模块,该模块在接收到开始发送信号时,通过tx线发送数据。在实现RS-485通信时,通常需要使用专用的收发器芯片,如MAX485,来实现电平转换和半双工通信。

## 2.2 并行通信的原理与应用

并行通信是指数据的各个位同时在多条数据线上传输。与串行通信相比,它能提供更高的数据传输速率,但同时也会增加线路的复杂度和成本。

### 2.2.1 并行数据传输的特点

并行传输通常用于短距离和高速数据传输,如计算机内部的并行端口和FPGA内部的数据交换。并行传输的主要缺点是线路上的时序问题,随着传输距离的增加或传输速度的提高,信号可能会出现延迟和扭曲。

### 2.2.2 并行接口协议及其实现

并行接口有多种类型,比如LPT(并行端口)、PCMCIA等。在FPGA设计中,可以使用GPIO引脚来实现自定义的并行接口。在设计时需要注意信号的同步问题,通常使用锁存器、触发器和同步器来确保数据的一致性和稳定性。

为了实现并行通信,FPGA需要提供足够的I/O引脚以及相应的接口逻辑。以下是一个简单的Verilog代码示例,用于实现一个简单的并行接口:

```verilog

module parallel_interface(

input clk, // 时钟信号

input [7:0] data_in, // 8位数据输入

output reg [7:0] data_out, // 8位数据输出

output reg write_enable // 写使能信号

// 其他信号线...

);

// 并行数据传输控制逻辑

endmodule

```

在该模块中,我们定义了一个简单的并行接口。根据具体应用需求,可以通过编写相应的控制逻辑来处理数据的接收和发送。

## 2.3 现代接口标准与Quartus II的兼容性

随着技术的发展,新的通信协议如USB、PCIe和HDMI等成为主流。这些现代接口标准提供了更高的数据传输速率和更复杂的协议栈。FPGA和Quartus II如何与这些接口标准兼容,成为工程师们关注的焦点。

### 2.3.1 USB、PCIe和HDMI接口标准

USB(通用串行总线)是一种广泛使用的串行总线标准,它支持热插拔和即插即用功能。PCIe(外设组件互连快速版)是一种高速串行计算机扩展总线标准,常用于连接主板和扩展卡。HDMI(高清晰度多媒体接口)是一种全数字视频和音频传输接口。

这些接口标准有着复杂的协议实现和电气要求,因此通常会有专用的IP核来在FPGA中实现这些标准。在Quartus II中,Intel提供了一系列的IP核,这些IP核可以通过图形化界面来配置和实现相应的通信协议。

### 2.3.2 Quartus II对现代接口的支持与限制

Quartus II提供了丰富的IP核,使得FPGA设计工程师可以轻松地在设计中集成USB、PCIe和HDMI等现代接口。通过使用这些IP核,可以大大减少设计的复杂度和开发周期。

在使用这些高级接口时,FPGA的性能和资源占用也成为了限制因素。高性能的FPGA,如Intel Stratix系列,提供了更多的逻辑单元和存储资源,更适合实现复杂的现代接口标准。同时,设计者也需要考虑时钟管理、信号完整性、热管理等多方面的因素。

通过上述内容,我们可以看到Quartus II在处理与外部设备通信协议方面的能力。它不仅支持传统的串行和并行通信,也能与现代接口标准进行有效的集成。本章所涉及的基础知识和实践技能,将为后续章节中更加深入的I/O设计实践提供坚实的基础。在下一章中,我

0

0