【功耗分析大师】:实现节能型16位CPU的设计技巧

发布时间: 2025-01-04 03:10:03 阅读量: 11 订阅数: 19

# 摘要

随着计算需求的日益增长,节能型16位CPU的设计变得至关重要。本文从CPU功耗理论基础出发,详细探讨了功耗的来源、组成以及优化理论模型,包括电源门控技术、多阈值CMOS技术与动态电压频率调节(DVFS)等策略。同时,对热设计功耗(TDP)及其与系统散热设计的关系进行了阐述。在设计实践中,重点分析了低功耗架构设计、电源管理策略和热管理技术。为达到性能与功耗的平衡,本文还介绍了性能分析工具、功耗测试方法以及平衡两者的调优策略。通过案例研究,本文展示了节能型CPU设计的实际应用和成功案例,并对未来技术发展趋势进行了展望。最后,文章总结研究成果,并提出了面向未来的建议和行业对策。

# 关键字

节能型CPU;功耗优化;电源门控;动态电压频率调节;热设计功耗;性能与功耗平衡

参考资源链接:[Quartus Ⅱ软件在16位CPU FPGA/CPLD设计中的应用](https://wenku.csdn.net/doc/6461ef91543f84448895b258?spm=1055.2635.3001.10343)

# 1. 节能型16位CPU概述

在当今数字时代,随着物联网、移动计算和大数据的不断发展,对电子设备的能源效率提出了更高要求。CPU作为设备的核心部件,其功耗问题受到了广泛关注。本章将介绍节能型16位CPU的基本概念和重要性,并概述其在未来技术中的关键作用。

## 1.1 CPU在现代技术中的地位

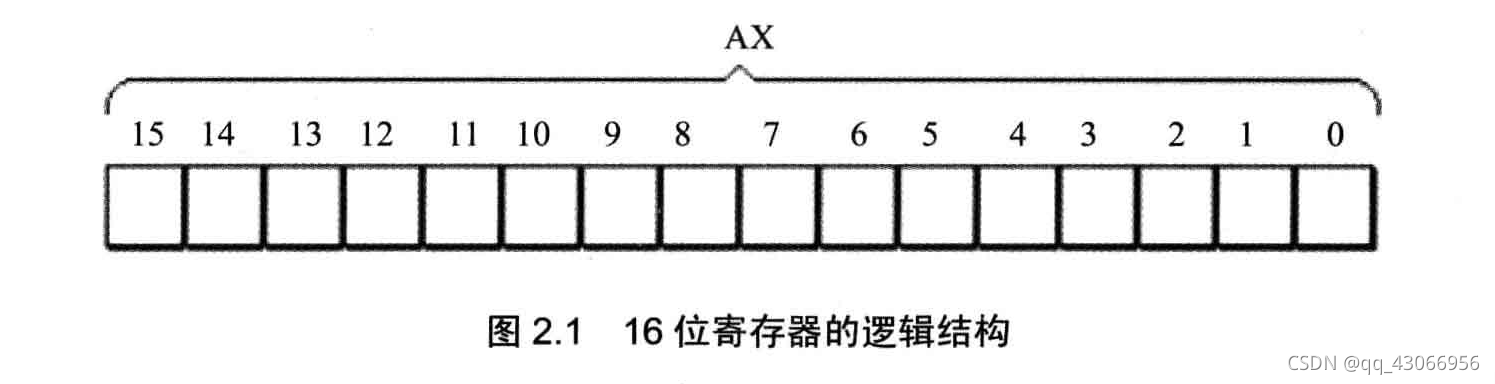

CPU,即中央处理单元,是任何计算设备的“大脑”。16位CPU相较于32位或64位,通常具有更低的能耗和成本,同时适用于那些对计算能力要求不是特别高的场合。它们广泛应用于嵌入式系统、微控制器和各种IoT设备。

## 1.2 节能型CPU的优势

节能型CPU的优势在于其低功耗设计,这不仅延长了电池寿命,降低了能源消耗,还有助于减少电子设备运行时产生的热量,从而降低冷却成本。随着技术的进步,这些CPU在保持性能的同时,正变得更加高效。

## 1.3 节能型CPU的设计挑战

尽管节能型CPU有诸多优势,但在设计过程中,工程师需要在性能、功耗和成本之间取得平衡。设计人员必须考虑电路优化、电源管理和热设计等方面,以确保CPU在不牺牲性能的前提下实现能效最优化。

在这一章节中,我们已经对节能型16位CPU有一个初步的了解,为后文的深入探讨奠定了基础。接下来,我们将深入探讨CPU功耗的理论基础,以及如何通过不同的技术手段实现功耗优化。

# 2. CPU功耗理论基础

### 2.1 功耗的组成与来源

#### 2.1.1 静态功耗与动态功耗的区别

在分析CPU的功耗时,我们需要理解两个基本概念:静态功耗(Static Power Dissipation)和动态功耗(Dynamic Power Dissipation)。静态功耗,又称为漏电流功耗,是在电路不工作时仍然消耗的功率,主要由于晶体管的漏电流所引起。随着半导体工艺的进步,晶体管尺寸越来越小,漏电流问题变得越来越严重,静态功耗也相应增加。

另一方面,动态功耗发生在晶体管开启和关闭的过程中,主要是因为电容充放电造成的。它与CPU的工作频率、电压以及电路的负载电容成正比。随着性能需求的提升,动态功耗一直是研究和设计的重点领域。

在具体设计时,静态功耗的降低往往依赖于工艺上的改进,比如使用高阈值电压晶体管和优化晶体管的物理结构。而动态功耗的优化则更注重电路设计和电源管理策略。

```mermaid

graph LR

A[静态功耗] --> B[漏电流]

A --> C[晶体管尺寸]

D[动态功耗] --> E[电容充放电]

D --> F[工作频率]

D --> G[电压]

D --> H[负载电容]

```

#### 2.1.2 功耗来源的深入分析

进一步深入分析,CPU功耗的来源可以分为几个部分:逻辑单元功耗、时钟树功耗、输入输出(I/O)功耗和存储器功耗。逻辑单元功耗是CPU内部运算逻辑单元在处理数据时产生的功耗。时钟树功耗是由于时钟信号分布网络中存在电容充放电所导致的。I/O功耗涉及到CPU与外部设备的数据交换,存储器功耗则源于缓存和主存的读写操作。

在16位CPU中,由于处理单元和存储器相对较小,整体功耗相比现代处理器要低。但是,设计者仍然需要仔细考虑如何降低各个部分的功耗,尤其是在静态功耗占比逐渐上升的背景下。

### 2.2 功耗优化理论模型

#### 2.2.1 电源门控技术原理

电源门控技术是降低静态功耗的一种重要手段。基本原理是在不工作的时候,切断逻辑电路的电源,从而避免漏电流产生功耗。这项技术通常通过在电路中添加一系列的开关来实现,这些开关在电路活动时导通,在非活动时关闭。

电源门控技术不仅仅是一种简单的开关,它还需要考虑到信号完整性和恢复时间,因为电路在重新供电时可能会有短暂的不稳定状态。设计时,需要权衡开关的数量和位置,以优化功耗与性能之间的平衡。

```mermaid

graph LR

A[电源门控技术] --> B[开关控制]

A --> C[信号完整性]

A --> D[性能优化]

```

#### 2.2.2 多阈值CMOS技术

多阈值CMOS(Multi-Threshold CMOS, MTCMOS)技术是一种将不同阈值电压的晶体管结合在同一芯片中的方法。通过使用高阈值电压晶体管来降低静态功耗,低阈值电压晶体管提高开关速度,这种技术可以同时在性能和功耗上达到优化。MTCMOS技术的关键在于合理地安排高阈值和低阈值晶体管的使用,以最大限度地减少功耗,同时保持处理速度。

#### 2.2.3 动态电压频率调节(DVFS)

动态电压频率调节(Dynamic Voltage and Frequency Scaling, DVFS)是一种通过动态调整CPU的工作电压和频率来优化功耗的技术。DVFS的核心思想是在满足当前工作负载的情况下,尽可能降低电压和频率,从而减少功耗。例如,在CPU负载较轻时,可以降低工作频率和电压,而在CPU负载较重时,则提高电压和频率。

DVFS技术的应用需要精确的功耗监测和智能的控制策略,以避免因为错误的电压调整导致系统不稳定。在实际应用中,DVFS策略通常结合CPU的性能监控单元(PMU)进行,根据实时的性能数据做出快速响应。

```mermaid

graph LR

A[DVFS技术] --> B[性能监控单元PMU]

A --> C[实时功耗监测]

A --> D[动态电压调整]

A --> E[动态频率调整]

```

### 2.3 热设计功耗(TDP)概念

#### 2.3.1 TDP的定义与计算方法

热设计功耗(Thermal Design Power, TDP)是CPU制造商提供的一项参数,它表示在特定条件下(通常是最大频率和电压下),处理器的最大散热功率。TDP的计算需要考虑CPU在运行时各个部分的功耗,包括核心逻辑、缓存、内存控制器和I/O等。TDP对于系统散热设计至关重要,因为散热器的尺寸和风扇的功率选择都与TDP密切相关。

在实际计算TDP时,需要通过实验测量不同工作条件下的功耗,然后通过公式和模型来估计在最坏情况下的功耗值。TDP的估计不是简单的相加,而是需要考虑到各部分之间的相互作用和影响。

#### 2.3.2 TDP与系统散热设计的关系

TDP为系统散

0

0